# Outphasing Class-E Power Amplifiers: From Theory to Back-off Efficiency Improvement

Ali Ghahremani, Student Member, IEEE, Anne-Johan Annema, Member, IEEE and Bram Nauta, Fellow, IEEE

Abstract—This paper presents an analysis of outphasing class-E Power Amplifiers (OEPAs), using load-pull analyses of single class-E PAs. This analysis is subsequently used to rotate and shift power contours and rotate the efficiency contours to improve the efficiency of OEPAs at deep power back-off, to improve the Output Power Dynamic Range (OPDR) and to reduce switch voltage stress. To validate the theory a 65nm CMOS prototype, using a pcb transmission-line based power combiner was implemented. The OEPA provides +20.1dBm output power from VDD=1.25V at 1.8GHz with more than 65% Drain Efficiency (DE) and 60% Power Added Efficiency (PAE). The presented technique enables more than 49dB OPDR and 37% DE and 22% PAE at 12dB back-off with reduced switch voltage stress.

Index Terms—Class-E, outphasing power amplifier, power contours, efficiency contours, reliability, power back-off efficiency.

#### I. INTRODUCTION

OWADAYS, modern communication systems necessitate complex modulated signals (e.g. OFDM and 64QAM) with high peak to average power ratios (PAPRs). The demands on the power amplifier (PA) in these systems are manifold: the PA mainly works in back-off, must be sufficiently robust and must have sufficiently high efficiency.

Among the various classes of PAs, class-E PAs are of great interest. Zero Voltage Switching (ZVS) and Zero Slope Switching (ZSS) conditions for the switch waveform in class-E PAs result in non-overlapping voltages and currents for the switch and hence yield high efficiency (ideally 100%) [1]. Due to switch-mode operation, a single class-E with constant supply voltage only allows phase modulation or On-Off Keying (OOK) modulation. Supply modulation through Envelope Elimination and Restoration (EER) [2] or load modulation through outphasing [3] is necessary to also enable amplitude modulation.

Outphasing class-E PAs (OEPAs) are getting more popular. Their performance is weakly dependent on process variations due to the switch-mode operation of the branch amplifiers [4]. Other advantages of OEPAs include maintaining high efficiency at a relatively wide output power back-off range and digital compatibility due to the phase-only control [5].

However, some issues with OEPAs need to be addressed. Firstly, the maximum voltage of the switches can be very high [6], [7]. Being implemented by transistors, there is a trade off between switch performance (e.g. on-resistance, drive power, speed) and reliability (e.g. life time) which makes

Ali Ghahremani, Anne-Johan Annema and Bram Nauta are with the Department of Electrical Engineering and Computer Science, University of Twente, Enschede, The Netherlands.

the design of class-E PAs challenging [8]. Secondly, high order modulated signals require a high Output Power Dynamic Range (OPDR). However, mismatch between the two paths in outphasing system limits the OPDR. Thirdly, OPEAs require power combiners. For high efficiency at power back-off non-isolating power combiners are used [9]. This results in load-pulling between the two branch amplifiers yielding the ZVS and ZSS conditions to be violated and consequently dropping the efficiency well below it's maximum (ideal) 100% [10].

Recently some papers reported on improving the efficiency of OEPAs in power back-off. In [10], variable duty cycle combined with variable drain capacitance and with a tunable load network were used to maintain ZVS and ZSS conditions in power back-off up to (ideally) 9dB back-off. The CMOS implementation of the technique, presented in [10], was employed in [11] at 1.85GHz. For higher than (ideally) 9dB back-off levels, the outphasing technique employed in [10], [11] resulted in a reduction of the efficiency due to non-zero switching losses (non-ZVS condition). Due to practical limitations on the minimum feasible duty cycle at high frequencies in [11], the ZVS and ZSS conditions were satisfied for 6dB of back-off range which yielding lower than 10% Power Added Efficiency (PAE) at 10dB back-off. Furthermore, amplitude errors limited the OPDR to 30dB in [10]. In [12] an isolating power combiner was used and supply voltage switching was implemented to maintain high efficiency at power back-off. However, this latter technique requires a highly efficient DC-DC converter not to compromise the overall efficiency of the OEPAs. Non-isolating package-integrated transformer based power combiners with Chireix compensation elements along with cleverly chosen class-E PA design parameters (denoted as load-insensitive class-E PA) was introduced in [5]. This loadinsensitive class-E design concept provides 100\% efficiency only for ohmic loads while Chireix compensation elements null the imaginary parts of the branch PA loads at (typically) only two power back-off levels. However, for higher back-off levels, OEPA efficiency reduces rapidly due to the non-zero imaginary part of the loads. Adaptive compensation elements [13] or 4-way outphasing systems [14] can be used to reduce the imaginary part of the loads at lower power levels but add complexity and lossy elements at the output that compromise the efficiency. Variable duty cycle was used in [15] to ensure load-insensitive design conditions across a wide frequency range. The technique in [15] aimed at minimizing the backoff efficiency drop in the frequency range 1.84-2.14GHz with respect to the nominal design at 2.14GHz.

In [7], we presented a new technique to improve the back-

1

off efficiency for OEPAs with load-insensitive class-E designs. Output power contours and efficiency contours of the class-E PAs on the Smith chart were shown to rotate and the power contours were shown to shift by changing just a few class-E design parameters. This rotation and shift were used to considerably improve the efficiency of OEPAs at back-off. Moreover, it was shown that this technique also improves the OPDR and reduces switch voltage stress at back-off.

In contrast to [10], [11], in [7] we used a load-insensitive design which ideally yields 100% efficiency at (almost) 0dB and 10dB back-off levels and more than 95% efficiency between 0dB and 12dB back-off levels. Moreover, theoretically this yields an infinite OPDR without requiring to tune any parameter. Using our technique in [7], the second compensation point can be shifted up to 20dB into back-off. This not only can improve the average efficiency of the OEPAs for modulated signals with high PAPRs, but is also promising for applications with output power control or for multi-mode (standard) PAs with different average output power levels [16]–[18]. Also, our technique does not require to tune the load while parameter tuning is done prior to the series output filter of the class-E PAs to change the (very non-sinusoidal) voltage at the switching node. Moreover, parameter tuning is employed at power backoff which helps to obtain high efficiency both at back-off and at maximum output power. This paper provides more insight to the technique, shows detailed design considerations and provides more measurement results at a higher frequency.

There are other previously published works on the derivation of class-E design equations as well as the effect of changing design parameters on performance and reliability of class-E PAs. The design equations for variable duty cycle, ZVS and ZSS conditions were presented in [19] while [20] derives similar design equations for variable duty cycle and (only) ZVS condition. However, under non-nominal load conditions ZVS and ZSS conditions, both are violated. As a result, the design equations in [19] and [20] cannot be employed to loadpulling nor to study the effect of changing design parameters on load-pull contours. Therefore, new mathematical design equations were derived for general switching conditions (non-ZVS and non-ZSS) similar to [6], [21] but now including the DC-feed inductor loss as well as the switch conduction loss. These derivations are not included in the paper because of length reasons and only the results are summarized and used to explain our efficiency enhancement technique.

A few publications provide a theoretical model for OEPAs. The presented analyses in [22], [23] are (only) for a special case; using ideal loss-less components, RF choke as the DC-feed inductor and 50% duty cycle. The presented semi-analytical design methodology in [24] is for a more general case of arbitrary DC-feed inductor and arbitrary duty cycle. However, the presented theory only works for one outphasing angle where both the branch class-E PAs satisfy a predefined switching conditions (e.g. the ZVS). Then, to have a full picture of the outphasing operation, in [24], simulations were conducted using a commercial computer program.

The paper is organized as follows. A review of the class-E PAs, a load-pull study of load-insensitive class-E PAs and the effect of changing class-E design parameters on load-pull

contours is presented in section II. The presented approach in the current paper to study the OEPAs (in section III) and our efficiency improvement technique at back-off (in section IV) is based on the load-pull study of the class-E PAs presented in section II. This approach makes it possible to theoretically obtain the PA loads, normalized output power, efficiency and reliability related maximum switch voltage for all the outphasing angles and as a result the OPDR. The presented approach can be used with any arbitrary DC-feed inductor (including loss), arbitrary duty cycle, considering the switch conduction loss and we use standard Smith chart representation. Second order effects that come into play for hardware realizations are discussed in section V. The design of a demonstrator OEPA in 65nm CMOS that implements the proposed technique and measurement results thereof are given in sections VI and VII, respectively. Finally, the conclusions are summarized in section VIII.

#### II. CLASS-E POWER AMPLIFIER BASICS

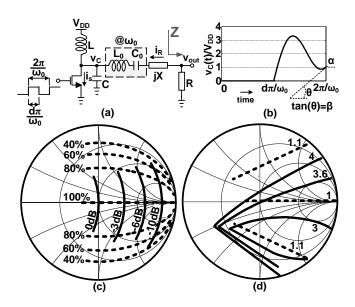

Fig. 1a shows a class-E PA, where the MOS transistor acts as a switch driven by a square wave input signal with (angular) frequency  $\omega_0$  and duty cycle scaling factor of d where d=1 corresponds to 50% duty cycle. The general switching conditions are defined as

$$v_c\left(\frac{2\pi}{\omega_0}\right) = \alpha V_{DD}$$

and  $\frac{dv_c}{dt}\left(\frac{2\pi}{\omega_0}\right) = \beta \omega_0 V_{DD}$  (1)

where  $v_c$  and  $V_{DD}$  are the switch and supply voltage, respectively. L and C form the primary LC-tank to shape the switch voltage according to the required values of  $\alpha$  and  $\beta$ , shown in Fig. 1b, [25], [26]. The relative resonance frequency of this tank is defined [21] as

$$q = \frac{1}{\omega_0 \sqrt{LC}} \tag{2}$$

The second tank, by  $L_0$  and  $C_0$ , is a band pass filter to filter out load current harmonics. A matching network (not shown here for simplicity) provides the load of the PA (R+jX) from the nominal  $50\Omega$  antenna impedance. The relation between circuit elements (L, C, X and R),  $V_{DD}$ ,  $\omega_0$  and output power  $P_{out}$  are formulated by a K-design set [21]:

$$K = \{K_L, K_C, K_X, K_P\} = \{\frac{L\omega_0}{R}, RC\omega_0, \frac{X}{R}, \frac{RP_{out}}{V_{DD}^2}\}$$

(3)

The K-design set for non-ZVS, non-ZSS, arbitrary d and q and taking into account the switch resistance  $R_{on}$  is derived in [6], yielding  $K = K(q, d, m, \alpha, \beta)$ , where  $m = \omega_0 R_{on} C$ .

# A. Load-pulling class-E PAs

For the so-called load-insensitive design [5], [27], a class-E PA is conventionally designed to have q=1.3, d=1, ZVS  $(\alpha=0)$  and ZSS  $(\beta=0)$ . Assuming an ideal switch, (m=0), the K-design set elements can be obtained from e.g. [6] as  $\{K_L, K_C, K_X, K_P\} = \{1.04, 0.58, 0.28, 1.26\}$ . For given  $P_{out}$ ,  $\omega_0$  and  $V_{DD}$ , the component values in Fig. 1a can then be calculated from the K-design set equations in (3).

For a load-pulling analysis, this ideal class-E PA is subjected to different loads. For this, jX is kept constant and only the

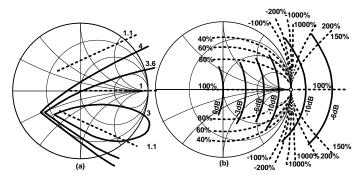

Fig. 1. (a) Single-ended Class-E PA, (b) normalized switch voltage. Load-pull plots for  $q=1.3,\ d=1$  and m=0, (c) normalized output power (solid) and efficiency (dotted) contours, (d) maximum switch voltage normalized to  $V_{DD}$  (solid) and normalized output voltage amplitude (dotted).

load impedance Z, represented by its nominal (real) value R in Fig. 1a, is changed. For simplicity we normalize both the real and imaginary part of Z to R:

$$Z = kR + jk'R \tag{4}$$

Note that for the nominal load, k = 1 and k' = 0. For fixed q, d and m, under non-nominal load conditions ZVS and/or ZSS conditions are violated. A full mathematical derivation of the switch voltage and current is beyond the scope of this paper and can be found in e.g. [6].

These equations can be rewritten to get important properties of both the switch voltage  $v_C(t)$  and the switch current  $i_s(t)$ . This allows to derive e.g.  $P_{out}$  normalized to that at nominal load conditions, the efficiency, the maximum switch voltage  $V_{c,Max}$  normalized to  $V_{DD}$  and the output voltage amplitude  $V_{out}$  normalized to that at nominal load conditions. All these can be derived as a function of k and k' as defined in (4), independent from  $P_{out}$  at nominal conditions, the frequency and the nominal load value R. As a result, for any set of q, d and m, we can now plot contours on a Smith chart with R as the reference impedance, showing the impact of load changes on the performance and behavior of class-E PAs.

For example for a load-insensitive class-E PA with an ideal switch (m=0), the load-pull contours are shown in Fig. 1c and d for a part of Smith chart. The normalized output power and the efficiency contours are shown in Fig. 1c with solid and dotted lines, respectively. Fig. 1c shows that for real loads (for impedances  $\text{Re}\{Z\} \geq R$ ) the efficiency is (ideally) 100% while the output power can be lowered. A non-zero imaginary part of the load will result in  $\alpha \neq 0$  at switching moment and hence causes switching loss (because of discharging the non-zero capacitor voltage) which reduces the efficiency.  $V_{c,Max}$ . contours normalized to  $V_{DD}$  are shown in Fig. 1d. For real loads ( $\text{Re}\{Z\} \geq R$ ) the  $V_{c,Max}$ . stays close to (but is lower than) that for the nominal load. Toward the upper

Fig. 2. Effect of changing q from 1.3 to 1.2 (a,b), respectively 1.4 (c,d) on the load-pull plots for d=1 and m=0. (a,c) Normalized output power (solid) and efficiency (dotted) contours. (c,d)  $V_{c,Max}$ , normalized to  $V_{DD}$  (solid) and normalized output voltage amplitude (dotted).

side of the Smith chart the  $V_{c,Max}$  increases. Normalized output voltage amplitude across the load, shown in Fig. 1d, shows a symmetrical behavior with respect to real axis. These load-pull contours will be used in the next section to describe the behavior of OEPAs and to introduce our method to increase power efficiency in back-off.

### B. Effect of changing q and d on the load-pull contours

Parameters q and d have a major impact on the load-pull contours shown in Fig. 1. In this section we assume that the class-E PA is initially designed for q=1.3 and d=1. Then we change the parameter q (by e.g. changing the capacitor C) and/or change the parameter d and plot the resulting load-pull contours. Again, these contours are independent from  $P_{out}$ ,  $\omega_0$  and the nominal load R.

The load-pull plots are shown in Fig. 2 for changing q from 1.3 to 1.2, respectively 1.4. The shape of the normalized output power, efficiency and  $V_{c,Max}$  contours hardly change except for a rotation: there is clockwise (anti-clockwise) rotation for higher (lower) q. The normalized output voltage contours, shown in Fig. 2b and d, are rotated and changed in shape. Similar contours can be derived and plotted to show the effect of changing d; then clockwise (anti-clockwise) rotation occurs for lower (higher) d. These plots are shown in Appendix A.

#### III. SIMPLIFIED THEORY OF OEPAS

An outphasing class-E PA with a signal component separator (SCS), two class-E branch PAs and a combiner is shown in Fig. 3a. The SCS generates two driving waveforms with phase difference of  $\Delta\theta_{in}$  according to the input signal amplitude.

To be able to map the results of section II, we assume that both class-E PAs, conventionally, are designed to have q = 1.3,

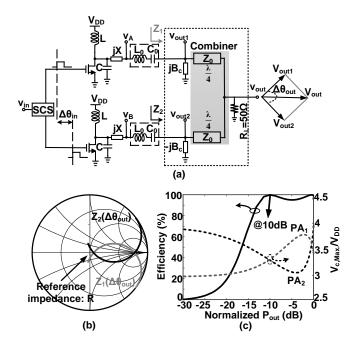

Fig. 3. (a) Outphasing class-E PA with transmission-line based combiner. (b)  $Z_{1,2}$  for  $0 < \Delta \theta_{out} < \pi$  and compensation at outphasing angles  $\frac{\pi}{5}$  and  $\pi - \frac{\pi}{5}$ . (c) Efficiency vs normalized output power (solid) and  $V_{c,Max}$ . normalized to  $V_{DD}$  for PA1 (dotted-grey) and PA2 (dotted-dark).

d=1 and  $\alpha=\beta=0$  for a load  $Z_1=Z_2=R$ . The combiner at the output sums the output voltages to reconstruct an amplified replica of the input signal. Two compensating elements,  $\pm jB_c$  are used to compensate the imaginary part of the loads at two specific outphasing angles. In this paper a transmission-line based combiner is used.

Let's consider the part in the dotted box in Fig. 3a and assume voltages at the branch PAs' outputs as

$$v_{out_{1,2}}(t) = V_{out_{1,2}}\sin(\omega_0 t + \phi_{v_{1,2}})$$

(5)

where  $V_{out_{1,2}}$  and  $\phi_{v_{1,2}}$  are the amplitudes and initial phases with respect to a reference time, respectively. The circuit is linear and can be solved in phasor domain which leads for the apparent load impedances of the two branch PAs to:

$$\frac{1}{Z_1} = +jB_c + \frac{R_L}{Z_0^2} \left( 1 + \frac{V_{out,2}}{V_{out,1}} e^{-j\Delta\theta_{out}} \right)

\frac{1}{Z_2} = -jB_c + \frac{R_L}{Z_0^2} \left( 1 + \frac{V_{out,1}}{V_{out,2}} e^{+j\Delta\theta_{out}} \right)$$

(6)

where  $\Delta\theta_{out}=\phi v_1-\phi v_2$  is denoted as the outphasing angle. To simplify the analysis, let's assume  $\frac{V_{out1}}{V_{out2}}=1$ . We will show the validity of this assumption later in this section. The  $\Delta\theta_{out}$ -dependent impedance seen by each PA,  $Z_{1,2}$ , then is

$$\begin{split} \frac{1}{Z_{1}} &= \frac{2R_{L}}{Z_{0}^{2}}cos^{2}(\frac{\Delta\theta_{out}}{2}) + j\left(-\frac{R_{L}}{Z_{0}^{2}}sin(\Delta\theta_{out}) + B_{c}\right) \\ \frac{1}{Z_{2}} &= \frac{2R_{L}}{Z_{0}^{2}}cos^{2}(\frac{\Delta\theta_{out}}{2}) - j\left(-\frac{R_{L}}{Z_{0}^{2}}sin(\Delta\theta_{out}) + B_{c}\right) \end{split} \tag{7}$$

where we assume  $Z_0 = \sqrt{2RR_L}$ . For  $B_c < \frac{R_L}{Z_0^2}$ , there are two outphasing angles for which the imaginary part of the loads  $Z_{1,2}$  is zero.  $Z_{1,2}$  for a range  $0 < \Delta \theta_{out} < \pi$  are shown in

Fig. 3b on the Smith chart for  $B_c = \frac{1}{2R} sin(\pi/5)$ , assuming R as the reference impedance.

Having PA loads  $Z_{1,2}$ , shown in Fig. 3b, on top of the load-pull contours of the normalized output voltage amplitude shown in Fig. 1d, yields two important observations. Firstly, the output voltage of the branch PAs is not constant across different outphasing angles and therefore, the PAs cannot be modeled as ideal voltage sources as was done in e.g. [5] (although the same final results for  $Z_{1,2}$  were obtained). Secondly, because of the symmetry of the PA loads  $Z_{1,2}$  and of the normalized output voltages contours with respect to the real axis, for all outphasing angles  $\frac{V_{out,1}}{V_{out,2}} = 1$  which proves the validity of our assumption leading to (7).

To get the output power and the efficiency for an OEPA as a function of power back-off, the normalized power contours and the efficiency contours of Fig. 1c can be combined with the  $\Delta\theta_{out}$ -dependent load impedance for the two branch PAs of an OEPA, described in (7) and shown in Fig. 3b. Then for each  $\Delta\theta_{out}$ , the output power and the efficiency of the branch class-E PAs follow. Due to symmetrical PA loads and contours with respect to the real axis, the output power and efficiency of both branch PAs are identical.

Combining the output power as a function of  $\Delta\theta_{out}$  and the efficiency as a function of  $\Delta\theta_{out}$  yields Fig. 3c, that shows the efficiency of the OEPA plotted versus the (normalized) output power. The second compensation point is located at 10dB back-off where the efficiency is (ideally) 100 %. Similarly, the  $V_{c,Max}$  (normalized to  $V_{DD}$ ) for the two branch PAs can also be derived as a function of the power back-off. Fig. 3c shows that the  $V_{c,Max}$  for PA2 increases at back-off. We will also address this issue in the measurement section. All plots of Fig. 3c are valid under the assumption of an ideal OEPA with an ideal combiner and assuming a very high loaded quality factor for the  $L_0-C_0$  filter.

#### A. Output Vectors' Amplitude Mismatch

In theory, the branch class-E PAs are identical and hence have 0% mismatch/error between the output voltage amplitudes  $V_{out,1,2}$ . The normalized output power, shown in Fig. 3c, is then 0 for  $\Delta\theta_{out}=\pi$  which yields an infinite OPDR.

Any mismatch between the two paths in an outphasing system that causes amplitude errors between the two output vectors  $V_{out1}$  and  $V_{out2}$ , reduces the OPDR. Using the vector diagram in Fig. 3a and assuming a relative amplitude error  $\epsilon$  between the two vectors,  $V_{out1} = V$  and  $V_{out2} = V(1 + \epsilon)$ , the maximum attainable OPDR can then be written as

$$OPDR(dB) = 20 \log \left( \frac{\max(V_{out})}{\min(V_{out})} \right) = 20 \log(1 + \frac{2}{\epsilon}) \quad (8)$$

Using (8), to have an OPDR better than 60dB [27], the amplitude error should be kept below 0.2 % while mismatch less than 6.5% keeps the OPDR better than 30dB [10].

One of the mechanisms that leads to amplitude error, is the residual impedance of the series filter  $L_0 - C_0$  due to e.g. frequency deviations or components spread. For instance, the

residual impedance at  $\Delta\omega$  deviation from the center frequency  $\omega_0 = \frac{1}{\sqrt{I_0 C_0}}$  can be written as

$$Z_r(\Delta\omega) = L_0(\omega_0 + \Delta\omega)j - \frac{j}{C_0(\omega_0 + \Delta\omega)} \approx 2L_0\Delta\omega j \quad (9)$$

For  $\Delta\omega=0$ ,  $Z_r=0$  and the filter passes the first harmonic of the signal without any error. However, non-zero  $Z_r$  causes a voltage division at the inputs of the combiner and hence creates error.

To find a simple quantitative model, consider the OEPA system, shown in Fig. 3a and assume that, for small  $\Delta\omega$ , the combiner, the q parameters, the compensation elements impedance and the first harmonic of the signals at nodes A and B (before the filter) are not affected. Then we can assume identical first harmonics  $V_A = V_B = V$  for nodes A and B for identical class-E branch PAs. For minimum output power,  $\Delta\theta_{out} = \pi$ , and therefore  $V_{out1}$  and  $V_{out2}$  can be written as

$$V_{out1}(\Delta\theta_{out} = \pi) = \frac{Z_1 V_A}{Z_1 + Z_r} = \frac{V}{1 - 2L_0 B_c \Delta\omega}$$

$$V_{out2}(\Delta\theta_{out} = \pi) = \frac{Z_2 V_B}{Z_2 + Z_r} = \frac{V}{1 + 2L_0 B_c \Delta\omega}$$

(10)

where we replaced  $Z_1$  and  $Z_2$  from (7) for  $\Delta\theta_{out}=\pi$  and  $Z_r$  from (9). Assuming the loaded Q of the filter as  $Q_L=\frac{L_0\omega_0}{R}$  and locating the second compensation point at 10dB back-off  $(B_c=\sin(\pi/5)/2R)$ ,

$$\frac{V_{out1}}{V_{out2}}(\Delta\theta_{out} = \pi) = \frac{1 + Q_L \sin(\frac{\pi}{5})\frac{\Delta\omega}{\omega_0}}{1 - Q_L \sin(\frac{\pi}{5})\frac{\Delta\omega}{\omega_0}}$$

(11)

$Q_L$ =5,  $\frac{\Delta\omega}{\omega_0}$ =+1% and  $\frac{\Delta\omega}{\omega_0}$ =+5% yield  $\frac{V_{out1}}{V_{out2}}$  equal to 1.06 and 1.34, respectively. According to (8), and assuming that  $Z_T$  will not affect maximum  $P_{out}$ , these amplitude errors limit OPDR to 30dB respectively 16dB. Moreover,  $\frac{\Delta\omega}{\omega_0}$ =-1% and  $\frac{\Delta\omega}{\omega_0}$ =-5% results in  $\frac{V_{out1}}{V_{out2}}$  equal to 0.94 and 0.74, respectively, which limits OPDR to 31dB and 19dB, respectively.

# IV. BACK-OFF EFFICIENCY IMPROVEMENT TECHNIQUE

This section presents detailed discussions of the technique presented in [7] to improve the back-off efficiency of the OEPAs. The starting point is again a conventional OEPA with  $q_1 = q_2 = 1.3$  and with the second compensation points located at 10dB back-off.

#### A. Rotation

Adaptively changing the compensating elements  $\pm jB$  in the OEPA or employing 4-way outphasing system can improve the efficiency at more back-off levels. However, a more efficient way — both for efficiency and for integration — is to change the parameter q of both branch PAs. Fig. 2 shows that by increasing (decreasing) the parameter q, the power and efficiency contours rotate in the clockwise (anti-clockwise) direction.

Using Fig. 3b, to shift the compensation point deeper into back-off, the contours for PA1 should rotate in the clockwise direction and simultaneously the contours for PA2 must rotate in the anti-clockwise direction. To accomplish this, for PA1

the q must be increased (e.g. from 1.3 to 1.4) and for PA2 it must be reduced (e.g. from 1.3 to 1.2).

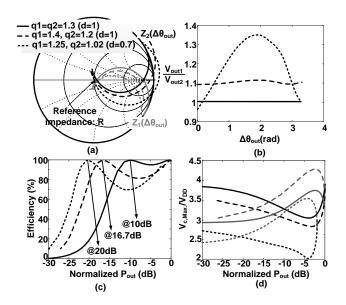

To find the efficiency of the OEPA having different q for the two branch PAs, again the PA loads  $Z_{1,2}$  need to be known. However, whereas in the previous section  $V_{out2} = V_{out1}$  due to having the same q in both branch PAs, this condition is inherently violated now, see e.g. Fig. 2b and d. Therefore, (7) cannot be used and the general equation (6) must be employed. For each outphasing angle  $\Delta \theta_{out}$ , we use a simple iterative method to find the PA loads; in it we start at  $V_{out1} = V_{out2}$ and estimate the loads from (6). For the calculated loads, we use the data in Fig. 2b and d to update the estimated  $\frac{V_{out1}}{V_{out2}}$ and to then recalculate the loads from (6). We terminated this iterative routine upon reaching a sufficiently low change in  $\frac{V_{out1}}{V_{out2}}$ ; typically lower than 1% error was reached within 2 or 3 iterations. The PA loads  $Z_{1,2}$  and  $\frac{V_{out1}}{V_{out2}}$  for  $q_1=1.4$  and  $q_2=1.2$  are shown with dashed lines for  $0 \leq \Delta \theta_{out} \leq \pi$  in Fig. 4a and b. For comparison, the corresponding curves for a conventional OEPA ( $q_1 = q_2 = 1.3$ ) are shown using solid

After obtaining the PA loads  $Z_{1,2}$  as a function of  $\Delta\theta_{out}$ , for specific  $q_1$  and  $q_2$ , and using the load-pull contours in Fig. 2, the output power, efficiency and the normalized  $V_{c,Max}$  can directly be obtained. These are shown in Fig. 4c and d with dashed lines.

Fig. 4c shows that the second compensation point is shifted from the initial 10dB back-off (for  $q_1=q_2=1.3$ ) to almost 17dB into back-off for  $q_1=1.4$  and  $q_2=1.2$ ; here the power efficiency is 100%, see Fig. 4c. Fig. 4a shows the PA loads  $Z_{1,2}$ ; the negative real part of  $Z_2$  for  $\Delta\theta_{out}$  close to  $\pi$  implies that PA2 absorbs part of the power provided by PA1. The extension of the load-pull contours, presented in Fig. 1c and d for positive loads, toward negative impedances is presented in Appendix B. Note that for the OEPA shown in Fig. 3a, there is no risk for the stability as the loop gain, for the loop consists of the nodes  $V_{DD}-v_A-v_{out,1}-v_{out}-v_{out,2}-v_B-V_{DD}$ , is always less than unity due to the loss of the components, switch loss and mainly due to the fact that  $P_{out}>=0$ .

The (almost) 10% unbalance between the two branch PAs, visible in Fig. 4b for  $q_1=1.4$  and  $q_2=1.2$ , limits the OPDR according to (8) to about 27dB. Shifting the second compensation point more into back-off with extra rotation will limit the OPDR more. The unbalance due to rotation, however, can be used to compensate the amplitude error due to e.g. frequency deviations, discussed in section III-A. For negative frequency deviations where  $\frac{V_{out1}}{V_{out2}}$  goes below 1, the rotation according to Fig. 4 can be employed to increase the amplitude ratio toward unity and to improve the OPDR. For positive frequency deviations, where  $\frac{V_{out1}}{V_{out2}}$  increases above unity, rotation in reverse direction by reducing  $q_1$  or/and increasing  $q_2$  should be employed to reduce the amplitude ratio. In this case, however, the back-off efficiency will reduce compared to the conventional design having  $q_1=q_2=1.3$ . The next section extends the shift technique with the rotation to compensate for this efficiency drop.

Fig. 4d shows the  $V_{c,Max}$  versus the normalized output power (back-off), illustrating that the  $V_{c,Max}$  in back-off can be reduced with shifting the second compensation point further

Fig. 4. Ideal OEPA results for  $0 \le \Delta \theta_{out} \le \pi$  for conventional design with  $q_1 = q_2 = 1.3$  (solid), for rotation with  $q_1 = 1.4$  and  $q_2 = 1.2$  (dashed) and for shift-rotation with d = 0.7,  $q_1 = 1.25$  and  $q_2 = 1.02$  (dotted): (a) PA loads  $Z_1$  (grey) and  $Z_2$  (dark) , (b)  $\frac{V_{out1}}{V_{out2}}$  vs  $\Delta \theta_{out}$ , (c) efficiency vs normalized output power and (d)  $V_{c,Max}$ . normalized to  $V_{DD}$  for PA1 (grey) and PA2 (dark).

into back-off.

#### B. Shift

Reducing the parameters d and q for both branch PAs results in rotation in the opposite directions. Therefore, for a lower d (e.g. 0.7), a lower q (e.g. 1.1) can be found to have almost same efficiency contours for the branch PAs at a lower output power level. This corresponds to a shift of power contours to the left on Smith chart for almost the same efficiency contours. As a result the output power at (e.g.) the second compensation point can be lowered while the efficiency is 100%: the second compensation can be shifted to a lower output power levels.

This technique can be combined with the rotation technique to shift the second compensation point more into back-off. For this, the d for both branch PAs are reduced to 0.7 for  $q_1 = q_2 = 1.1$  to shift the power contours. Subsequently  $q_1$ is increased to 1.25 and  $q_2$  is reduced to 1.02 to rotate both the power and the efficiency contours. Following the same procedure as in the previous section, the load-pull contours can be plotted and a simple iterative procedure can be used to find  $\frac{V_{out1}}{V_{out2}}$  for each  $\Delta\theta_{out}$  which results in the PA loads  $Z_{1,2}$ . For length reasons the load-pull contours are not shown here but the effect of the shift-rotation technique on the OEPA performance and behavior is shown in Fig. 4 with dotted lines. Fig. 4b shows that the output voltage amplitude error first increases with  $\Delta\theta_{out}$ , and again reduces when  $\Delta\theta_{out}$ approaches  $\pi$ , which therefore helps to improve the efficiency without sacrificing the OPDR.

Fig. 4c shows that the second compensation point is now shifted to almost 20dB into back-off with lower switch voltage stress deep in back-off. However, by fine tuning of the parameters d,  $q_1$  and  $q_2$ , the second compensation point can

be easily shifted to any arbitrary back-off level between 10dB and 20dB. Furthermore, shifting the power contours can lower the maximum output power. For maximum output power and to benefit from the high back-off efficiency that the presented shift-rotation technique brings to the OEPA, one can tune the parameters d and q dynamically according to the required instantaneous output power.

#### V. SECOND ORDER EFFECTS

#### A. Switch conduction loss

In the previous sections the switch was assumed to be ideal (m=0). However, being implemented by transistors, the switch-on resistance  $R_{on}$  is non-zero which causes conduction loss for the time period during which the switch is closed. For a non-zero m, the output power and efficiency contours in Fig. 5a for a single class-E PA with q=1.3 and d=1 follow for a switch-on resistances with  $m=0.05^{-1}$ .

Compared to the ideal load-pull contours shown in Fig. 1c, the elliptical shape of the efficiency contours is noticeable and, for real loads, the efficiencies between 3dB to 6dB back-offs are higher (>85%) than the efficiency at peak output power (<80%). Moreover, the elliptical shape of the efficiency contours seriously impacts the improvement that the rotation technique of section IV brings to the OEPAs.

Fig. 5b shows the effect of reducing q and d on the power and efficiency contours; not only the power contours are shifted to the left, but that also the efficiency at back-off is improved. At e.g. the cross sections of the -10dB contours and the real axis in Fig. 5a and b, the efficiency is improved from almost 70% to 90%. To benefit from these improved efficiency contours at back-off, the rotation technique can now be employed to optimally place the contours on the Smith chart for the actual load at back-off.

To demonstrate the effect of the shift-rotation technique in the case of lossy switch with m=0.05, we follow the same procedure as section IV and derive the efficiency and the output power, yielding the plots in Fig. 5c and d for  $B_c = \sin\left(\frac{\pi}{5}\right)/2R$  (correponding to compensation at 10dB back-off for  $m=0^2$ ). The results for the conventional OEPA design  $(q_1 = q_2 = 1.3 \text{ and } d = 1)$  are shown with soliddark lines. For comparison, the efficiency of an OEPA with  $q_1 = q_2 = 1.3$ , d = 1 and m = 0.05 with (ideal) real load modulation (zero imaginary part) is also shown in Fig. 5c and d with a solid grey curve. For this, the efficiency and the output power are obtained from Fig. 5a for real loads in the range of  $[R,\infty]$ . This curve also corresponds to the maximum reachable efficiency for techniques that rely on reducing the imaginary part of loads for the branch PAs at back-off to improve the back-off efficiency, e.g. the adaptive Chireix compensation elements technique [13] or 4-way OEPA systems [14].

$^{1}$ It is shown that m only depends on the technology and the operation frequency [25]. For this paper, at the frequency of interest (1.8GHz) for a cascode switch in 65nm CMOS technology m=0.05 shows a fair agreement between theory and simulation results.

<sup>2</sup>Non-zero m (m=0.05) slightly changes the power contours. It can be shown that for m=0.05,  $B_c = \sin\left(\frac{\pi}{5}\right)/2R$  corresponds to the compensation of the imaginary parts of the loads at (almost) 9dB back-off. But in this paper, for simplicity, we ignore this small difference

Fig. 5. (a,b) The output power (solid) and the efficiency (dotted) contours for a single class-E PA with (a) q=1.3, d=1 and m=0.05 and (b) q and d are reduced to 1.1 and 0.7, respectively. (c,d) The efficiency versus normalized output power for an OEPA with m=0.05 for the class-E branch PAs and with conventional design and compensation at 10dB back-off (solid-dark), with an ideal load modulation with zero imaginary part (solid-grey), with the rotation (dashed-dark), with the shift-rotation with setting Sett. 1 (dotted-dark) and the shift-rotation with setting Sett. 2 (dashed-dotted-dark).

Fig. 5c shows that compensation at 10dB back-off for a conventional OEPA, with  $q_1=q_2=1.3, d=1$ , having a lossy switch can achieve the maximum reachable efficiency (80% for m=0.05) at full power and near 10dB back-off. The figure also shows that the rotation technique can improve the efficiency at more than 15dB back-off. Comparing Fig. 5c and 4c also clearly shows that the switch conduction loss seriously impact the improvement of our proposed rotation technique as well as achieved by the adaptive tuning (or 4-way OEPA). On top of that, also additional losses of the tuning elements or due to extra components at the output can compromise this improvement. This last issue is also addressed in the measurements section.

Fig. 5d shows the effect of shift-rotation technique on the efficiency for two different settings Sett.1:  $\{q_1, q_2, d\} = \{1.25, 1.02, 0.7\}$  and Sett.2:  $\{q_1, q_2, d\} = \{1.18, 0.95, 0.5\}$  with dotted and dashed-dotted curves, respectively. The shift-rotation technique can significantly increase the efficiency in back-off: e.g. the efficiency is improved from less than 10% to more than 75% at 20dB back-off (more than  $\times 7.5$  improvement).

#### B. Limited quality factor of the DC-feed inductor L

Another important loss mechanism is due to the limited quality factor (Q) of the DC-feed inductor L, shown in Fig. 3a. This inductor can be a separate component [7] or it can be a part of the transformer-based combiner [5], [27]. To study this effect, one can derive a new set of load-pull equations using Q as a parameter. This derivation is not given here for simplicity and length reasons.

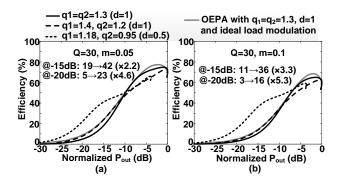

Fig. 6. The efficiency versus normalized output power for a conventional OEPA with  $q_1=q_2=1.3$  and compensation at 10dB back-off (solid-dark) and with an ideal load modulation (solid-grey), the rotation (dashed-dark), the shift-rotation with setting Sett. 2 (dotted-dark): (a) m=0.05 and (b) m=0.1.

The resulting efficiency versus power curves for m=0.05 and m=0.1 and for quality factor value Q=30 are shown in Fig. 6 for the conventional OEPA design (solid curve) with compensation at 10dB back-off, using the rotation technique (dashed curve) and for the shift-rotation with setting Sett.2 (dotted curve). For comparison, both graphs in Fig. 6 include a solid-grey curve that corresponds to the maximum efficiency of an OEPA with conventional design and ideal real load modulation, for the specific Q and m listed for each graph. Again, these curves represent the upper efficiency limit for any technique that optimizes efficiency by reducing the imaginary part of loads for the branch PAs at back-off [13], [14].

For the both cases, employing only the rotation technique can improve the efficiency to the maximum reachable efficiency (grey curve) at back-offs up to around 20dB. However, the improvement with respect to a conventional OEPA (black solid curve) almost vanishes for high m or low Q. This is due to compression of the elliptical efficiency contours. However, the rotation technique can be used both to reduce the switch voltage stress at back-off and to improve the OPDR.

The proposed shift-rotation technique, however, improves the efficiency at back-off to levels significantly higher than the maximum reachable efficiency with real load modulation. Also, the improvement ratio increases with increasing switch conduction loss for a constant Q (the absolute efficiencies are lower though). For instance, at 20dB back-off, more than  $\times 4.6$  and  $\times 5.3$  higher efficiencies with respect to the conventional design are obtained for respectively, m=0.05 and 0.1. It can be concluded that this shift-rotation technique is quite promising to improve the efficiency of an OEPA with an integrated combiner at high frequencies e.g. [27], where the switch conduction is the dominant loss mechanism.

### VI. IMPLEMENTATION IN 65NM CMOS TECHNOLOGY

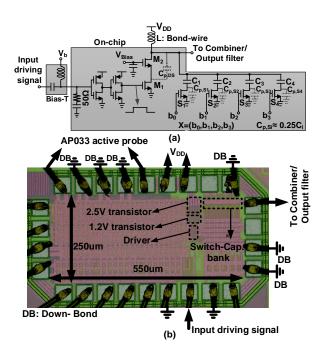

The schematic of a single class-E branch PA and its driver stage is shown in Fig. 7a. Note that this system serves to demonstrate the performance increase of our shift-rotation technique, and does not aim at a specific transmit standard or application. The switch is implemented by a cascode structure employing a 1.2V thin oxide transistor (W/L=

0.84mm/60nm) as switch transistor and a thick oxide 2.5V transistor (W/L=1.65mm/280nm) as cascode device. The cascode structure allows  $V_{c,Max}$ . up to 4V for reliability reasons.

Using the K-design set elements for  $q=1.3,\ d=1,\ m\approx 0.05$  and  $\alpha=\beta=0$  and for  $R=15\Omega,\ \omega_0=2\pi 1.8 {\rm GHz},\ {\rm yields}\ L=1.4 {\rm nH},\ C=3.3 {\rm pF}$  and  $X=0.5 {\rm nH}.$  The DC-feed inductor L is implemented by two parallel bondwire inductances to provide a relatively high quality factor Q ( $\approx 25$ ). The tank capacitor C at the switching node was implemented with the drain-bulk and gate-drain parasitic capacitance of the cascode transistor. Moreover, the drain and the source of the cascode transistor were layed out close to each other to introduce some parasitic capacitance  $C_{P,DS}$  to achieve slightly better efficiency [28]. Two cascaded inverters were used as the driver for the switch where the duty cycle can be controlled by the off-chip control voltage  $V_b$ .

Two switched capacitor banks with 4 control bits X1 and X2 were used at the switching nodes to tune the q parameter of the branch PAs independently. Circuit simulations in 65nm CMOS technology suggest that a total switchable capacitance of 1.5pF is more than sufficient to employ the shift-rotation technique with shifting the contours up to 5dB. This 1.5pF capacitor is divided into 4 sections with  $C_1 = 150$ fF,  $C_2 = 300$ fF,  $C_3 = 450$ fF and  $C_4 = 600$ fF, shown in Fig. 7a, being controlled with 4 control switches  $S_i$ ,  $i \in \{0, 1, 2, 3\}$ .

When each switch  $S_i$  is off, it needs to tolerate the maximum voltage at the switching node which can be up to 4V. The switches  $S_i$  are implemented by 2.5V thick oxide transistors. There is a parasitic capacitance  $C_{p,S_i}$  associated with the switch  $S_i$ , shown in Fig. 7a. The switches  $S_i$  are sized to have  $C_{p,S_i} \approx \frac{1}{4}C_i$  to make sure the maximum voltage across the switches  $S_i$  does not exceed (almost) 3V. This switch-capacitor network at the switching node introduces extra capacitive loading at this node when all control bits are zero, which amounts to 0.3pF or 10% of the total drain capacitance. To compensate for this extra capacitance, the switch size was reduced by 10%. This increases m by 10% which impacts the (simulated) efficiency at maximum output power and at the back-off by less than 3%.

To have the high and low level of the voltages at the driver output well defined, the driver and the main switch share the same ground and to reduce the bond-wire inductance at ground 6 parallel down-bonds (DBs) with minimum length were used (shown in Fig. 7b). The switches  $S_i$  are controlled quasi-statically, driven from off-chip sources; no dynamic tuning is provided for this paper. The microphotograph of the implemented branch class-E PA is shown in Fig. 7b.

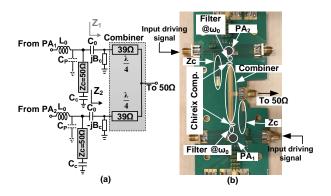

The detailed implementation of the off-chip transmission-line based combiner and the output series filters  $L_0-C_0$  are shown in Fig. 8a. The combiner is implemented on I-Tera MT RF substrate with a dielectric constant 3.45 and 0.5mm thickness. The characteristic impedance  $Z_0$  is obtained for  $R=15\Omega$  and  $R_L=50\Omega$  as  $Z_0=\sqrt{2RR_L}\approx 39\Omega$ . The total series inductance at the branch class-E PAs outputs  $(X+L_0)$  is implemented partly by the bond-wire inductance and partly by an off-chip component. The loaded quality factor of the output filter for  $R=15\Omega$  is roughly 5. Due to the

Fig. 7. The branch class-E PAs (a) schematic, (b) chip microphotograph

Fig. 8. (a) The detailed schematic of the combiner, (b) the designed PCB

small thickness of the substrate and the relatively high loaded quality factor of the series filter, the parasitic capacitance  $C_p$  becomes noticeable and changes the impedance level and impedance behavior  $Z_{1,2}$  with  $\Delta\theta_{out}$ . To reduce this effect, a parallel quarter wavelength transmission-line terminated with a capacitor  $C_c = \frac{1}{C_p\omega^2Z_c^2}$  was used. The final designed PCB is shown in Fig. 8b with the mounted branch class-E PAs.

# VII. MEASUREMENT RESULTS

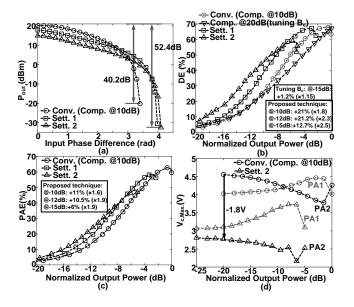

Measured  $P_{out}$  versus  $\Delta\theta_{in}$  for 3 different conditions is shown in Fig. 9a for compensation of the imaginary part of the PA loads at 10dB back-off. +20.1dBm maximum output power  $(P_{out,Max.})$  is achieved for the conventional design from 1.25V supply voltage at 1.8GHz while the mismatch between the branches limits OPDR to 40.2dB. Changing the PA settings to Sett. 1, shifts the power contours by almost -2.3dB and rotates them which result in better than 50dB OPDR. Reducing duty cycles (setting 2), result in almost -5.15dB shift in power contours and in an OPDR improvement to more than 52dB. The improvement in the OPDR is (mainly) due to tuning

Fig. 9. (a) Measured  $P_{out}$  versus  $\Delta\theta_{in}$  for compensation at 10dB back-off and 3 different settings; conventional with  $V_b$ =0.6V,  $X_1$ =0000 and  $X_2$ =0000 (corresponding to  $\{q_1,q_2,d\}\approx\{1.3,1.3,1\}$ ), Sett.1 with  $V_b$ =0.43V,  $X_1$ =0011 and  $X_2$ =1010 (corresponding to  $\{q_1,q_2,d\}\approx\{1.25,1.02,0.7\}$ ) and and Sett.2 with  $V_b$ =0.36V,  $X_1$ =0000 and  $X_2$ =1111 (corresponding to  $\{q_1,q_2,d\}\approx\{1.18,0.95,0.5\}$ ). (b) Measured DE for conventional compensation at 10dB back-off, Sett. 1 and 2 and for conventional setting and compensation at 20dB back-off (by tuning  $B_c$ ). (c) Measured PAE for compensation at 10dB back-off and 3 different settings. (d) Measured  $V_{c,Max}$ . for compensation at 10dB back-off and 2 different settings.

the voltage ratio  $\frac{V_{out1}}{V_{out2}}$  to cancel out the amplitude mismatch between the two branches, discussed in sections III-A.

Fig. 9b shows the Drain Efficiency (DE) versus power back-off for 4 different conditions. Compensation at 20dB back-off (dark-triangle (down)), by tuning  $B_c$ , with respect to compensation at 10dB (grey-circle), brings less than  $\times 1.15$  improvement at 15dB back-off at the cost of reducing the efficiency at higher power levels. Employing adaptive elements [13] or using more components at the output to implement a 4-way system [14] will limit the improvement even more. However, as shown in Fig. 9b and c, the presented shift-rotation technique can effectively improve the DE and PAE.

Fig. 9b shows that measured DE at  $P_{out,Max}$ . for the conventional setting and compensation at 10dB back-off is 65.3% and maximum DE is 68% at 1dB back-off. PAE at  $P_{out,Max}$ ., shown in Fig. 9c, is 60.7%. By our proposed shift-rotation technique,  $\times 2.5$  better DE and almost  $\times 2$  better PAE at 15dB back-off were achieved. PAE at 0dBm output power (20dB back-off) is also improved from 2% to more than 4%. Therefore, to transmit 1mW power the presented technique reduces supply power from 50mW to less than 25mW.

Measured  $V_{c,Max}$ . for both PAs at 1.8GHz for compensation at 10dB back-off are shown in Fig. 9d. For this, the transient waveforms were measured against the power back-off using an AP033 active probe and a 80GSa/s Agilent Oscilloscope. Maximum voltage, for the conventional configuration at maximum  $P_{out}$  and for both switches, is almost 4V. For PA2, however, it increases to more than 4.5V at 20dB back-off which can cause reliability issues. Fig. 9d shows that our proposed shift-rotation technique can significantly reduce the  $V_{c,Max}$  in power back-

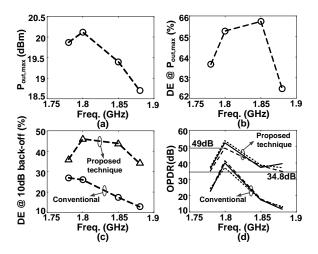

Fig. 10. (a) Measured maximum  $P_{out}$ , (b) DE at maximum  $P_{out}$ , (c) DE at 10dB back-off and (d) OPDR (for three different PA realizations, each with two (unselected) class-E PA ICs) versus frequency for conventional design with  $V_b$ =0.6V,  $X_1$ =0000 and  $X_2$ =0000 and for the proposed technique with  $V_b$ =0.43V,  $X_1$ =0000 and  $X_2$ =1111 at 1.78GHz, with  $V_b$ =0.36V,  $X_1$ =0000 and  $X_2$ =1000 at 1.85GHz and with  $V_b$ =0.36V,  $X_1$ =0000 and  $X_2$ =0000 at 1.88GHz.

off; -1.8V reduction was measured for PA2 at 20dB back-off which reduces transistor degradation and hence improves the PA life-time.

We also measured the system performance across a frequency range from 1.78GHz to 1.88GHz, see Fig. 10. The maximum  $P_{out}$  at conventional setting is higher than 18.7dBm with more than 62% DE. Increasing the frequency from 1.8GHz to 1.88GHz results in 1.4dB reduction in the maximum output power. Increasing the frequency, for both the branch class-E PAs the parameter q reduces which rotates and slightly shifts the power contours to the left (shown in Fig. 2a). Also, the positive residual impedance of the series filter at higher frequencies, rotates the PA loads toward the right-hand side of the Smith chart which further reduces the maximum output power. And finally, our transmission-line based power combiner is a narrow band combiner which further impacts the maximum output power by deviating from the center frequency [35].

The DE for conventional setting at 10dB back-off, shown in Fig. 10c reduces with increasing frequency due to the rotation of both efficiency contours in the same direction (counter-clockwise due to reduced q). However, the proposed technique improves the 10dB back-off efficiency to more than 34%.

Executing the measurements with different samples, (almost) the same numbers for the maximum output power, efficiency at maximum output power and at 10dB back-off were obtained. However, the OPDR is sensitive to the mismatch between the two samples. Fig. 10d shows the OPDR for three different PA realizations, each of these using their own set of (unselected) class-E PA ICs from the same batch. The OPDR for conventional design at center frequency (1.8GHz) is more than 37dB and it reduces sharply with deviating the frequency from 1.8GHz. The OPDR reduces to almost 11dB (solid curve) at 1.88GHz (4.45% deviation from 1.8GHz). This is mainly due to the residual impedance of the filter at frequencies

Fig. 11. (a) Measured output voltage  $(V_{out})$  amplitude (dark) and phase (grey) versus input phase difference for 2 different settings at 1.8GHz. The effect of DPD on PSD (b) and symbol constellation (c) for the conventional setting and for a 64QAM amplitude modulated signal. (d) Measured symbol constellation (after DPD) for the conventional setting and for a 1.8GHz 256QAM modulation. (e) EVM versus modulation BW for the conventional setting. (f) Measured PSD for the 256QAM and 64QAM modulations with 12.5MHz, respectively 20MHz modulation bandwidths.

different from the  $\omega_0$ , discussed in section III-A. The presented technique, however, improves the OPDR to more than 49dB at 1.8GHz and to more than 34.8dB across 100MHz bandwidth. As discussed in section IV-A, toward higher frequencies we rotate the contours of PA2 in reverse direction by increasing  $q_2$ . For this  $X_2$  is reduced from 1111 at 1.8GHz to 0000 at 1.88GHz for the same  $V_b$ . Toward lower frequencies, however, we need to rotate the contours more, in the same direction that we rotate at 1.8GHz. This is done by slightly increasing d.

The designed OEPA was also characterized using single carrier 1.8GHz amplitude modulated signals. For this first the output voltage amplitude ( $V_{out}$  in Fig .3a) and phase are measured versus  $\Delta\theta_{in}$  for 2 different settings, shown in Fig. 11a to implement a memory-less Digital Pre-Distortion (DPD).

The output power spectral density (PSD) and symbol constellation for a single carrier 7dB PAPR 64QAM amplitude modulated signal with 5MSym/s symbol rate are shown in 11b and c for two cases, without DPD and using a memoryless DPD. For this, the polar representations (the normalized envelope and the angle) of the time domain base-band IQ signals were generated in Matlab. Then, we constructed two carrier signals (at 1.8GHz) where the phase difference between

the two carries was obtained from inverse cosine of the envelope (non-DPD case) and for the DPD, the inverse of plots shown in Fig. 11a (in dark). The common mode phase of the carriers is equal to the angle of the IQ signal (no-DPD). However, for the DPD, the output voltage phases, shown in Fig. 11a (in grey), were derived from the common mode phase of the carriers. The two carrier signals were then uploaded to a 12GS/s M9502A Agilent Arbitrary Waveform Generator with two output channels to drive the two class-E branch PAs. Fig. 11c shows that, for the conventional design, DPD improves the RMS EVM from -24.6dB to -34.8dB with 13.1dBm average  $P_{out}$  ( $P_{out,avq.}$ ), 41.8% DE and 33.6% PAE. The measured symbol constellation (using DPD) for a single carrier 7.6dB PAPR 256QAM amplitude modulated signal with 10MSym/s symbol rate and for the conventional setting is also shown in Fig. 11d. +12.5dBm average output power with 37.6% DE and 30% PAE was measured at -31.3dB RMS EVM level. Dynamic tuning of parameters d and q was not implemented in this current work. However, if dynamic tuning would be used to tune the parameters d and q according to the instantaneous output power level, it can be estimated that the PA then could provide about 48%<sup>3</sup> DE for 7.6dB PAPR 256QAM amplitude modulated signals.

Measured EVM as a function of the modulation bandwidth is shown in Fig. 11e for both 64QAM and 256QAM modulations at a constant average output power. The EVM increases with increasing bandwidth (signal symbol rate). The limited bandwidth of the OEPAs is both due to  $10{\sim}15x$  bandwidth expansion that comes with the non-linear SCS operation in outphasing mode [34] and due to the limited bandwidth of the output series filter and the combiner. Ways to improve the modulation bandwidth include a lower loaded quality factor for the output filters and using transformer based combiners [35]. The output PSDs for the 256QAM and 64QAM amplitude modulations with 12.5MHz, respectively 20MHz modulation bandwidths are shown in Fig. 11f.

Finally, we measured the OEPA performance with 256QAM modulated signals with different  $P_{out,avg}$  to demonstrate the effect of the proposed technique in the efficiency improvement of the OEPA at back-off. A summary of the measured DEs and PAEs are given in Table I. At 5dB back-off ( $P_{out,avg}$ .=7.5dBm) the DE and PAs are improved from 14.8% and 11.3% for the conventional design to 29% (× 1.96) and 17.9% (× 1.6) at a better EVM level. At 10dB back-off ( $P_{out,avg}$ .=2.5dBm) DE and PAE are improved by × 2.4 and × 1.7 with better RMS EVM.

In Table II, the measured results at 1.8GHz are benchmarked against the other CMOS PAs. The designed PA at conventional settings provides the best DE and PAE for single tone excitation at maximum output power. Furthermore, the presented technique improves the DE at 12dB back-off to more than 1.7 times better than other published works with a comparable PAE. The presented demonstrator PA has 20.1dBm maximum

$<sup>^3</sup> The$  average efficiency was estimated from the integral  $\int_{-\infty}^0 p df(BF). \max{(DE(BF))} d(BF)$  where pdf(BF) is the probability density function of back-off level BF for a modulated signal and  $\max(DE(BF))$  is the maximum achievable efficiency at back-off level BF for the three different settings shown in Fig. 9b.

TABLE I MEASURED EFFICIENCY (AFTER DPD) FOR 7.6DB PAPR 256QAM MODULATION WITH 6.25MHz (5Msym/s) and 12.5MHz BW (10Msym/s) and different average  $P_{out}$ .

| P <sub>out,avg</sub> . | DE (%) |       | DAE     | (%)   | EVM (dB) |       |         |       |  |  |

|------------------------|--------|-------|---------|-------|----------|-------|---------|-------|--|--|

|                        |        |       | PAE (%) |       | 6.25MHz  |       | 12.5MHz |       |  |  |

|                        | Con.   | Set.2 | Con.    | Set.2 | Con.     | Set.2 | Con.    | Set.2 |  |  |

| 12.5dBm                | 37.6   | -     | 30      | -     | -35.6    | -     | -31.3   | _     |  |  |

| 7.5dBm                 | 14.8   | 29    | 11.3    | 17.9  | -33.4    | -36.1 | -30.3   | -31.5 |  |  |

| 2.5dBm                 | 4.2    | 10.1  | 3.7     | 6.3   | -32.1    | -35.9 | -30.1   | -31.2 |  |  |

output power which is lower than some other reported works. However, the outphasing theory and the back-off efficiency improvement approach described in the paper are not limited to a specific frequency or power level or technology: on purpose we (re)normalize voltages, power levels, impedances and use Smith chart representations to be as independent from frequency, power and technology as possible. Scaling our PA to achieve higher than 20.1dBm maximum output power levels in first order (ideally) has no impact on DE and PAE numbers [36]<sup>4</sup>. Section V.B already discussed the impact of the operating frequency on the merits of the efficiency enhancement technique.

All the measured efficiency numbers include the loss of the DC-feed inductor L (with Q=25), output bondwire inductance loss (1nH with Q=15), the loss of the off-chip inductor  $L_0$  (which has a series resistance  $0.5\Omega$ ) and the combiner loss (0.3dB). Therefore, replacing the PCB-based combiner with an on-chip transformer based counterpart will not considerably affect the efficiency [38]. Due to lack of relevant data in literature, we cannot benchmark the effect of the presented technique on  $V_{c,Max}$ . against the other efficiency improvement techniques.

# VIII. CONCLUSION

A simple analysis of the Outphasing class-E PAs (OEPAs) based on the load-pull analyses of the class-E PAs was given. The results of the study, then, further were used to rotate and shift the power contours and to rotate the efficiency contours to improve OEPAs performance and reliability aspects. Measurements in 65nm CMOS technology showed more than  $\times 2$  drain efficiency improvement at deep back-off for single tone excitation at 1.8GHz as well as for 7.6dB PAPR 12.5MHz 256QAM amplitude modulated signals.

Class-E PAs (and the outphasing systems that employ class-E PAs as the branch amplifiers) are tuned amplifiers and hence are optimized for narrow-band applications. However, measurement results across a wide frequency range 1.78GHz-1.88GHz showed that the presented technique can improve the OPDR to more than 34.8dB with at least 34% DE at 10dB back-off in this frequency range.

Fig. 12. Effect of changing d from 1 to 0.7 (a,b), respectively 1.2 (c,d) on the load-pull plots for q=1.3 and m=0. (a,c) Normalized output power (solid) and efficiency (dotted) contours. (c,d)  $V_{c,Max}$ , normalized to  $V_{DD}$  (solid) and normalized output voltage amplitude (dotted).

# APPENDIX A EFFECT OF CHANGING DUTY CYCLE ON THE LOAD-PULL CONTOURS

The effects of changing parameter d from 1 to 0.7, respectively to 1.2 on the load-pull contours are shown in Fig. 12; clockwise (anti-clockwise) rotation occurs for lower (higher) d. Note that the normalized maximum switch voltage as well as the normalized output voltage amplitude contours change with the rotation. This can potentially impact the OEPAs reliability and the OPDR which were taken into account in our efficiency improvement technique.

# APPENDIX B EXTENSION OF THE LOAD-PULL CONTOURS TOWARD NEGATIVE IMPEDANCES

The load-pull contours of a class-E PA with load-insensitive design, including negative impedances, are shown in Fig. 13. Outside the Smith chart, the real part of the load is negative and the direction of the output power is toward the switch (negative  $P_{out}$ ). Positive efficiencies ( $\eta > 100\%$ ) imply that the supply voltage  $V_{DD}$  sinks a fraction of the power that comes from the load (negative  $P_s$ ). Since the switch loss is always positive, then  $|P_s| < |P_{out}|$  which results in efficiencies more than 100%. Infinite efficiency shows that the whole power that comes from the load is dissipated in the switch and  $P_s = 0$ .

Negative efficiecies show that both the load power and the supply power are dissipated in the switch. Fig. 13, shows an intersection point where all the efficiency contours converge. At this point the load in open,  $P_{out}=0$ , there is no loss in the switch, which then results in  $P_s=0$ . Therefore, at this point the efficiency is not defined;  $\eta=\frac{P_{out}}{P_s}=\frac{0}{0}$ .

<sup>&</sup>lt;sup>4</sup>The matching network should also be adapted with the scaling; if a matching network with a higher quality factor were to be used to get higher output power (from a low-voltage PA), the Bode-Fano theorem [37] shows a limitation of the bandwidth. This is however a secondary effect, not inherent to the presented efficiency enhancement technique.

| TABLE II               |  |  |  |  |  |  |  |  |

|------------------------|--|--|--|--|--|--|--|--|

| PERFORMANCE COMPARISON |  |  |  |  |  |  |  |  |

|                                                         | [11]     | [12]        | [27]    | [29]      | [30]            |        | [31]    | [32]    | [33]     | This Work   |             |

|---------------------------------------------------------|----------|-------------|---------|-----------|-----------------|--------|---------|---------|----------|-------------|-------------|

| CMOS Technology                                         | 0.13(um) | 65(nm)      | 40(nm)  | 45(nm)    | 65(nm)          |        | 40(nm)  | 65(nm)  | 90(nm)   | 65(nm)      |             |

| Topology                                                | OEPA     | OEPA        | OEPA    | ODPA(e)   | Class-G+DLTM(f) |        | Doherty | Polar   | OBPA(j)  | OEPA        |             |

| Combiner                                                | On-chip  | Off-chip    | On-chip | Off-chip  | On-chip         |        | On-chip | On-chip | Off-chip | Off-chip    |             |

| Frequency (GHz)                                         | 1.85     | 2.4         | 5.9     | 0.9-2.4   | 2.4             |        | 1.9     | 2.4     | 0.9      | 1.8         |             |

| Supply (V)                                              | 2.8      | 2.5-0.85(a) | 1.2     | 1.2       | 2.8-1.55(g)     |        | 1.5     | 1.2     | 2.5      | 1.25        |             |

| P <sub>out,Max</sub> (dBm)                              | 29.7     | 27.7        | 22.2    | 25-25     | 24.6            |        | 28      | 22.8    | 20       | 20.1        |             |

| DE at Pout,Max                                          | 39.8     | NR(b)       | 49.2    | 60-52     | 39              |        | NR      | 46      | NR       | 65.3        |             |

| PAE at P <sub>out,Max</sub>                             | 36.9     | 45          | 34.9    | 55-45     | NR              |        | 34      | NR      | 56       | 60.7        |             |

| DE/PAE at 12dB                                          | NR       | NR          | <18(d)  | 20/14-    | 21.8            |        | NR      | NR      | NR       | 37.2        |             |

| back-off (%)                                            | /≈5(c)   | /<22(c)     | <13     | 12/8(c)   | /NR             |        | /19.7   | /NR     | /<20     | /22.1       |             |

| Signal                                                  | LTE      | OFDM        | 64QAM   | LTE       | 64QAM           | 256QAM | 16QAM   | 64QAM   | WCDMA    | 64QAM       | 256QAM      |

| (PAPR(dB))                                              | (7.5)    | (7.5)       | (7.2)   | (6)       | (7)             | (7.3)  | (8.36)  | (6.5)   | NR       | (7)         | (7.6)       |

| BW (MHz)                                                | 10       | 20          | 20      | 10-10     | NR(h)           | NR(i)  | 20      | 20      | 5        | 12.5/20     | 6.25/12.5   |

| Fractional BW (%)                                       | 0.54     | 0.83        | 0.34    | 1.11-0.42 | NR              | NR     | 1.05    | 0.83    | 0.55     | 0.7/1.11    | 0.35/0.7    |

| Pout,avg.(dBm)                                          | 24.7     | 20.2        | 16.4    | 18.9      | 17.6            | 17.3   | 23.4    | 16.8    | 13       | 13.1        | 12.5        |

| DE at Pout, avg.                                        | NR       | 31.9        | 23.3    | NR-NR     | 27.5            | 26.7   | NR      | 24.5    | NR       | 41.8        | 37.6        |

| PAE at Pout, avg.                                       | 20.8     | 27.6        | 16.1    | 32-22     | NR              | NR     | 23.3    | 19.3    | 30       | 33.6        | 30          |

| RMS EVM(dB)                                             | -30.5    | -31.3       | -30     | NR        | -25.6           | -30.4  | -23     | -28     | -16.6    | -30.9/-27.1 | -35.6/-31.3 |

| $\frac{V_{\rm cmax}}{V_{\rm DD}}$ at $P_{{ m out,Max}}$ | NR       | NR          | NR      | NR        | NR              |        | NR      | NR      | NR       | <3.3        |             |

| / 15dB back-off                                         | /NR      | /NR         | /NR     | /NR       | /NR             |        | /NR     | /NR     | /NR      | /<2.6       |             |

(a) Multi-level supply, (b) Not Reported, (c) obtained from publication figures, (d) DE=18% and PAE=13% at 9dB back-off, obtained from publication figures, (e) Outphasing class-D PA, (f) Dynamic Load Trajectory Manipulation, (g) full and half  $V_{DD}$  mode, (h) 20MSym/s reported symbol rate, (i) 10MSym/s reported symbol rate, (j) Outphasing class-B PA.

Fig. 13. Load-pull contours of a class-E PA with load-insensitive design and m=0. (a) Maximum switch voltage normalized to  $V_{DD}$  (solid) and normalized output voltage amplitude (dotted), (b) normalized output power (solid) and efficiency (dotted) contours.

#### REFERENCES

- [1] F.H. Raab, "Idealized operation of the class-E tuned power amplifier," in *Circuits and Systems, IEEE Transactions on*, vol. 24, no. 12, pp. 725-735, Dec. 1977.

- [2] S. C. Cripps, "RF Power Amplifiers for Wireless Communications," Norwood, MA: Artech House, pp. 113-143, 219-249.

- [3] R. Beltran, F. H. Raab and A. Velazquez, "HF outphasing transmitter using class-E power amplifiers," in *IEEE MTT-S International Microwave Symposium Digest*, 2009, pp. 757-760.

- [4] N. O. Sokal and A. D. Sokal, "Class E-A new class of high-efficiency tuned single-ended switching power amplifiers," in *IEEE Journal of Solid-State Circuits*, vol. 10, no. 3, pp. 168-176, June 1975.

- [5] M. P. van der Heijden, M. Acar, J. S. Vromans and D. A. Calvillo-Cortes, "A 19W high-efficiency wide-band CMOS-GaN class-E Chireix RF outphasing power amplifier," 2011 IEEE MTT-S International Microwave Symposium, Baltimore, MD, 2011, pp. 1-4.

- [6] R. Sadeghpour, A. Nabavi, "Design Procedure of Quasi-Class-E Power Amplifier for Low-Breakdown-Voltage Devices," Circuits and Systems I: Regular Papers, IEEE Transactions on, vol. 61, no. 5, pp. 1416-1428, May 2014.

- [7] A. Ghahremani, A. J. Annema and B. Nauta, "A 20dBm outphasing class E PA with high efficiency at power back-off in 65nm CMOS technology,"

- in IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2017, pp. 340-343.

- [8] I. Aoki, S. Kee, R. Magoon, R. Aparicio, F. Bohn, J. Zachan, G. Hatcher, D. McClymont and A. Hajimiri, "A Fully-Integrated Quad-Band GSM/GPRS CMOS Power Amplifier," Solid-State Circuits, IEEE Journal of, vol. 43, no. 12, pp. 2747-2758, Dec. 2008.

- [9] M. Ozen, M. van der Heijden, M. Acar, R. Jos and C. Fager, "A Generalized Combiner Synthesis Technique for Class-E Outphasing Transmitters," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 64, no. 5, pp. 1126-1139, May 2017.

[10] N. Singhal, H. Zhang and S. Pamarti, "A Zero-Voltage-Switching

- [10] N. Singhal, H. Zhang and S. Pamarti, "A Zero-Voltage-Switching Contour-Based Outphasing Power Amplifier," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 60, no. 6, pp. 1896-1906, June 2012

- [11] S. Shim and S. Pamarti, "A 1.85GHz CMOS power amplifier with zero-voltage-switching contour-based outphasing control to improve back-off efficiency," 2015 IEEE MTT-S International Microwave Symposium, Phoenix, AZ, 2015, pp. 1-4.

- [12] P. A. Godoy, S. Chung, T. W. Barton, D. J. Perreault and J. L. Dawson, "A 2.4-GHz, 27-dBm Asymmetric Multilevel Outphasing Power Amplifier in 65-nm CMOS," in *IEEE Journal of Solid-State Circuits*, vol. 47, no. 10, pp. 2372-2384, Oct. 2012.

- [13] J. Qureshi, R. Liu, A. J. M. de Graauw, M. P. van der Heijden, J. Gajadharsing and L. C. N. de Vreede, "A highly efficient chireix amplifier using adaptive power combining," in *IEEE MTT-S International Microwave Symposium Digest*, 2008, pp. 759-762.

- [14] D. J. Perreault, A New Power Combining and Outphasing Modulation System for High-Efficiency Power Amplification, in *IEEE Trans. on Circuits and Systems I: Regular Papers*, vol. 58, no. 11, Aug. 2011.

- [15] M. P. van der Heijden and M. Acar, A Radio-Frequency Reconfigurable CMOS-GaN Class-E Chireix Power Amplifier, IEEE MTT-S Intl. Microwave Symp. Digest, June 2014.

- [16] 3GPP TS 36.101 V14.3.0, "Evolved Universal Terrestrial Radio Access (E-UTRA); User Equipment (UE) radio transmission and reception", April 2017.

- [17] H. Wang et al., "A Highly-Efficient Multi-Band Multi-Mode All-Digital Quadrature Transmitter," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 61, no. 5, pp. 1321-1330, May 2014.

- [18] H. S. Chen, Y. K. Hsieh and L. H. Lu, "A 5.5-GHz multi-mode power amplifier with reconfigurable output matching network," 2015 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Phoenix, AZ, 2015, pp. 203-206.

- [19] N. Singhal, N. Nidhi, R. Patel and S. Pamarti, "A Zero-Voltage-Switching Contour-Based Power Amplifier With Minimal Efficiency Degradation Under Back-Off," in IEEE Transactions on Microwave Theory and Techniques, vol. 59, no. 6, pp. 1589-1598, June 2011.

- [20] M. Ozen, R. Jos, C. M. Andersson, M. Acar and C. Fager, "High-Efficiency RF Pulsewidth Modulation of Class-E Power Amplifiers," in IEEE Transactions on Microwave Theory and Techniques, vol. 59, no. 11, pp. 2931-2942, Nov. 2011.

- [21] M. Acar, A.J. Annema, B. Nauta, "Analytical Design Equations for Class-E Power Amplifiers," Circuits and Systems I: Regular Papers, IEEE Transactions on, vol. 54, no. 12, pp. 2706-2717, Dec. 2007.

- [22] R. A. Beltran and F. H. Raab, "Simplified analysis and design of outphasing transmitters using class-E power amplifiers," 2015 IEEE Topical Conference on Power Amplifiers for Wireless and Radio Applications (PAWR), San Diego, CA, 2015, pp. 1-3.

- [23] K. Tom and M. Faulkner, "Load pull methodology to characterise class-E outphasing power amplifiers," in IET Microwaves, Antennas and Propagation, vol. 6, no. 4, pp. 387-392, March 20 2012.

- [24] R. Zhang, M. Acar, M. P. van der Heijden, M. Apostolidou and D. M. W. Leenaerts, "Generalized Semi-Analytical Design Methodology of Class-E Outphasing Power Amplifier," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 61, no. 10, pp. 2951-2960, Oct. 2014.

- [25] M. Acar, A. J. Annema and B. Nauta, "Variable-Voltage Class-E Power Amplifiers," in *IEEE MTT-S International Microwave Symposium*, 2007, pp. 1095-1098.

- [26] M. Acar, A. J. Annema and B. Nauta, "Generalized Analytical Design Equations for Variable Slope Class-E Power Amplifiers," in *IEEE International Conference on Electronics, Circuits and Systems*, 2006, pp. 431-434.

- [27] Z. Hu, L. C. N. de Vreede, M. S. Alavi, D. A. Calvillo-Cortes, R. B. Staszewski and S. He, "A 5.9 GHz RFDAC-based outphasing power amplifier in 40-nm CMOS with 49.2% efficiency and 22.2 dBm power," in *IEEE Radio Frequency Integrated Circuits Symposium (RFIC)*, 2016, pp. 206-209.

- [28] O. Lee et al., "A Charging Acceleration Technique for Highly Efficient Cascode Class-E CMOS Power Amplifiers," in *IEEE Journal of Solid-State Circuits*, vol. 45, no. 10, pp. 2184-2197, Oct. 2010.

- [29] L. Ding, J. Hur, A. Banerjee, R. Hezar and B. Haroun, "A 25 dBm Outphasing Power Amplifier With Cross-Bridge Combiners," in *IEEE Journal of Solid-State Circuits*, vol. 50, no. 5, pp. 1107-1116, May 2015.

- [30] S. Hu, S. Kousai and H. Wang, "A Compact Broadband Mixed-Signal Power Amplifier in Bulk CMOS With Hybrid Class-G and Dynamic Load Trajectory Manipulation," in *IEEE Journal of Solid-State Circuits*, vol. 52, no. 6, pp. 1463-1478, June 2017.

- [31] E. Kaymaksut and P. Reynaert, "Dual-Mode CMOS Doherty LTE Power Amplifier With Symmetric Hybrid Transformer," in *IEEE Journal of Solid-State Circuits*, vol. 50, no. 9, pp. 1974-1987, Sept. 2015.

- [32] L. Ye, J. Chen, L. Kong, P. Cathelin, E. Alon and A. Niknejad, "A digitally modulated 2.4GHz WLAN transmitter with integrated phase path and dynamic load modulation in 65nm CMOS," in *IEEE International* Solid-State Circuits Conference Digest of Technical Papers, 2013, pp. 330-331.

- [33] S. Moloudi and A. Abidi, The Outphasing RF Power Amplifier: A Comprehensive Analysis and a Class-B CMOS Realization, in *IEEE Journal of Solid-State Circuits*, vol. 48, no. 6, pp. 13571369, June 2013.

- [34] J. H. Qureshi et al., "A 90-W Peak Power GaN Outphasing Amplifier With Optimum Input Signal Conditioning," in IEEE Transactions on Microwave Theory and Techniques, vol. 57, no. 8, pp. 1925-1935, Aug. 2009.

- [35] M. C. A. van Schie, M. P. van der Heijden, M. Acar, A. J. M. de Graauw and L. C. N. de Vreede, "Analysis and design of a wideband high efficiency CMOS outphasing amplifier," 2010 IEEE Radio Frequency Integrated Circuits Symposium, Anaheim, CA, 2010, pp. 399-402.

- [36] M. Acar et. al, Scalable CMOS Power Devices with 70% PAE and 1, 2 and 3.4 W Output Power at 2GHz, RFIC Symp., pp. 233-236, June 2009.

- [37] R. M. Fano, "Theoretical limitations on the broadband matching of arbitrary impedances," J. Franklin Inst., vol. 249, pp. 57-83, 139-155, Ian /Feb. 1950.

- [38] Jongchan Kang, A. Hajimiri and Bumman Kim, "A single-chip linear CMOS power amplifier for 2.4 GHz WLAN," 2006 IEEE International Solid State Circuits Conference - Digest of Technical Papers, San Francisco, CA, 2006, pp. 761-769.

Ali Ghahremani received the B.Sc. and M.Sc. degrees in electrical engineering from Sharif University of Technology, Tehran, Iran, in 2009 and 2012, respectively. He is currently working on his Ph.D. with the ICD group at University of Twente. His general research interests include high speed and low power CMOS analog circuits and power amplifiers for RF applications.

Mr. Ghahremani was ranked third in the 2009 Iranian Student Scientific Olympiad on Electrical Engineering, Honored by Ministry of Science.

Anne-Johan Annema received the M.Sc. degree in electrical engineering and the Ph.D. degree from the University of Twente, Enschede, The Netherlands, in 1990 and 1994, respectively. In 1995, he joined the Semiconductor Device Architecture Department of Philips Research in Eindhoven, The Netherlands, where he worked on a number of physics-electronics-related projects. In 1997, he joined the Mixed-Signal Circuits and Systems Department at Philips NatLab, where he worked on a number of electronics-physics-related projects ranging from

low-power low-voltage circuits, fundamental limits on analog circuits related to with process technologies, high-voltage in baseline CMOS to feasibility research of future CMOS processes for analog circuits. Since 2000 he is with the IC-Design group in the department of Electrical Engineering at the University of Twente, Enschede, The Netherlands. His current research interest is in physics, analog and mixed-signal electronics, and deepsubmicrometer technologies and their joint feasibility aspects. He is also part-time consultant in industry, co-founded ChipDesignWorks and is the recipient of four educational award at the University of Twente.

Bram Nauta was born in 1964 in Hengelo, The Netherlands. In 1987 he received the M.Sc degree (cum laude) in electrical engineering from the University of Twente, Enschede, The Netherlands. In 1991 he received the Ph.D. degree from the same university on the subject of analog CMOS filters for very high frequencies. In 1991 he joined the Mixed-Signal Circuits and Systems Department of Philips Research, Eindhoven the Netherlands. In 1998 he returned to the University of Twente, where he is currently a distinguished professor, heading the IC

Design group. Since 2016 he serves as chair of the EE department. His current research interest is high-speed analog CMOS circuits, software defined radio, cognitive radio and beamforming.

He served as the Editor-in-Chief (2007-2010) of the IEEE Journal of Solid-State Circuits (JSSC), and was the 2013 program chair of the International Solid State Circuits Conference (ISSCC). He is currently the President elect of the IEEE Solid-State Circuits Society.

Also, he served as Associate Editor of IEEE Transactions on Circuits and Systems II (1997-1999), and of JSSC (2001-2006). He was in the Technical Program Committee of the Symposium on VLSI circuits (2009-2013) and is in the steering committee and programme committee of the European Solid State Circuit Conference (ESSCIRC). He served as distinguished lecturer of the IEEE, is co-recipient of the ISSCC 2002 and 2009 "Van Vessem Outstanding Paper Award" and in 2014 he received the Simon Stevin Meester award (500.000), the largest Dutch national prize for achievements in technical sciences. He is fellow of the IEEE and member of the Royal Netherlands Academy of Arts and Sciences (KNAW)