# Model-based Application Development for Massively Parallel Embedded Systems

#### Members of the dissertation committee:

| -             | G.J.M. Smit    | University of Twente (promoter)               |

|---------------|----------------|-----------------------------------------------|

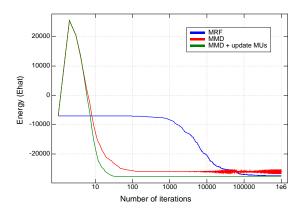

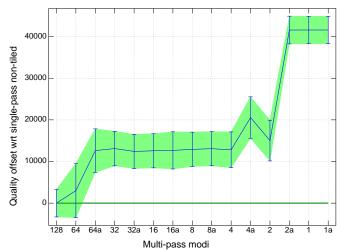

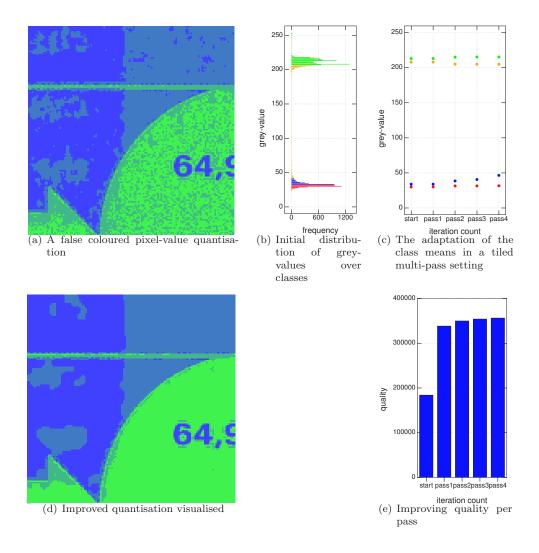

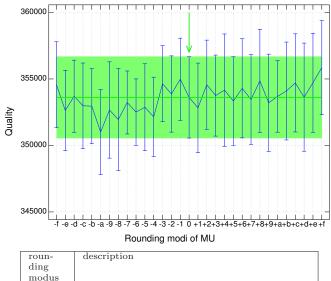

| dr. ir.       | J. Kuper       | University of Twente (assistent-promoter)     |

| prof. dr. ir. | Th. Krol       | University of Twente                          |

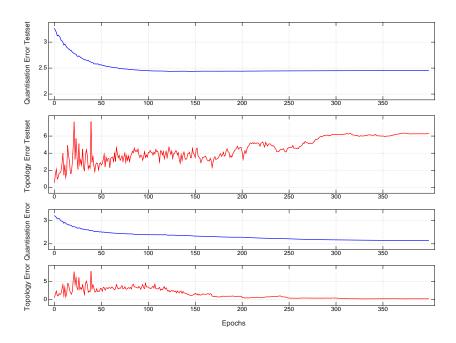

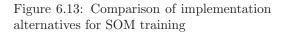

| prof. dr. ir. | M. Aksit       | University of Twente                          |

| prof. dr.     | H. Corporaal   | University of Eindhoven                       |

| ir.           | P.G. Jansen    | University of Twente                          |

| dr. ir.       | P.J. Mosterman | The MathWorks, Inc.                           |

| prof. dr. ir. | A.J. Mouthaan  | University of Twente (chairman and secretary) |

CTIT Ph.D. thesis Series No. 08-132 Centre for Telematics and Information Technology (CTIT) P.O. Box 217 - 7500 AE Enschede - The netherlands

Copyright © 2008 by Jan W.M. Jacobs, Kessel, The Netherlands.

Cover photo: Jan Beckers, Venlo, The Netherlands. Cover design: Jos Kerkhoffs, Steijl, The Netherlands.

All rights reserved. No part of this book may be reproduced or transmitted, in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage or retrieval system, without the prior written permission of the author.

Typeset with LATEX.

Printed by Océ Technologies BV, Venlo, The Netherlands.

ISBN 978-90-365-2752-1

ISSN 1381-3617 (CTIT Ph.D.-THESIS SERIES NO. 08-132)

# MODEL-BASED APPLICATION DEVELOPMENT FOR MASSIVELY PARALLEL EMBEDDED SYSTEMS

#### DISSERTATION

to obtain

the doctor's degree at the University of Twente,

on the authority of the rector magnificus,

prof. dr. W.H.M. Zijm,

on account of the decision of the graduation committee,

to be publicly defended

on Thursday, November 20, 2008 at 16.45

by

Johannes Wilhelmus Maria Jacobs

born on 30 April 1955, in Kessel (LB), The Netherlands This dissertation is approved by:

$\begin{array}{cccc} prof. \; dr. \; ir. & G.J.M. \; Smit & (promoter) & \quad and \\ dr. \; ir. & J. \; Kuper & (assistant-promoter) & \end{array}$

The development of embedded systems in information-rich contexts is governed by some intertwined trends. The increase of both volume of data to be processed and the related processing functionality feeds the growing complexity of applications. Independently, the processing hardware that is needed to process these applications, is becoming increasingly parallel and heterogeneous (many-core) because of performance and power problems. Furthermore, today's compiler technology is not able to translate sequential legacy code for multi-core or many-core systems in an efficient way.

This thesis addresses the problem of generating efficient code for a number of cores, that operate synchronously. Examples are Single Instruction Multiple Data (SIMD) and Very Long Instruction Word (VLIW) architectures. In this thesis we restrict ourselves to architectures that include a control processor that provides the instruction stream.

In practice the manufacturers of such many-core processors only provide a C-compiler that supports hardware intrinsic instructions. This situation usually requires manual adaptation of sequential code. Unfortunately, a first feedback of the implementation on the targeted parallel architecture only comes late in the development trajectory. Moreover, during implementation phases more engineers enter the project and this increases the risk of early errors proliferating to later phases. Although some parts of the system can be modelled in high level language(s) (e.g., MATLAB), the typical approach lacks a single integral and executable framework allowing for an immediate system-wide verification.

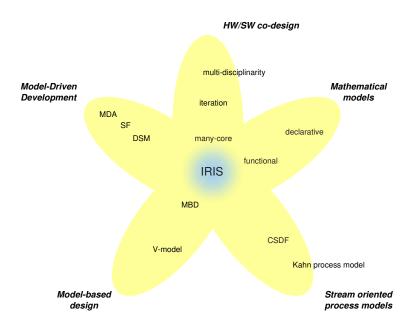

This thesis proposes an integral design methodology, named IRIS, for the development of firmware for many-core architectures.

The methodology is illustrated by three cases: a colour image processing pipeline for a printer, stochastic image quantisation, and data mining of dynamic document spaces. For the three cases the various development phases and the associated development roles result in mathematical models, that can be directly

transcribed in a functional language. The executable models are subsequently transformed into a series of implementation models, that converge to the targeted many-core implementation.

This thesis contains the following contributions:

First, all three cases showed that for an effective and efficient implementation of applications on a massively parallel processing architecture it is necessary to manually (re)model the problem in a suitable parallel representation.

Second, a semi-automatic and interactive development process is needed for mapping an application on a dedicated massively parallel processing core.

Third, the three cases demonstrate that a single architectural language – firmly based on mathematics – for all development phases, reduces development time and reduces the number of design errors.

Fourth, it is shown that the relevant extra-functional requirements can be handled by integrating them into the regular functional flow. As a consequence the architectural language should support *in situ* monitoring and visualisation of quantifiable extra-functional properties.

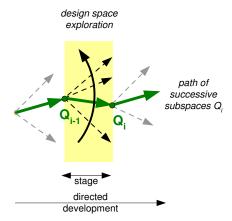

Fifth, in the development process small steps and immediate feedback are crucial as demonstrated by the various performed iterations (optimisations, correction of errors) and the involved design space explorations.

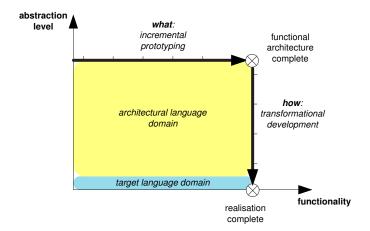

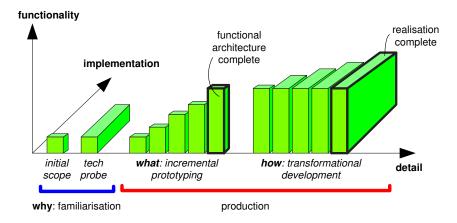

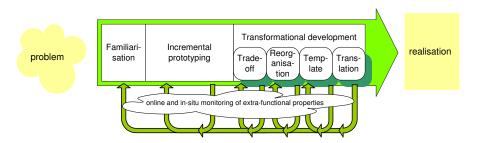

Sixth, it is shown that a development process having a phased approach works very well. This should subsequently include:

- 1. a familiarisation phase with respect to the problem and the target hardware architecture(s),

- 2. an incremental prototyping phase (hardware architecture independent), and

- a transformational development phase (hardware architecture dependent),

which are performed in an iterative manner when needed.

| 1 |                                       |

|---|---------------------------------------|

| 1 | · · · · · · · · · · · · · · · · · · · |

| 1 | · · · · · · · · · · · · · · · · · · · |

| 1 | · · · · · · · · · · · · · · · · · · · |

| 1 | · · · · · · · · · · · · · · · · · · · |

| 1 |                                       |

| 1 |                                       |

| 1 |                                       |

| 1 | <b>~</b>                              |

| 1 | Component time                        |

| 1 | Samenvatting                          |

|   |                                       |

De ontwikkeling van embedded systemen in informatie-intensieve omgevingen wordt bepaald door enkele met elkaar verbonden trends. De groei van zowel volume van data alsook de gerelateerde processing funktionaliteit, voeden de groeiende komplexiteit van applikaties. Onafhankelijk daarvan ontwikkelt de voor de applikaties benodigde processing hardware zich vanwege prestatie en vermogen steeds meer in de richting van meerdere parallelle en heterogene cores. Daar komt nog bij dat de huidige compiler-technologie niet geschikt is om de bestaande sequentiële source code te vertalen in een efficiënte implementatie voor multi- of many-core systemen.

Dit proefschrift gaat over het probleem van de generatie van efficiënte code voor een aantal cores die synchroon samenwerken. Voorbeelden zijn Single Instruction Multiple Data (SIMD) en Very Long Instruction Word (VLIW) architekturen. In dit proefschrift beperken we ons tot architekturen die een besturingsprocessor hebben voor de benodigde instruktie-stroom.

In de praktijk leveren de producenten van dergelijke many-core processoren slechts een C-compiler die hardware-afhankelijke instrukties ondersteunt. Deze situatie vereist gewoonlijk een handmatige aanpassing van de sequentiële code. In deze aanpak is het echter pas op een laat tijdstip mogelijk om een eerste terugkoppeling te geven over de implementatie op de beoogde parallelle hardware architektuur. Bovendien neemt gedurende de implementatie-fase de instroom van engineers in het projekt toe en dit verhoogt het risiko van de proliferatie van vroege fouten naar latere fasen. Ofschoon delen van het systeem kunnen worden gemodelleerd in een hoog-nivo taal (b.v. MATLAB), ontbeert de typische aanpak toch een integraal en executeerbaar raamwerk dat een instantane systeem-brede verifikatie mogelijk maakt.

Dit proefschrift levert een integrale ontwerp-methodologie, genaamd IRIS, voor de ontwikkeling van firmware voor many-core architekturen.

De methodologie wordt geïllustreerd door drie praktijkvoorbeelden: een beeld-

verwerkingspipeline voor een kleurenprinter, stochastische beeldkwantisatie, en data mining van dynamische dokumentkollekties. De diverse ontwikkelfasen en hun overeenkomstige ontwikkelrollen resulteren voor al deze drie praktijk-voorbeelden in wiskundige modellen, die op hun beurt direkt kunnen worden overgezet in een funktionele taal. Deze uitvoerbare modellen worden achtereenvolgens omgezet in een reeks implementatie-modellen, die uiteindelijk konvergeren naar de beoogde many-core implementatie.

Het proefschrift bevat de volgende bijdragen:

Ten eerste, alle drie praktijkvoorbeelden laten zien dat het noodzakelijk is om het probleem met de hand te (her)modelleren in een geschikte parallelle representatie, ten einde een effektieve en efficiënte implementatie van de toepassing op een massief-parallel verwerkingsarchitektuur te verkrijgen.

Ten tweede, voor het afbeelden van een toepassing op een specifieke massiefparallelle verwerkingskern is een semi-automatisch en interactief ontwikkelproces nodig.

Ten derde, de drie praktijkvoorbeelden demonstreren dat voor alle ontwikkelfasen, een enkele architektuurtaal – direkt gebaseerd op de wiskunde – zowel de ontwikkeltijd alsook het aantal gemaakte ontwerpfouten terugbrengt.

Ten vierde wordt aangetoond dat de relevante extra-funktionele eisen kunnen worden afgehandeld door deze te integreren in de reguliere funktionele beschrijving. Een direkt gevolg hiervan is dat de architektuurtaal de *in situ* monitoring and visualisatie van meetbare extra-funktionele eigenschappen moet ondersteunen.

Ten vijfde, in het ontwikkelproces zijn het maken van klein stappen en instantane terugkoppeling van cruciaal belang zoals gedemonstreerd door de verscheidene uitgevoerde iteraties (optimalisaties, korrekties van fouten) en de betrokken verkenning van de ontwerpruimte.

Tenslotte wordt aangetoond dat een gefaseerde aanpak van het ontwikkelproces goed werkt. De fasen zijn achtereenvolgens:

- 1. een kennismakingsfase aangaande het probleem en de beoogde hardware architektu(u)r(en),

- 2. een incrementele prototyping fase (hardware-architektuur onafhankelijk), en

- 3. een transformationele ontwikkelfase (hardware-architektuur afhankelijk).

De fasen worden naar behoefte op een iteratieve wijze uitgevoerd.

| Acknowledgements |

|------------------|

Each end goes with a begin. The start of this enterprise was laid during my study at the Technische Hogeschool Eindhoven (TUE); it seemed to be quite a nice challenge to also become a "doctor" one time. Never give up your dreams!

During the development of microcode for the first commercial laserprinter of Océ in the mid 80s, unknowingly a first step was made in the selection of a theme (a methodology) for this PhD. This work was conducted together with Roger Hacking. Roger, thanks for your support.

One of the next steps was the selection of a suitable research group and professor, and mid 90s I met Thijs Krol at the University of Twente (UT). Although the meeting did not result in concrete plans, it led to the right scientific place and a free meal in the Bastille. Thijs, thanks for the good advice.

It was for Roelof Hamberg, that achieving a doctor's degree – as part of a liaison assignment with the UT – became a topic within Océ. Roelof, many thanks for your belief in me. I learned that communication of one's dreams is necessary before any strategic enterprise can start!

Now, almost at the end of this enterprise, I want to express my gratitude to Gerard Smit and Jan Kuper. Gerard's constant commitment, notably the conscientiously reviewing of texts (papers, thesis) leading to to-the-point criticism and – most of all – the encouraging way of coaching, made my PhD study both a challenging and a rewarding process. Jan showed me how to (re)model a problem in such a way that its mathematical description can be elegantly transcribed in a functional language. From him I also painfully learned never to bet with a mathematician. Gerard and Jan form a good complementary team in which global as well as more detailed concerns balance well.

The foundation of the work on IRIS are the three application cases. The cases could not have been conducted successfully without the assistance of Winston Bond (Aspex) and master students Rui Dai (University of Singapore) and Leroy van Engelen (UT). Winston, Rui and Leroy, thank you very much for your effort

and the many extra hours you have spent in analysing, designing and coding in Aspro-C and in the 'dreadful' J language! Roel Pouls, Samuel Driessen and Zoé Goey provided me real challenging problem cases, and gave constructive feedback on the quality of the work. Roel, thanks for introducing me into and guiding through the world of productive image processing for a colour printer and Field Programmable Gate Array (FPGA) based system design. Zoé, thank you very much for the attentive guidance through Markov Random Fields and the various critical remarks on the involved mathematical modeling. Samuel, your help in the world of natural language processing, data mining and knowledge discovery for news articles is very much appreciated. A lot of people supported the work on the cases in a direct way. I want to thank (in arbitrary order): Stuart Cornell (Aspex), Sebastian de Smet, Jos Nelissen, Rob Audenaerde, Harold van Garderen, Andras Zolnay and Anjo Anjewierden (VU) for their contribution.

A very special word of thanks goes to Klaas Kuin, for guiding me through the rough waters of writing a thesis. His typical way of giving constructive critism on one hand and offering opportunities for me to discover in the other, not only helped me finishing this work in time but also provided me with wise lessons for my future life. Klaas, thank you for your coaching.

Co-readers are appreciated, in particular when massive amounts of English-like (euphemism) texts are being generated. I want to thank the following people for proofreading and other kinds of support: Marco Krom, Lou Somers, Herman Driessen, Jos Kerkhoffs, Jack van der Elsen, Waldo Ruiterman, Aart van Meeteren, Jorrit Buurman, Kees-Jan Sonnenberg, Dion Slijp and Paul Verhelst.

You never work alone, and the following persons provided me with social context. First I want to express my thanks to Rob van den Tillaart for the many techno-philosophical and creative discussions (and U-memos) and Joost Meijer for the many exciting applied AI thoughts that were exchanged. You both provided me with an enjoyable research context. Thanks also to Juri Snijders, Eric Dortmans, Jan Beckers, Mechlin Pelders, Rokus Visser, Peter van den Bosch, Bart Verheijen, Matthijs Mullender, Dirk Schäfer, Rogier de Blok, Guus Muisers and Josse van der Plaat. Furthermore the advise of the young but experienced 'flying doctors' Jaap de Jong, Aico Troeman and Bart van As was very comforting. Thank you all for being my roommates in Venlo!

Once a week I visit Twente, where I am lucky to be part of a pleasant social matrix too. I want to thank Andre Kokkeler, Gerard Rauwerda, Bert Molenkamp, Hans Scholten, Paul Havinga, Berend-Jan van der Zwaag, Pascal Wolkotte, Philip Hölzenspies and all other staff-members, AIOs and Master students of the UT/EWI CAES group (too many to mention them all) for providing a challenging but at the same time comforting environment.

I also want to thank Marlous Weghorst, Nicole Baveld and Thelma Nordholt and their Venlo counterparts Petra van der Heijden and Bianca Meijers for all the secretarial work. You are the real motors in organisations, many thanks for your support.

This enterprise could not end successfully without the unconditional support

of my family. I want to thank my parents for their continuous support for my personal development. I want to thank my children, Marcia and Jorn, and Robert for their love and understanding, in particular the many times that my thoughts drifted away during the very scarce moments we were together. But most of all, I want to thank my wife Marja for all her love, understanding and patience with my peculiar way of being. Marja, you not only tolerated my frequent absence but also took over a lot of my domestic duties, despite your own full time job. Without you I would never have accomplished this work.

# \_\_\_\_TABLE OF CONTENTS

| T        | Intr | oduction                                                                                                                                           | T |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|---|

|          | 1.1  | Introduction                                                                                                                                       | 1 |

|          | 1.2  | Document processing in a changing world                                                                                                            | 2 |

|          |      |                                                                                                                                                    | 2 |

|          |      | 1.2.2 Trends                                                                                                                                       | 4 |

|          |      |                                                                                                                                                    | 6 |

|          | 1.3  |                                                                                                                                                    | 9 |

|          |      |                                                                                                                                                    | 9 |

|          |      | 1.3.2 Contribution                                                                                                                                 | 9 |

|          | 1.4  | Thesis outline                                                                                                                                     | 0 |

|          |      |                                                                                                                                                    |   |

| <b>2</b> | Stat | e of the Art Massively Parallel Embedded Architectures 1                                                                                           | 1 |

|          | 2.1  | $Introduction \dots \dots$                   | 2 |

|          |      | 2.1.1 Streaming Applications                                                                                                                       | 2 |

|          |      | 2.1.2 Many-core Architectures                                                                                                                      | 3 |

|          | 2.2  | Classification                                                                                                                                     | 6 |

|          | 2.3  | Sample architectures                                                                                                                               | 8 |

|          |      | 2.3.1 Montium Reconfigurable Processing Core                                                                                                       | 8 |

|          |      | 2.3.2 PACT-XPP                                                                                                                                     | 1 |

|          |      | 2.3.3 Tilera                                                                                                                                       | 3 |

|          |      | 2.3.4 Linedancer                                                                                                                                   | 5 |

|          | 2.4  | Conclusion                                                                                                                                         | 9 |

| 3        | The  | IRIS Firmware Design Methodology 3                                                                                                                 | 1 |

|          | 3.1  | Introduction                                                                                                                                       | 1 |

|          | 3.2  | State of the Art Methodologies $\dots \dots \dots$ | 5 |

|          |      | 3.2.1 Multi-disciplinary aspect                                                                                                                    | 5 |

|   |      | 3.2.2   | Iterative aspect                            |

|---|------|---------|---------------------------------------------|

|   |      | 3.2.3   | Software economics                          |

|   |      | 3.2.4   | Many-core developments                      |

|   |      | 3.2.5   | Model-based design                          |

|   | 3.3  | Model   | -Based Design as a basis for IRIS           |

|   |      | 3.3.1   | Extending Model-Based Design                |

|   |      | 3.3.2   | Remaining problems                          |

|   | 3.4  | Startin | ng points of IRIS                           |

|   | 3.5  | The II  | RIS methodology                             |

|   |      | 3.5.1   | Overview                                    |

|   |      | 3.5.2   | Architectural language                      |

|   | 3.6  | Phase   | I: Familiarisation                          |

|   | 3.7  | Phase   | II: Incremental Prototyping                 |

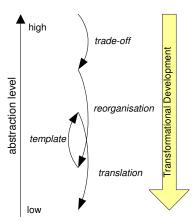

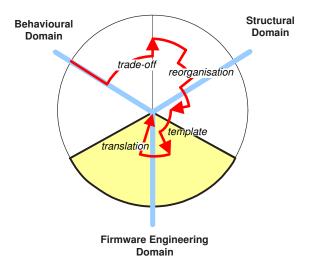

|   | 3.8  | Phase   | III: Transformational Development           |

|   |      | 3.8.1   | Trade-off Subphase                          |

|   |      | 3.8.2   | Reorganisation Subphase                     |

|   |      | 3.8.3   | Template Subphase                           |

|   |      | 3.8.4   | Translation Subphase                        |

|   | 3.9  | Summ    | ary                                         |

|   | 3.10 | Conclu  | asions                                      |

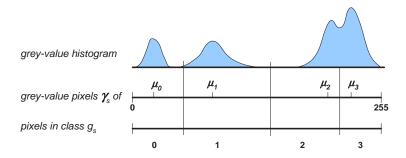

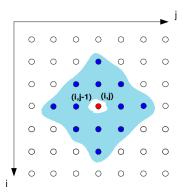

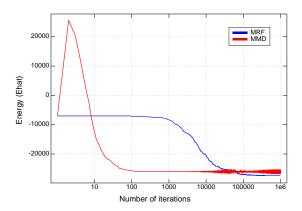

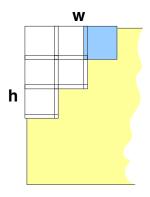

| 4 | Cas  | e: Sto  | chastic Image Quantisation 63               |

|   | 4.1  |         | uction                                      |

|   | 4.2  |         | arisation                                   |

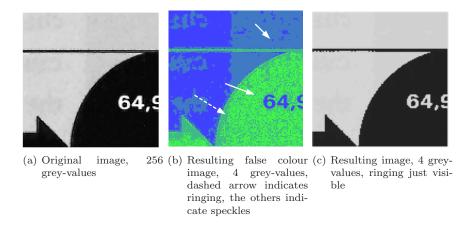

|   |      | 4.2.1   | Business Graphics and Image Quantisation 64 |

|   |      | 4.2.2   | Stochastic Image Quantisation               |

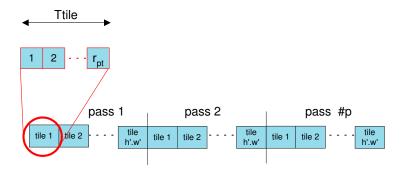

|   |      | 4.2.3   | Tiling                                      |

|   |      | 4.2.4   | Feasibility                                 |

|   | 4.3  | Incren  | nental Prototyping                          |

|   |      | 4.3.1   | The algorithm                               |

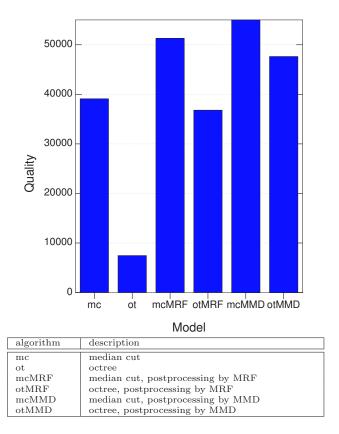

|   |      | 4.3.2   | Quality function                            |

|   |      | 4.3.3   | Quantisation methods                        |

|   |      | 4.3.4   | Iteration count                             |

|   | 4.4  | Transf  | formational Development                     |

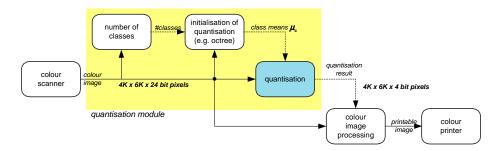

|   |      | 4.4.1   | Global system considerations 81             |

|   |      | 4.4.2   | Trade-off subphase                          |

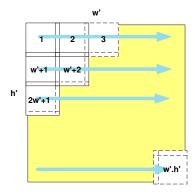

|   |      | 4.4.3   | Reorganisation subphase                     |

|   |      | 4.4.4   | Template subphase                           |

|   |      | 4.4.5   | Translation subphase                        |

|   | 4.5  | Result  | s and Discussion                            |

|   | 4.6  | Conclu  | isions 100                                  |

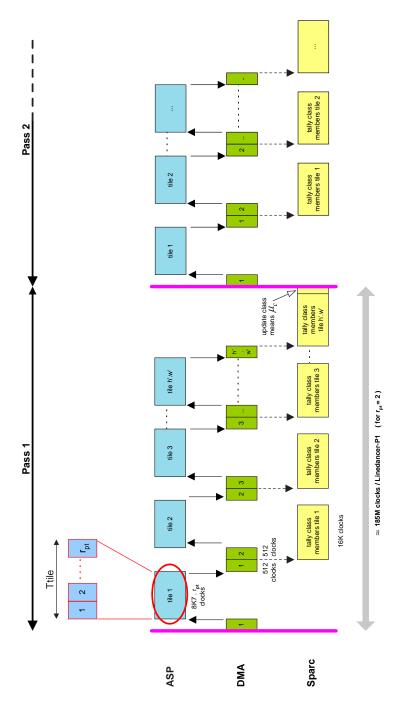

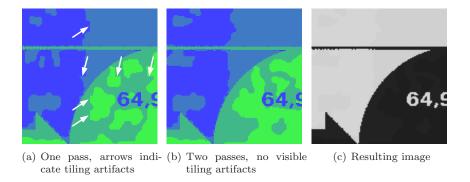

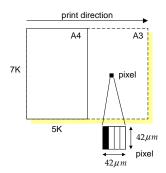

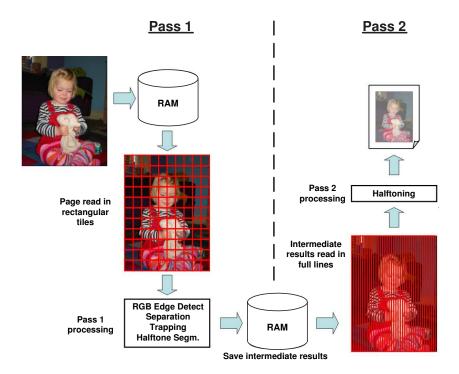

| 5 | Cas | e: Colour Image Processing 1                 | 11  |

|---|-----|----------------------------------------------|-----|

|   | 5.1 | Introduction                                 | 11  |

|   | 5.2 | Familiarisation                              | 12  |

|   |     | 5.2.1 Colour Printing Process                | 12  |

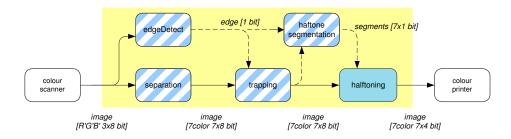

|   |     | 5.2.2 Colour Image Processing Pipeline       | 14  |

|   |     | 5.2.3 Feasibility                            | 23  |

|   | 5.3 | Incremental Prototyping                      | 26  |

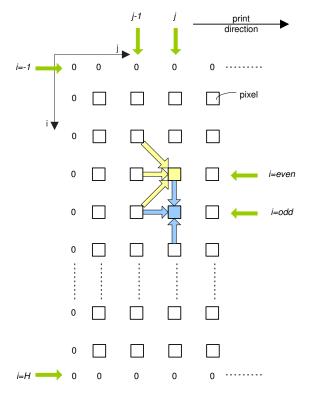

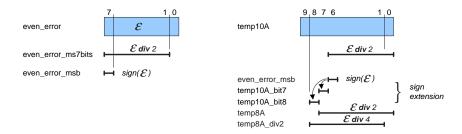

|   |     | 5.3.1 Half-toning Algorithm: Error Diffusion | 26  |

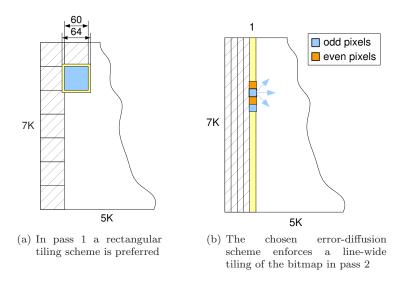

|   |     | 5.3.2 Implementation independent aspects     | 28  |

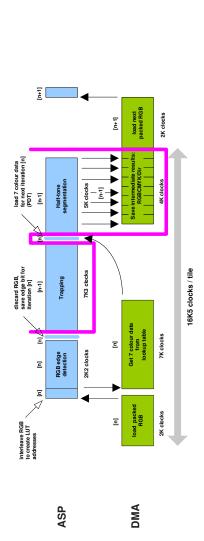

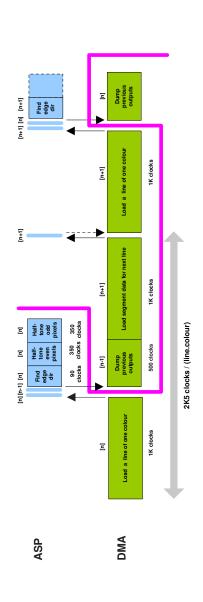

|   | 5.4 | Transformational Development                 | 30  |

|   |     | 5.4.1 Global system considerations           | 30  |

|   |     | 5.4.2 Trade-off subphase                     | 32  |

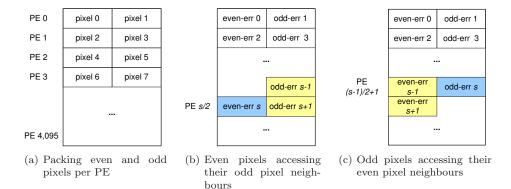

|   |     | 5.4.3 Reorganisation subphase                | 32  |

|   |     | 5.4.4 Template subphase                      | 35  |

|   |     | 5.4.5 Translation subphase                   | 37  |

|   | 5.5 | Results and Discussion                       | 38  |

|   | 5.6 | Conclusions                                  | 45  |

|   |     |                                              |     |

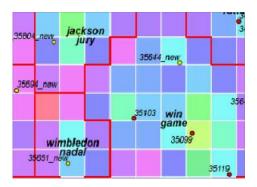

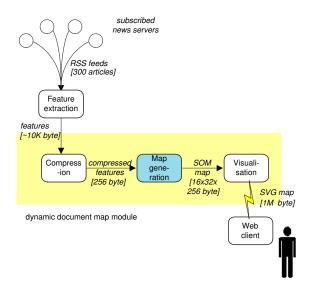

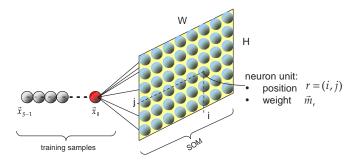

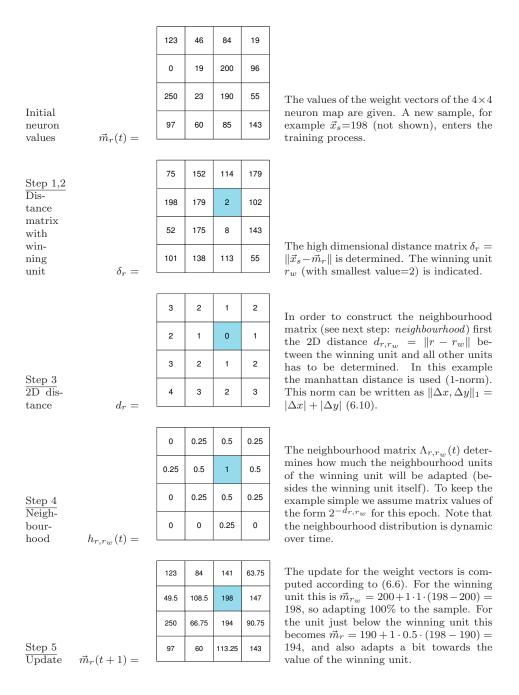

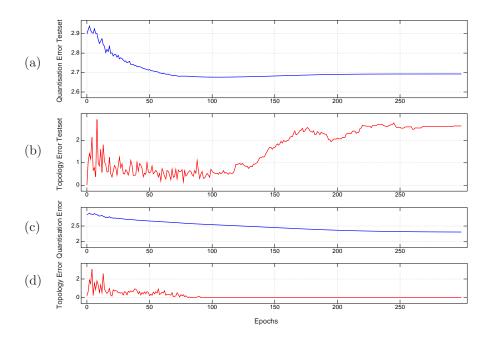

| 6 |     | 8 ,                                          | 47  |

|   | 6.1 |                                              | 47  |

|   | 6.2 |                                              | 48  |

|   |     | 1                                            | 48  |

|   |     |                                              | .50 |

|   |     | 9                                            | .55 |

|   |     | v                                            | .58 |

|   | 6.3 | 1 01 0                                       | 60  |

|   |     |                                              | 60  |

|   |     |                                              | 63  |

|   | 0.4 | 8 1                                          | 64  |

|   | 6.4 | <u>.</u>                                     | 66  |

|   |     | v                                            | 66  |

|   |     | 1                                            | 70  |

|   |     | 9                                            | 78  |

|   |     | r                                            | 79  |

|   |     | 1                                            | .80 |

|   | 6.5 |                                              | .80 |

|   | 6.6 | Conclusions                                  | .87 |

| 7 | Eva | luation and Conclusions 1                    | 89  |

| • | 7.1 |                                              | .89 |

|   | 7.2 |                                              | .89 |

|   | 7.3 |                                              | .90 |

|   | 7.4 |                                              | 01  |

| OD 1 | 1   | c  | $\sim$ |        |

|------|-----|----|--------|--------|

| Tab  | ıle | ot | Cor    | ntents |

| A                         | A.1  | evant Linedancer Details Relevant Linedancer instructions |     |

|---------------------------|------|-----------------------------------------------------------|-----|

| $\mathbf{A}_{\mathbf{j}}$ | ppen | dices                                                     | 193 |

# List of Acronyms

AGU Address-Generation Unit

**ALU** Arithmetic and Logical Unit

AMD Advanced Micro Devices

ANN Artificial Neural Network

ANN Artificial Neural Network

ANSI American National Standards Institute

APL A Programming language

ASIC Application Specific Integrated Circuit

ASP Associative String Processor

BBC British Broadcasting Corporation

BMU Best Matching Unit

CAM Content Addressable Memory

CCU Communication and Configuration Unit

CM Configuration Manager

${\color{red}\textbf{CMOS}} \qquad \text{Complementary MetalOxideSemiconductor}$

CMYK Cyan, Magenta, Yellow, and blacK

CNAPS Co-processing Node Architecture for Parallel Systems

CNN Cable News Network

COCOMO COnstruction COst MOdel

CSDF Cyclo-Static DataFlow

CSDF Cyclo-Static DataFlow

DCT Discrete Cosine Transform

DMA Direct Memory Access

dpi dots per inch

**DRAM** Dynamic Random Access Memory

DSL Domain Specific LanguageDSM Domain Specific Modelling

**DSP** Digital Signal Processor

**DSRC** Domain Specific Reconfigurable Core

EBM Energy-Based Model

EXT EXTended memory

FFT Fast Fourier Transform

FIR Finite Impulse Response

FPGA Field Programmable Gate Array

GALS Globally Asynchronous Locally Synchronous

$\begin{array}{ll} \textbf{GB} & \text{Giga Byte} \\ \textbf{GHz} & \text{Giga Hertz} \end{array}$

GOPS Giga Operations Per Second

GPP General Purpose Processor

HDL Hardware Description Language

**HP** Hewlett-Packard

HTML HyperText Markup LanguageHUT Helsinki University of Technology

HVS Human Visual System

IBM International Business Machines

IDF Inverse Document Frequency

IIR Infinite Impulse Response

ILP Instruction Level Parallelism

IO Input / Output

IT Information Technology

KB Kilo Byte

KLOC thousand Lines Of CodeKPN Kahn Process Network

LFSR Linear Feedback Shift Register

LOC Lines Of Code

lsb least significant bit(s)

LUT Look Up Table

MB Mega Byte

MBD Model-Based Design

MC-SoC Many-Core System-on-Chip

MDA Model-Driven Architecture

MDA Model-Driven ArchitectureMDD Model-Driven Development

MHz Mega Hertz

MIMD Multiple Instruction Multiple Data

MIPS Million Instructions Per Second

ML Meta-Language

MMD Modified Metropolis Dynamics

MMU Memory Management Unit

MP3 MPEG-1 Audio Layer 3

MPEG Moving Pictures Experts Group

MRF Markov Random Field

msb most significant bit(s)

MT Memory Tile

NLP Natural Language ProcessingNML Native Mapping Language

NoC Network on Chip

PAC Processing Array Cluster PAE Processing Array Element **PDA** Personal Digital Assistent PDS Primary Data Store **PDT** Primary Data Transfer PΕ Processing Element PPA Processing Part Array ppm pages per minute

QE Quantisation Error QoS Quality of Service

RAM Random Access Memory

RGB Red Green Blue

RISC Reduced Instruction Set Computer

RIP Raster Image Processing

RSS Really Simple Syndication

RTS Run Time Support

SCM Supervising Configuration Manager

SDS Secondary Data StoreSDT Secondary Data Transfer

SIMD Single Instruction Multiple Data

SISO Single Input Single Output

SF Software Factory

**SMP** Symmetric Multi-Processing

SoC System-on-ChipSOM Self Organising Map

**SPARC** Scalable Performance ARChitecture

SQL

Structured Query Language

SSE2

Streaming SIMD Extensions 2

SSM

Soft System Methodology

SRAM

Static Random Access Memory

SVG Scalable Vector Graphics

TDS Ternary Data Store

TDT Ternary Data Transfer

TE Topology Error

TF Term Frequency

**TLB** Translation Lookaside Buffer

TP Tile Processor

UML Unified Modeling LanguageURL Uniform Resource Locator

VHDL Very-high-speed integrated circuits Hardware Description Language

**VLIW** Very Long Instruction Word

WiMAX Worldwide interoperability for Microwave Access

XOR Exclusive OR

**XP** Extreme Programming

**XPP** eXtreme Processing Platform

**XSLT** eXtensible Stylesheet Language Transformations

## 1.1 Introduction

This thesis is concerned with the development of embedded systems in information-rich contexts such as document processing for offices. Two intertwined trends play a role in the development of such systems. One is the unabatingly growing complexity of applications and the other the advance of powerful and often massively parallel embedded computer architectures. Combined, the trends cause a significant increase in the complexity of embedded systems and pose new challenges for the development of embedded software (firmware).

The goal of this chapter is to anchor firmware development for many-core<sup>1</sup> processors in tomorrow's document processing products and services. We do that by departing from a personal vision on document processing<sup>2</sup>, that envisions tomorrow's computing demands. The trends on four computation-related aspects of this vision are mentioned and related to each other: content, hardware, software, and products & services. The latter links business to the first three aspects (Section 1.2.1). The mutual confrontation of these aspects motivates the importance of improved firmware development for embedded systems and cumulates in a problem description (Section 1.3). Finally, the structure of the thesis is given in Section 1.4.

$<sup>^{1}</sup>$  A core is an independent processing entity containing at least a control unit and one or more execution units.

<sup>&</sup>lt;sup>2</sup> This personal vision is not the official vision of Océ.

# 1.2 Document processing in a changing world

The purpose of this section is to create a possible future scenario of document processing in the office in which trends in four aspects, *content*, *hardware*, *software*, and *products & services*, are related to each other.

#### 1.2.1 **Vision**

Document processing follows the changing information flows in the world. One of the dominant media still is paper, but it is used differently nowadays. We like to use paper for a short time and then dispose it rather than use it for archiving purposes [105]. An alternative is a digital medium. Digital information can be processed, not only by humans, but also by intelligent software. The Semantic Web<sup>3</sup> for example, is an evolving extension of the World Wide Web in which the semantics of information and services on the web is defined, and which implements inference engine(s) and ontologies that cover the basic domains of human knowledge.

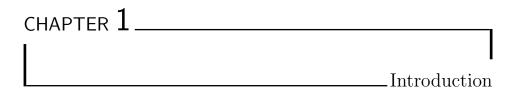

We have chosen for the *semantic copier* to play a central role in our vision. The semantic copier is a fictive extension of the basic copier (yellow parts), in Figure 1.1. The copier model is chosen because it is the most simple transformer that involves  $input \rightarrow processing \rightarrow output$  in a feedback loop that is being closed by a user. The goal of the semantic copier is to reduce the information burden of an office professional by processes with autonomous and proactive behaviour, based on knowledge of the context of the user (awareness). We will subsequently describe the semantic copier concept and the technologies that will be used to build it. At the left-hand side in Figure 1.1 the copier obtains its input, and after processing the output is generated (at the right-hand side). The vertical axis represents the projected developments over time. Possible emerging behaviour of such a copier includes summarisation (the act of preparing a summary), translation (e.g., Chinese  $\rightarrow$  English), and even behaviours that support the decision making processes of professionals, as demonstrated in Apple's Knowledge Navigator<sup>4</sup>. Obviously these behaviours need – besides a thorough analysis and directed synthesis of the output – general world knowledge such as generally known objects as persons, buildings, and cities. At the left-hand side sensors feed the analysis, and symmetrically, at the right-hand side composed texts are output, for example, printed or articulated (speech) or in other ways. Note that the various parts of the semantic copier may be distributed to different locations and used at different points in time.

As an example we take the translation of an audio text and we will follow the stream of information from the origin (left) to the destination (right). The text

<sup>&</sup>lt;sup>3</sup> Tim Berners-Lee et al: "The Semantic Web.", Scientific American, May 2001, http://www.sciam.com/print\_version.cfm?articleID=00048144-10D2-1C70-84A9809EC588EF21.

<sup>&</sup>lt;sup>4</sup> Apple Computer Inc.: "The Knowledge Navigator.", 1987, video.google.com/videoplay? docid=-5144094928842683632.

Figure 1.1: The *semantic copier* is a fictive but inspiring extension of the basic copier (yellow shaded parts). The ultimate goal is to realise the equivalent of a knowledgeable conversational agent as featured by Apple's Knowledge Navigator.

stream is entered via an audio channel, for instance in a MPEG-1 Audio Layer 3 (MP3) format, and is subsequently syntactically and semantically analysed. The translation involves world knowledge, that is for example needed for translation rules, dictionary lookups, and to resolve implicit references to generally known objects as persons, buildings, cities etc. Before the output is published (e.g., printed), it is composed according to the grammar of the destination language.

In our eyes a mixture of old and new technologies will be used to realise the required intelligence of this complex system. The older technologies such as image processing, natural language technology, and inference engines, process their input and are not directly influenced by the effect their output has on the outside world. However, new technologies better exploit the environment the system is in. Since the embedded system is situated in a physical environment, it is possible to set up a feedback loop in which the immediate user, the near environment, and even the world (internet) participate, see Figure 1.1. The system's output induces actions of a user or reactions in the (near) environment, and when those are fed back to the input side the system learns to adapt old behaviour or even learns to develop new behaviour.

In our opinion, developments in for example embodied intelligence [96] and coevolution [71] show the way to this *emergent behaviour*. Emergent behaviour refers to the way complex systems and patterns arise out of a multiplicity of relatively simple interactions. It is behaviour that is not specified as such but emerges from a carefully set up optimisation process. The objective of these new approaches is to write less and simpler code for setting up this optimisation process and train the behaviour rather than to program its functionality in an explicit manner. As a result the system obtains a smarter behaviour at lower development effort.

To allow for a good awareness of the environment, the semantic copier changes its physical appearance with respect to the basic copier. The point of service is not restricted to the location of the hardware anymore. The input and output are detached from the copier (today mostly positioned at a corridor or mail room) and are moved closer to the working desk. The same applies for the processing, that is integrated in the commodity IT infrastructure, leaving the bare scan and print unit in its familiar environment. Also at the processor level a behaviour-oriented approach is visible. For example Intel describes its "Recognition, Mining and Synthesis scenario" a processing platform for the 2015 workload model. The platform supports a kind of sense-think-act behaviour: recognition (what is?), mining (is this?), and synthesis (what if?).

To conclude, in our vision the semantic copier is a system that realises intelligent behaviour in two complementary ways. First, it transforms its input data to the demanded value added output. Second, it is aware of the immediate context of the user – partly influenced by its own output – and can act autonomously on it, thereby realising desired behaviours e.g., adaptivity.

#### 1.2.2 Trends

In the above vision four aspects, that play a role in building the semantic copier, can be identified. These four aspects are: content, hardware, software, and products & services. The purpose of this section is to describe the autonomous trends of these four aspects, and to prepare for their relations in embedded systems design (Section 1.2.3).

Content. According to Gulli [57] the indexable web (2005) is larger than 11 billion pages. Market research institute IDC estimates the 'digital universe' to be 161 billion gigabytes in 2006 and projects a six-fold increase by 2010<sup>6</sup>. The usage<sup>7</sup> of the web is still growing. An integral growth of 305% over the past 8 years is reported<sup>8</sup>, and some 'less developed' continents (Africa, Middle East, Latin America) note already an average rate of more than 100% growth per year. To summarise, the amount of processable information is extremely large and is growing each day.

<sup>&</sup>lt;sup>5</sup> Pradeep Dubey: "A Platform 2015 Workload Model: Recognition, Mining and Synthesis Moves Computers to the Era of Tera.", 2005, http://download.intel.com/technology/computing/archinnov/platform2015/download/RMS.pdf.

<sup>&</sup>lt;sup>6</sup> Frederick Lane: "IDC: World Created 161 Billion Gigs of Data in 2006.", 2007, http://www.toptechnews.com/story.xhtml?story\_id=01300000E3D0.

<sup>7</sup> Internet World Stats defines usage by a person who has available access to an internet connection point and has the basic knowledge required to use web technology.

<sup>8</sup> Miniwatts marketing group: "Internet world stats: Usage and population statistics.", 2008, http://www.internetworldstats.com/stats.htm.

Information, that is acted upon, has shorter lifetimes. News is for example a typical information category that can influence decision makers directly. Most news items have a very short lifetime, but a few continue to be accessed well beyond their initial release. The average halftime of a news document is 36 hours<sup>9</sup>. For streaming information this can be reduced even further, down to the time of a single video frame (msec range).

A pressing problem is information overload. Information overload refers to the state of having too much information to make a decision on or remain informed about a topic. See also Chapter 6.

**Hardware.** For processor developments, Moore's law – originally formulated in 1965 [90] – still holds<sup>10</sup>. However, because of power dissipation, the single-core processor is replaced by a multi-core processor. To even further optimise the *computational efficiency* (performance-power dissipation ratio expressed in [MIPS/Watt]) heterogeneous System-on-Chips (SoCs), or many-cores, have been developed [63][39].

Besides a scalable processor and memory architecture, many-core SoCs also have a scalable communication bandwidth architecture [63]. For example the chip implementation of the IBM Cell employs multiple ring networks to interconnect the nine processors on the chip [74].

The size of transistors is decreasing, so does the cost per transistor. However, the manufacturing expenses per unit area has increased over time, since materials and energy expenditures per unit area have only increased with each successive integration technology. Large enough series keep the cost stable over time; in practice this means that the consumer gets 'more for the same price'.

**Software.** The major trend is that the complexity of software increases each year [64], and thus increases the existing *software crisis*. The software crisis was a term used in the early days of software engineering, before it was a well-established subject. The term was used to describe the impact of rapid increases in computer power and the complexity of the problems that could be tackled. In essence, it refers to the difficulty of writing correct, understandable, and verifiable computer programs.

Complexity emerges in many ways. We mention here the excessive development effort and the inherently weak performance of sequential processing. In particular for embedded systems the excessive development time has even more impact because of the many extra concerns that have to be dealt with. For ex-

<sup>&</sup>lt;sup>9</sup> Z. Dezso et al: "Fifteen Minutes of Fame: The Dynamics of Information Access on the Web.", 2005, http://www.citebase.org/abstract?id=oai:arXiv.org:physics/0505087.

Michael Kanellos: "Moore's law to roll on for another decade", 2003, http://news.cnet.com/ 2100-1001-984051.html.

ample in the automotive industry<sup>11</sup> the increasingly complex embedded systems have led to disappointment as cars are delivered to the market with software and electronic defects. Warranty costs are on the rise as brand perception suffers.

Traditional optimisation techniques are based on order of complexity reduction, that work for sequential processing but not for parallel processing. These techniques tend to introduce dependencies and new data structures that complicate parallelisation; programs are getting so immensely large that it is not feasible to unravel these dependencies.

Driven by the increasing performance demands, the transition of a single-core processor to parallel many-core SoCs, adds new problems. Compiler technology is not ready to translate sequential programs in multiple threads running on multiple cores [39]. Radical ideas are required to make many-core architectures a secure and robust base for productive software development since the existing solutions only shows successes in narrow application domains. This is the very reason why recently two groups of companies (AMD, HP, IBM etc. and Intel & Microsoft) sponsor parallel programming research at universities (Stanford and Berkley respectively)<sup>1213</sup>.

**Products & Services.** Products and services obey the general trends that need no further introduction. We only mention the demand for:

- increasing functionality (smarter, faster, better usable, etc.),

- shorter time to market, and

- cheaper services (or even free<sup>14</sup>).

# 1.2.3 Relating trends

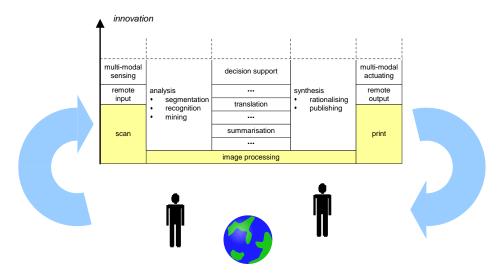

The purpose of this section is to show that for an embedded system the various trends lead to a significant shift in the division between hardware and software. We will connect related autonomous trends from the different aspects and tag the connection with a matching or a non-matching (mismatch) relation, see Figure 1.2. The figure includes all four mentioned aspects with their trends enclosed in a rounded box. The tagged relations are shown, visualised by coloured ellipses:

<sup>&</sup>lt;sup>11</sup> Stefan Gumbrich: "Embedded systems overhaul: It's time to tune up for the future of automotive.", IBM Business Consulting Services, 2004, http://tld.www-03.cacheibm.com/solutions/plm/doc/content/bin/g510\_3987\_embedded\_systems\_overhaul.pdf.

Advanced Micro Devices, Hewlett-Packard, IBM, Intel, NVidia and Sun Microsystems are funding Stanford's new Pervasive Parallelism Lab, and Intel and Microsoft officially announced their plan to research on parallel programming together with the University of California at Berkeley and University of Illinois at Urbana-Champaign.

<sup>&</sup>lt;sup>13</sup> Rick Merritt: "Stanford kicks off parallel programming effort.", 2008, http://www.eetimes.com/news/latest/showArticle.jhtml?articleID=207403653.

<sup>14</sup> Chris Anderson: "Free! Why \$0.00 is the future of business.", 2008, http://www.wired.com/techbiz/it/magazine/16-03/ff\_free.

Figure 1.2: Relating trends in the four aspects: content, software, hardware and products & services, gives cause for a new partition in hardware/software codesign

green for a match, red for a mismatch. For example the increasing size of content matches with the parallel storage capacity of hardware.

**Hardware.** On the hardware side the following matches can be made, see Figure 1.2:

- the data volumes of content can be covered by distributing data over multiple processors,

- the update rate of information (reduced lifetime) can be handled by the massively parallel processing capacity and the high aggregated communication bandwidth of SoCs, and

- the demanded pricing reductions asked for by the market, are in line with the current developments in chip costs: more computational power for the same price.

**Software.** Software development still is immature in comparison to hardware development, where first-time-right<sup>15</sup> is the normal procedure. Software developments on average tend to be late, consume lots of engineering resources and have

<sup>15</sup> In digital hardware development the implementations are usually right the first time.

questionable quality, so it is a complex undertaking. This causes the following mismatches on the software side:

- the increasing amount of data (as indicated for example in Footnote (6) on page 4) cannot be handled adequately by current software practices while running on a General Purpose Processors (GPPs) [39],

- the software processing time (on GPPs) does not correspond to the update frequency of information, whether it concerns extensive on-line video processing (MB/sec), or off-line data mining (GB/h), and

- the increasing market pressure to deliver products faster than the previous version, demands reduced development times. This is in contrast to general software development practice.

Moreover, the following observations can be made:

- Compiler technology is not capable of generating parallel code from sequential legacy [39]. We need the option to code the parallelism manually.

- When moving towards very large number of processors, the current way of working requires more programmers than available [99].

- Most algorithms that require random access to data or take time greater than  $O(N \cdot log N)$ , for data size N, are not scalable to large data sets [99].

All relations at the hardware side do match and actually represent opportunities for solving problems. At the software side mismatches emerge, and those represent challenges for improving the development of embedded systems.

# Summarising

The advances of heterogeneous multi-core chips in embedded systems design will also change the way software is written. This is independent of application domain, from a small multi-media Personal Digital Assistent (PDA) to blade-based racks in Amazon's compute server facilities; all have to run power-aware [39]. The above interrelation of hardware and software trends lead to the following conclusions:

- Traditional software development cannot cope with the identified trends: more data to process, shorter lifetime of information, and increasing market pressure to reduce time to market.

- Hardware, in particular the massively parallel many-core systems, enable new programming paradigms.

- The challenge is to find simple parallel processing schemes that reduce software complexity significantly.

# 1.3 Problem description

## 1.3.1 Problem description and thesis

Following the above mentioned line of reasoning it is beneficial to reconsider the traditional balance between hardware and software in embedded system design. Therefore, our approach is to break with the sequential coding tradition and apply parallelism to allow for new simple models. This requires support for modelling the problem in a parallel way such that it is suitable for a many-core hardware architecture, and human guidance for bridging the gap between the two in an orderly manner.

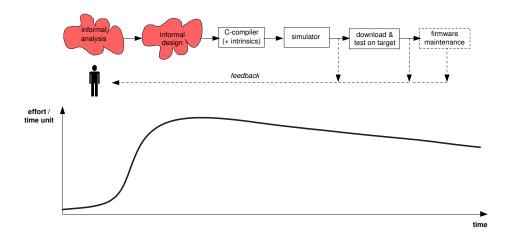

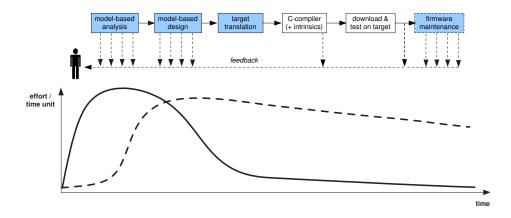

Today the *de facto* way applications are programmed on such dedicated systems is by manually adapting sequential code, which is mostly written in C. This adaptation involves the replacement of the time consuming sequential parts by parallel code. Most tooling is supplied by the manufacturer of the processor hardware and is, to no suprise and without exception, a C-compiler with *intrinsic instructions* (hardware dependent predefined functions), and occasionally, a simulator. This means that the design can only be validated at the end of the development cycle, when the code finally becomes available.

This leads to the following research thesis:

While most research on firmware<sup>16</sup> development concentrates on automatic conversion of C-like descriptions to program applications for massively parallel processors, it is more productive to explicitly remodel the application in a parallel way by using a methodology based on a semi-automatic guidance through the whole firmware development process.

### 1.3.2 Contribution

The research thesis leads to the following claims:

For an effective and efficient implementation on a massively parallel processing core it is necessary to manually (re)model the problem in a suitable parallel representation;

Chapter 3, Section 4, and Chapters 4, 5, 6, Sections 2, 3, 4.

- 2. A semi-automatic and interactive development process is needed for mapping a task on a dedicated massively parallel processing core efficiently; Chapter 3, (Sub)sections 2, 5.1.

- A single architectural language firmly based on mathematics for all development phases reduces development time and reduces the number of design errors;

Chapter 3, Subsection 5.2.1, and Chapters 4,5,6, Subsection 4.2.

Firmware is a computer program that is embedded in a hardware device, for example a microcontroller. The term "firmware" was originally used for micro-programs written for microsequencers such as AMD29xx.

- 4. Most of the relevant extra-functional requirements can be handled by integrating them into the regular functional flow; as a consequence the architectural language should support *in situ* monitoring and visualisation of quantifiable extra-functional properties;

- Chapter 3, Section 4, and Chapters 4,5,6, Subsection 4.2.

- 5. In the development process small steps and immediate feedback are crucial; Chapter 3, Section 4.

- 6. The development process should have a phased approach serving the various development roles, and should subsequently include:

- (a) a familiarisation phase with respect to the problem and the target hardware architecture(s),

- (b) an incremental prototyping phase (hardware architecture independent),

- (c) a transformational development phase (hardware architecture dependent),

which are performed in a cyclic manner when needed (e.g., in case of design iterations);

Chapter 3, Sections 6, 7, 8, and Chapters 4, 5, 6, Sections 2, 3, 4.

# 1.4 Thesis outline

The design methodology proposed in this thesis is shaped by evaluating three different case-studies, each with its own characteristics. The cases provide for a wide coverage of existing as well as new problem contexts and models. All three cases map on the same hardware architecture: a massively parallel processing array (Linedancer).

In the first case, a high volume image processing pipeline for a colour printer, is combined with a known model (FPGA implementation), see Chapter 5. Next, for image quantisation, a new model is developed that fits well on a parallel array, see Chapter 4. Finally, in the last case a new problem (mining and visualisation of a document space) is selected to extend and test the robustness of the methodology, see Chapter 6. The design methodology, called IRIS, is presented in Chapter 3, and includes an overview on state of the art methodologies. Because of the close interaction of hardware and software we have included a short overview of the state of the art on many-core systems, see Chapter 2, that also includes some details of the used Linedancer processor. In Chapter 7 we formulate the conclusions.

# CHAPTER 2

\_State of the Art Massively Parallel Embedded Architectures

In this chapter we focus on many-core architectures for streaming applications. The many-core concept has a number of advantages: (1) depending on the requirements, cores can be (dynamically) switched on/off, (2) the many-core structure fits well to future process technologies, more cores will be available in advanced process technologies, but the complexity per core does not increase, (3) the many-core concept is fault tolerant, faulty cores can be discarded and (4) multiple cores can be configured in parallel. When processing and memory are combined in the cores, tasks can be executed efficiently on cores (locality of reference). There are a number of application domains that can be considered as streaming applications, for example colour image processing, data mining, multimedia processing, medical image processing, sensor processing (e.g., remote surveillance cameras), phased array radar systems and wireless baseband processing. In this chapter the key characteristics of streaming applications are highlighted, and the characteristics of the processing architectures to efficiently support these types of applications are addressed. We present an overview of some stateof-the-art embedded core architectures for streaming applications and select one as a target hardware architecture to be used in this thesis.

Major parts of this chapter have been accepted as a bookchapter for the CRC Book series [P9].

## 2.1 Introduction

This chapter addresses heterogenous and homogeneous many-core SoC platforms for streaming applications. In streaming applications, computations can be specified as a data flow graph with streams of data items (the edges) flowing between computation kernels (the nodes). Most signal processing applications can be naturally expressed in this modelling style [32]. Typical examples of streaming applications are: colour image processing (Chapter 5, Chapter 4), data mining (Chapter 6), multimedia processing (e.g., MPEG, MP3 coding/decoding), medical image processing, sensor processing (e.g., remote surveillance cameras), phased array radar systems and wireless baseband processing. In a heterogeneous many-core architecture, a core can either be: a bit-level reconfigurable unit (e.g., FPGA), a word-level reconfigurable unit, or a general-purpose programmable unit (DSP or microprocessor). We assume the cores of the SoC are interconnected by a reconfigurable Network on Chip (NoC). The programmability of the individual cores enables the system to be targeted at multiple application domains.

We take a holistic approach, which means that all aspects of systems design need to be addressed simultaneously in a systematic way [108]. We believe that this is key for an efficient overall solution, because an interesting optimization in a small corner of the design might lead to inefficiencies in the overall design. For example the design of the NoC should be coordinated with the design of the processing cores, and the design of the processing cores should be coordinated with the tile specific compilers. Eventually, there should be a tight fit between the application requirements and the SoC and NoC capabilities.

We first introduce streaming applications and many-core architectures in sections 2.1.1 and 2.1.2. After that we give a multi-dimensional classification of architectures for streaming applications in Section 2.2. For each category one or more sample architectures are presented (Section 2.3). We end this chapter with a conclusion and make a selection for the target hardware architecture to be used in this thesis, see Section 2.4.

# 2.1.1 Streaming Applications

The focus of this chapter is on many-core SoC architectures for streaming applications where we can assume that the data streams are semi-static and have a periodic behaviour. This means that for a long period of time subsequent data items of a stream follow the same route through the SoC. The common characteristics of typical streaming applications are:

- They are characterised by relatively simple local processing but a huge amount of data.

- Data arrives at nodes at a rather fixed rate, which causes periodic data transfers between successive processing blocks. The resulting communication bandwidth is application dependent and a large variety of communi-

cation bandwidth is required. The size of the data items and data rate is application dependent.

- The data flows through the successive processes in a pipelined fashion. Processes might work in parallel on parallel processors or can be time-multiplexed on one or more processors. Therefore, streaming applications show a predictable temporal and spatial behaviour.

- For our application domains, typically throughput guarantees (in data items per sec.) are required for the communication as well as for the processing. Sometimes also latency requirements are given.

- The life-time of a communication stream is semi-static, which means a stream is fixed for a relatively long time.

## 2.1.2 Many-core Architectures

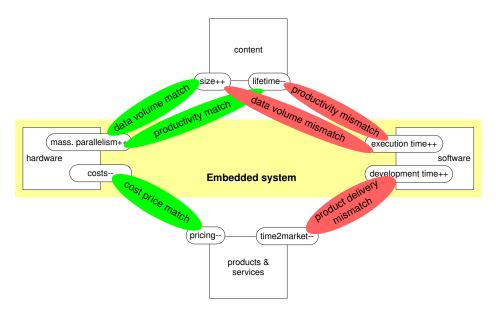

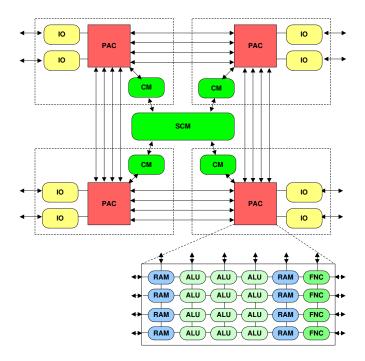

Flexible and efficient SoCs can be realised by integrating hardware blocks (called tiles or cores) of different granularities into heterogeneous SoCs. In this chapter the term *core* is used for processor-like hardware blocks and the term *tile* is used for Application Specific Integrated Circuits (ASICs), fine-grained reconfigurable blocks and memory blocks. We assume that the interconnected building blocks can be heterogeneous (see Figure 2.1), for instance bit-level reconfigurable tiles (e.g., embedded FPGAs), word-level reconfigurable cores (e.g., Domain Specific Reconfigurable Cores), general-purpose programmable cores (e.g., DSPs and microprocessor cores) and memory blocks. From a systems point of view these architectures are heterogeneous multi-processor systems on a single chip. The programmability and reconfigurability of the architecture enables the system to be targeted at multiple application domains. Recently a number of many-core architectures have been proposed for the streaming application domain. Some examples will be discussed in Section 2.3.

A many-core approach has a number of advantages:

- It is a future-proof architecture, as the processing cores do not grow in complexity with technology. Instead, as technology scales, simply the number of cores on the chip grows.

- A many-core organization can contribute to the energy-efficiency of a SoC. The best energy savings can be obtained by simply switching off cores that are not used, which also helps in reducing the static power consumption. Furthermore, the processing of local data in small autonomous cores abides the locality of reference principle. Moreover, a core processor might be adaptive, it does not always have to run at full clock speed to achieve the required Quality of Service (QoS).

| core | description                     |

|------|---------------------------------|

| FPGA | Field Programmable Gate Array   |

| GPP  | General Purpose Processor       |

| DSP  | Digital Signal Processor        |

| ASIC | Application Specific Integrated |

|      | Circuit                         |

| DSRC | Domain Specific Reconfigurable  |

|      | Core                            |

| MT   | Memory Tile                     |

Figure 2.1: A heterogenous SoC template

- When one of the cores is discovered to be defect (either because of a manufacturing fault or discovered at operating-time by the built-in-diagnosis) this defective core can be switched-off and isolated from the rest of the design.

- A many-core approach also eases verification of an integrated circuit design, since the design of identical cores only has to be verified once. The design of a single core is relatively simple and therefore a lot of effort can be put in (area/power) optimizations on the physical level of integrated circuit design.

- The computational power of a many-core architecture scales linearly with the number of cores. The more cores there are on a chip, the more computations can be done in parallel (provided that the network capacity scales with the number of cores and there is sufficient parallelism in the application).

- Although cores operate together in a complex system, an individual tile

operates quite autonomously. In a reconfigurable many-core architecture

every processing core is configured independently. In fact, a core is a natural

unit of partial reconfiguration. Unused cores can be configured for a new

task, while at the same time other cores continue performing their tasks.

That is to say, a many-core architecture can be reconfigured partly and

dynamically.

### Heterogeneous Many-Core SoC (MC-SoC)

The reason for heterogeneity in a SoC is that typically, some algorithms run more efficiently on bit-level reconfigurable architectures (e.g., pseudo random number generation), some on DSP-like architectures and some perform optimal on word-level reconfigurable platforms (e.g., FIR filters or FFT algorithms). We distinguish four processor types: General Purpose Processor, fine-grained reconfigurable hardware (e.g., FPGA), coarse-grained reconfigurable hardware and ded-

icated hardware (e.g., ASIC). The different tile processors in the SoC are interconnected by a Network-on-Chip (NoC). Both SoC and NoC are dynamically reconfigurable, which means that the programs running on the processing tiles as well as the communication channels are configured at run-time. The idea of heterogeneous processing elements is that one can match the granularity of the algorithms with the granularity of the hardware. Application designers or high-level compilers can choose the most efficient processing core for the type of processing needed for a given application task. Such an approach combines performance<sup>1</sup>, flexibility and energy-efficiency. It supports high performance through massive parallelism, it matches the computational model of the algorithm with the granularity and capabilities of the processing entity, it can operate at minimum supply voltage and clock frequency and hence provides energy-efficiency and flexibility at the right granularity only when and where needed and desirable. A thorough understanding of the algorithm domain is crucial for the design of an (energy-) efficient reconfigurable architecture. The architecture should impose little overhead to execute the algorithms in its domain. Streaming applications form a good match with many-core architectures: the computation kernels can be mapped on cores and the streams to the NoC links. Inter-processor communication is in essence also overhead, as it does not contribute to the computation of an algorithm. Therefore, there needs to be a sound balance between computation and inter-processor communication. These are again motivations for a holistic approach.

### Programmability

Design automation tools form the bridge between processing hardware and application software. Design tools are a crucial requirement for the viability of many-core platform chips. Such tools reduce the design cycle (i.e., cost and time-to-market) of new applications. The application programmer should be provided with a set of tools that on one side hides the architecture details but on the other side gives an efficient mapping of the applications onto the target architecture. However, high-level language compilers for domain specific streaming architectures are far more complex than compilers for general purpose superscalar architectures because of the data dependency analysis, instruction scheduling and allocation. Next to tooling for application development also tooling for functional verification and debugging is required for programming many-core architectures. In general, such tooling comprises:

general Hardware Description Language (HDL) simulation software that

provides full insight in the hardware state, but is relatively slow and not

suited for software engineers,

With performance we mean the number of operations per time unit, and this is reciprocal to execution time.

- dedicated simulation software that provides reasonable insight in the hardware state, performs better than general hardware simulation software and can be used by software engineers, and

- hardware prototyping boards that achieve great simulation speeds, but provide poor insight in hardware state and are not suited for software engineers.

By employing the tiled SoC approach, as proposed in Figure 2.1, various types of parallelism can be exploited. Depending on the core architecture, one or more levels of parallellism are supported.

- Thread-Level Parallelism is explicitly addressed by the many-core approach as different tiles can run different threads;

- Data-Level Parallelism is achieved by processing cores that employ parallelism in the data path;

- Instruction-Level Parallelism is addressed by processing cores when multiple data path instructions can be executed concurrently.

The programming of these kinds of streaming architectures is on one hand complex because of the variety in processors and parallelism but also complex because of the primitive state of the tooling. Furthermore, the *composability* issue<sup>2</sup> needs extra attention and restricts the design choices in hardware architecture as well as software [108]. The programmability of many-core architectures is an unsolved problem.

## 2.2 Classification

Different hardware architectures are available in the embedded systems domain to perform DSP functions and algorithms: *GPP*, *DSP*, (re-)configurable hardware and application specific hardware ASIC.

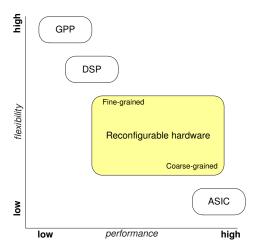

These hardware architectures have different characteristics in relation to *performance*, *flexibility* or *programmability* and *energy efficiency*. Figure 2.2 depicts the trade-off in flexibility and performance for different hardware architectures. Generally, more flexibility implies a less energy efficient solution.

Crucial for the fast and efficient realisation of a Many-Core System-on-Chip (MC-SoC) is the use of pre-designed modules, the so-called building blocks. In this section we will first classify these building blocks, second we classify the MC-SoCs that can be designed using these building blocks together with the interconnection structures between these blocks.

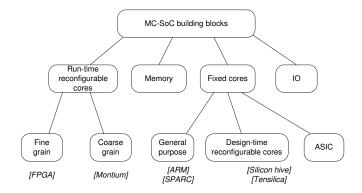

A basic classification of MC-SoC building blocks is given in Figure 2.3. The

<sup>&</sup>lt;sup>2</sup> Composability is a desired property that relates to the mapping of multiple independent applications on the same platform with the condition that each application does not influence any other application.

Figure 2.2: Flexibility versus performance trade-off for different hardware architectures

basic processing elements of an MC-SoC can be divided in run-time reconfigurable cores and fixed cores. The functionality of a run-time reconfigurable core is fixed for a relatively long period in relation to the clock frequency of the cores. Run-time reconfigurable cores can be subdivided into two classes: fine-grained reconfigurable cores and coarse-grained reconfigurable cores. Fine-grained reconfigurable cores are reconfigurable at bit-level (e.g., FPGA) while coarse-grained reconfigurable cores are reconfigurable at word-level (8 bit, 16 bit etc.). Two other essential building blocks are memory and I/O blocks. Reusing MC-SoCs building blocks to build larger systems increases the productivity of designers.

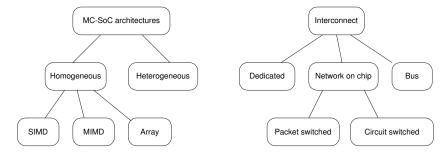

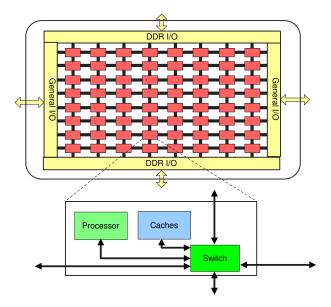

A classification of MC-SoCs is given in Figure 2.4. An MC-SoC basically consists of multiple building blocks connected by means of an interconnect. If an MC-SoC consists of multiple building blocks of a single type, the MC-SoC is referred to as *homogeneous*. The homogeneous MC-SoC architectures can be subdivided into Single Instruction Multiple Data (SIMD), Multiple Instruction Multiple Data (MIMD) and array architectures. Examples of these architectures will be given below. If multiple types of building blocks are used, the MC-SoC is called *heterogeneous*.

To interconnect the different building blocks, three basic classes can be identified: bus, Network-on-Chip and dedicated interconnects. A bus is shared between different processing cores and is a notorious cause of unpredictability. Unpredictability can be circumvented by a NoC [7]. Two types can be identified: packet-switched and circuit-switched. Besides the use of these more or less standardised communication structures, dedicated interconnects are still widely used. Some examples of different MC-SoC architectures are presented in Table 2.1.

Figure 2.3: Classification of MC-SoC building blocks for streaming applications

Figure 2.4: Classification of MC-SoC architectures and interconnect structures for streaming applications

In the following sections a few characteristic architectures will be presented in more detail.

# 2.3 Sample architectures

# 2.3.1 Montium Reconfigurable Processing Core

The Montium is an example of a coarse-grained reconfigurable processing core and targets the 16-bit DSP algorithm domain. The Montium architecture origins from research at the University of Twente [63][100]. The Montium processing core has been further developed by Recore Systems<sup>5</sup>. A single Montium process-

<sup>&</sup>lt;sup>3</sup> Nvidia, "Nvidia G80, architecture and GPU analysis", 2007, www.beyond3d.com/content/

<sup>&</sup>lt;sup>4</sup> Strictly speaking the Cell can be positioned as a heterogeneous processor, but because of the relative large number of SIMD cores it is categorised as homogeneous.

<sup>&</sup>lt;sup>5</sup> Recore Systems, www.recoresystems.com.

| Class         |       | Example                                                                            |  |

|---------------|-------|------------------------------------------------------------------------------------|--|

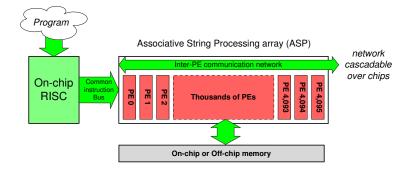

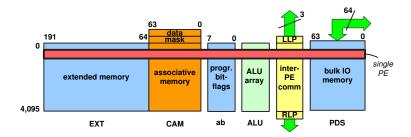

|               | SIMD  | Linedancer (see Section 2.3.4)<br>Geforce G80 <sup>3</sup><br>Xetal [42]           |  |

| Homogeneous   | MIMD  | Tilera (see Section 2.3.3)<br>Cell <sup>4</sup> [40]<br>Intel Tflop processor [44] |  |

|               | Array | PACT (see Section 2.3.2)<br>ADDRESS [85]                                           |  |

| Heterogeneous |       | Montium [63]<br>Silicon Hive [24]                                                  |  |

Table 2.1: Examples of different MC-SoC architecture

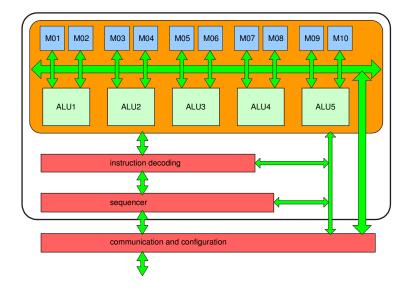

ing tile is depicted in Figure 2.5. At first glance the Montium architecture bears a resemblance to a VLIW processor. However, the control structure of the Montium is very different. The lower part of Figure 2.5 shows the Communication and Configuration Unit (CCU) and the upper part shows the coarse-grained reconfigurable Montium Tile Processor (TP).

Communication and Configuration Unit The CCU (Communication and Configuration Unit) implements the network interface controller between the NoC and the Montium TP. The definition of the network interface depends on the Network-on-Chip (NoC) technology that is used in a System-on-Chip (SoC) in which the Montium processing tile is integrated [23]. The CCU enables the Montium TP to run in *streaming* as well as in *block* mode. In *streaming* mode the CCU and the Montium TP run in parallel. Hence, communication and computation overlap in time in *streaming* mode. In *block* mode the CCU first reads a block of data, then starts the Montium TP, and finally after completion of the Montium TP, the CCU sends the results to the next processing unit in the SoC (e.g., another Montium processing tile or external memory).

Montium Tile Processor The Tile Processor (TP) is the computing part of the Montium processing tile. The Montium TP can be configured to implement particular DSP algorithms such as: all power of 2 FFTs upto 2048 points, non-power of 2 FFT upto FFT 1920, FIR filters, IIR filters, matrix vector multiplication, Discrete Cosine Transform (DCT) decoding, Viterbi decoders, Turbo (SISO) decoders. Figure 2.5 reveals that the hardware organisation of the Montium TP is very regular. The five identical Arithmetic Logic Units (ALU1 through ALU5) in a tile can exploit data level parallellism to enhance performance. This type of parallelism demands a very high memory bandwidth, which is obtained by hav-

Figure 2.5: The Montium TP coarse-grained reconfigurable processing tile

ing 10 local memories (M01 through M10) in parallel. The small local memories are also motivated by the locality of reference principle. The data path has a width of 16-bits and the ALUs support both signed integer and signed fixed-point arithmetic. The ALU input registers provide an even more local level of storage. Locality of reference is one of the guiding principles applied to obtain energy efficiency in the Montium TP. A vertical segment that contains one ALU together with its associated input register files, a part of the interconnect and two local memories is called a Processing Part (PP). The five PPs together are called the Processing Part Arrays (PPAs).

A relatively simple sequencer controls the entire PPA. The sequencer selects configurable PPA instructions that are stored in the instruction decoding block of Figure 2.5. For (energy) efficiency it is imperative to minimise the control overhead. The PPA instructions, which comprise ALU, Address-Generation Unit (AGU), memory, register file and interconnect instructions, are determined by a DSP application designer at design time. All Montium TP instructions are scheduled at design time and arranged into a Montium sequencer programme. By statically scheduling the instructions as much as possible at design time, the Montium sequencer does not require any sophisticated control logic which minimises the control overhead of the reconfigurable architecture.

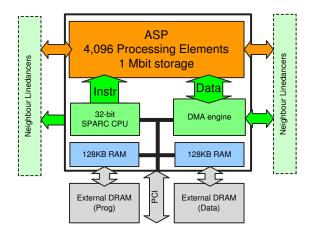

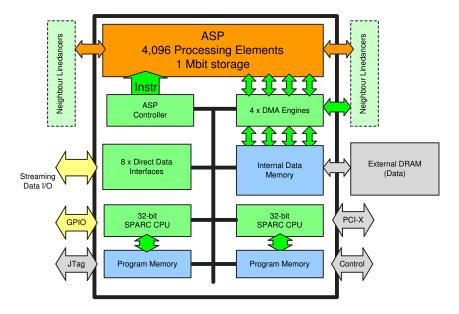

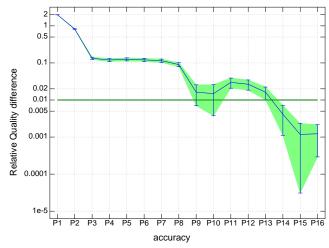

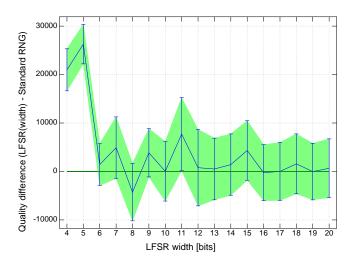

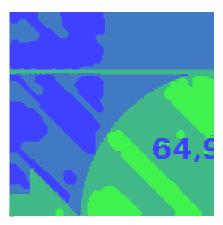

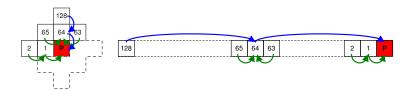

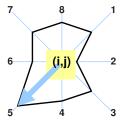

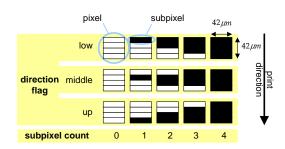

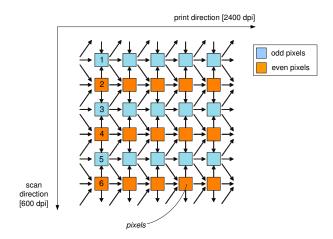

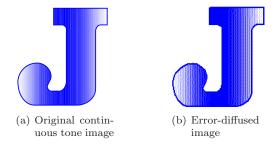

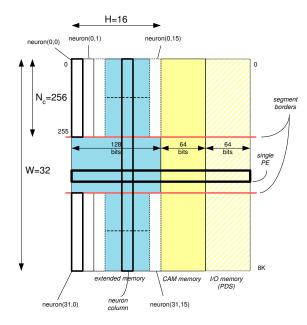

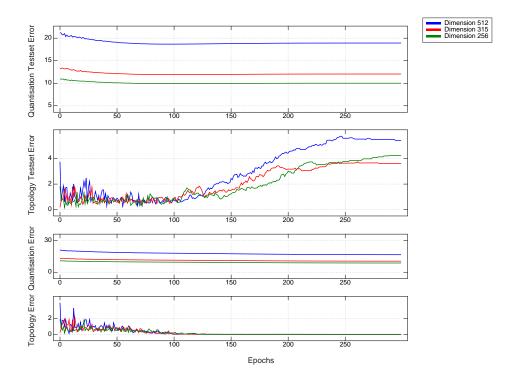

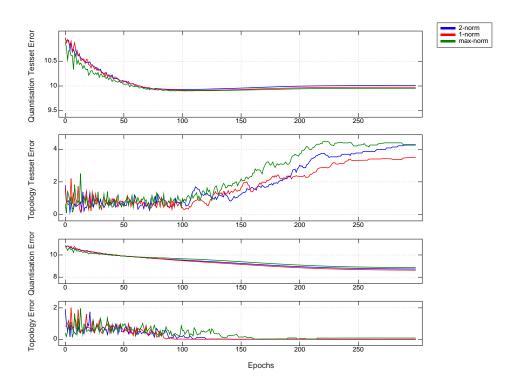

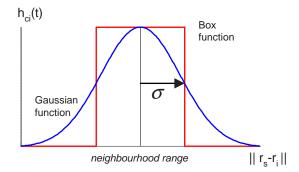

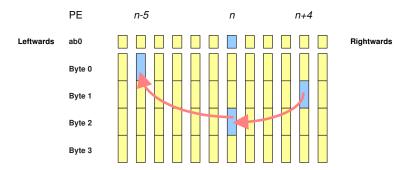

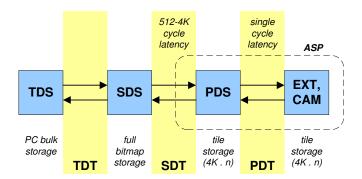

The Montium TP has no fixed instruction set, but the instructions are configured at configuration-time. During configuration of the Montium TP, the CCU writes the configuration data (i.e., instructions of the ALUs, memories and interconnects, etc.; sequencer and decoder instructions) in the configuration memory