# Towards Minimum Achievable Phase Noise of Relaxation Oscillators

Paul F. J. Geraedts, Ed (A. J. M.) van Tuijl, Eric A. M. Klumperink, Gerard J. M. Wienk, Bram Nauta <sup>1</sup>

## **Table of Contents entry:**

Oscillators show 1/f² phase noise, which is often benchmarked via a Figure of Merit (FoM). Practical ring oscillators can be close to the theoretical FoM limit of -165dBc/Hz at 290K. In contrast, relaxation oscillators have a better theoretical FoM limit (-169dBc/Hz), but until recently much worse practically achieved values. This paper presents a strategy to design a relaxation oscillator with similar FoM than ring oscillators have, while also featuring a linear frequency-tuning characteristic.

Abstract — A relaxation oscillator design is described, which has a phase noise rivaling ring oscillators, while also featuring linear frequency tuning. We show that the comparator in a relaxation-oscillator loop can be prevented from contributing to  $1/f^2$  colored phase noise and degrading control linearity. The resulting oscillator is implemented in a power efficient way with a switched-capacitor circuit. The design results from a thorough analysis of the fundamental phase noise contributions. Simple expressions modeling the theoretical phase noise performance limit are presented, as well as a design strategy to approach this limit. To verify theoretical predictions, a relaxation oscillator is implemented in a baseline 65nm CMOS process, occupying  $200\mu m \times 150\mu m$ . Its frequency tuning range is 1-12MHz and its phase noise is  $\mathcal{L}(100kHz)$ =-109dBc/Hz at  $f_{osc}$ =12MHz, while consuming  $90\mu W$ . A FoM of -161dBc/Hz is achieved, which is only 4dB from the theoretical limit.

*Index terms*: oscillator, low noise, phase noise, figure of merit, FoM, jitter, relaxation oscillator, thermodynamics, linear frequency tuning, large frequency tuning range, power efficiency

# I. INTRODUCTION

Oscillators are important circuits for on-chip frequency synthesis and digital clock generation. They can oscillate autonomously, but are also often locked to an external reference clock via a Phase Locked Loop. LC oscillators are commonly used for phase noise critical high frequency applications, that can live with a limited frequency tuning range (typically 5-20%). They take up an excessive area for lower frequencies, say below 1GHz, where it becomes difficult to realize high-Q coils with sufficiently large inductance. RC oscillators on the other hand can be quite compact, even at lower frequencies. In addition, they feature a large tuning range. Both ring oscillators and relaxation oscillators are forms of

1

<sup>&</sup>lt;sup>1</sup> Manuscript received February 2012. This work was supported in part by NXP Semiconductors, Eindhoven, The Netherlands. All authors are or have been at the University of Twente, IC Design group, Enschede, The Netherlands. Paul Geraedts and Ed van Tuijl are currently with Axiom IC, Enschede, The Netherlands. (corresponding author:+31 534892736; e-mail: e.a.m.klumperink@utwente.nl).

RC oscillators [1]. Relaxation oscillators have an important advantage over ring oscillators: they not only feature a large, but also a *linear* tuning range. A linear control characteristic is often convenient, while being crucial for FM modulation and demodulation with low distortion [2].

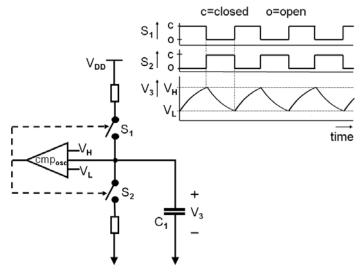

Fig. 1 shows a relaxation oscillator topology based on two resistors that alternately charge and discharge capacitor  $C_I$ . The capacitor voltage cycles between a high voltage  $V_H$  and a low voltage  $V_L$ controlled by a comparator with hysteresis. Such a resistor-based topology has a period time which linearly depends on resistance and capacitance. If resistors are replaced by current sources, a linearly current controlled frequency can be realized.

A study by Navid et al. has shown that the phase noise performance of RC oscillators is fundamentally bound by thermodynamics to a level that is rather poor compared to that of typical LC oscillators [1]. Meeting a phase noise specification with an RC oscillator can thus easily result in high power consumption. To minimize power dissipation, RC oscillator designs that perform near to their theoretical limit are wanted, and this paper pursues this aim for a relaxation oscillator.

Fig. 1: Basic relaxation oscillator topology based on resistive charging [1]

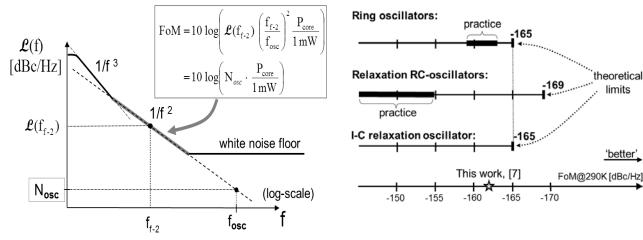

To characterize phase noise and jitter, the single-sided power spectral density  $\mathcal{L}(f)$  is useful (see Appendix A for its exact definition and relation to jitter). Fig. 2 shows  $\mathcal{L}(f)$  for a typical relaxation oscillator, with three indicated regions. Two "colored" regions, a 1/f<sup>3</sup> region and a 1/f<sup>2</sup> region, are caused by flicker and white noise that gets integrated in the oscillator [3]. Furthermore, white noise can be added directly without integratione.g. white noise in an output buffer contributes a "white noise floor".

Fig. 2: Phase noise plot with  $1/f^3$ ,  $1/f^2$  and white region and definitions of  $N_{osc}$  and FoM (see also Appendix A).

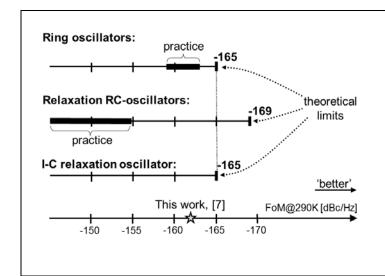

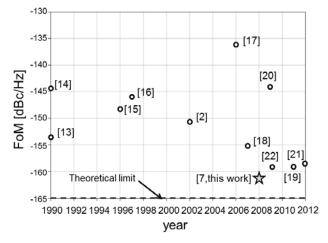

Fig. 3: Overview of theoretical and practical achievable FoMs of various oscillators

'better'

In a Phase Locked Loop, 1/f<sup>3</sup> noise can often be suppressed significantly by the loop gain [4] and the 1/f<sup>2</sup> noise of the oscillator is the most important timing jitter contribution together with the (usually white) noise of loop-components [4]. The value  $\mathcal{L}(f_{f-2})$  measured in the  $1/f^2$  region is thus of crucial importance. To benchmark oscillator phase noise, the "oscillator number" Nosc is useful [3] (see eqn. (21) in Appendix A). To quantify  $1/f^2$  phase noise, taking into account the power consumption of the oscillator core P<sub>core</sub>, the well-known FoM of eqn. (22) is often used [5][6] (see Fig. 2 and appendix A). In Fig. 3, FoM values for RC oscillators are indicated, based on [1]. Practical ring oscillators can be close to the theoretical FoM limit of -165dBc/Hz at 290K. In contrast, relaxation oscillators have a better theoretical FoM limit (-169dBc/Hz), but worse practically achieved values [1][7]. This can be explained partly by the phase noise contribution of the loop-comparator (cmp<sub>osc</sub> in Fig. 1), which is present in a relaxation oscillator to switch been charging and discharging, but is not present in ring oscillators [1]. During the calculation of this theoretical limit in [1], only the noise of the charging and discharging process was modeled, while comparator noise was neglected. This loop-comparator noise contribution turns out to be significant, and this paper will show how it can be prevented to translate into phase noise. Doing so, we aim to close the phase noise gap between practical relaxation oscillators and ring oscillators. The oscillator circuit and phase noise measurements were earlier reported in [7], but this paper provides a theoretical foundation, discusses a practical design strategy and reports some additional comparisons of measurements with simulation results.

The contents of this paper are organized as follows. In Section II we show how comparator noise can be prevented from contributing  $1/f^2$  phase noise. We analyze the remaining fundamental  $1/f^2$  colored phase noise contributions in a relaxation oscillator, i.e. the white noise of the charging and the discharging mechanism, and develop simple though precise phase noise expressions. Based on these expressions we devise a design strategy to maximize the phase noise performance. In Section III we will describe a new switched-capacitor relaxation oscillator topology [2] based on the developed insight and show that the simple phase noise expressions still hold for this topology. We then describe a transistor implementation in Section IV and explain how it can be designed to perform near to the theoretical FoM limit. In Section V we discuss measurement results, while Section VI draws conclusions.

# II. TOWARDS THE THEORETICAL LIMIT OF PHASE NOISE

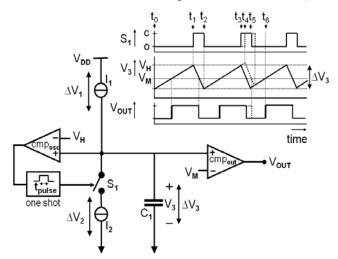

We will now discuss a technique which can prevent the noise of the oscillator loop-comparator from contributing 1/f² phase noise, so that its power consumption can be reduced. We will abandon the general relaxation oscillator topology of Fig. 1 based on resistors and use the topology given in Fig. 4, based on current sources instead (I-C relaxation oscillator). This topology shows a linear tuning range if the current sources are controlled linearly.

#### A. Eliminating the comparator noise

In the relaxation oscillator topology of Fig. 4, the charging mechanism is implemented by current source  $I_I$  that charges capacitor  $C_I$  continuously. As a result, the capacitor voltage  $V_3$  increases linearly in time and when it crosses  $V_M$ , an active edge is produced at  $V_{OUT}$ . When the capacitor voltage subsequently crosses  $V_H$ , the discharging mechanism is activated which discharges the capacitor by a fixed amount of charge. The discharging mechanism can be implemented by an "one-shot" (monostable circuit) that produces a pulse with fixed time-width in response to a trigger, in combination with an ideal current source  $I_2$ , which is also fixed. Assuming first a situation in which the comparator  $cmp_{osc}$  is noiseless, this discharging takes place in the interval  $[t_1, t_2]$  in Fig. 4.

Now suppose the comparator  $cmp_{osc}$  is noisy, i.e. the discharge pulse does not start at the nominal time  $t_3$ , but at a somewhat shifted instant  $t_4$  as shown in Fig. 4. Although the discharge ramp voltage is shifted, the rising edge of  $V_{OUT}$  still crosses  $V_M$  at the right time  $t_6$ . Thus the *active edge* is *unaffected* and so is the phase noise associated with the rising edge of  $V_{OUT}$ . Of course the falling edge is shifted (from  $t_4$  to  $t_5$ ), changing the duty cycle of  $V_{OUT}$ . This is acceptable in many applications that only use the

rising edge. If a reliable 50% duty is needed, this can be realized adding a divider triggered on rising oscillator edges while doubling the oscillator frequency. Of course, cmp<sub>out</sub> also adds noise, but this is white noise which is not integrated to  $1/f^2$  noise (to be discussed later).

Fig. 4: Current source based relaxation oscillator with rising output-edges insensitive to noise and delay of comparator cmp<sub>osc</sub>

In periodic steady-state, the charge flowing into the capacitor during a period of oscillation  $(T_{osc})$  is equal to the charge flowing out of the capacitor during the same period, i.e.  $Q_{in} = I_1 T_{osc} = Q_{out} = I_2 T_{pulse}$  or  $f_{osc} = I_1 / Q_{out}$ . By choosing  $Q_{out}$  fixed, the oscillation frequency is a linear function of  $I_1$  and independent of the delay and noise of  $cmp_{osc}$ .

Summarizing, if the discharge packet  $Q_{out}$  can be fixed, this technique effectively eliminates the noise contribution of the comparator. More precisely, it prevents the noise of the comparator  $cmp_{osc}$  to translate into  $1/f^2$  colored phase noise, i.e. prevents it to get integrated into the period of oscillation. This technique with one shot resembles the anti-jitter circuit technique [8], albeit for another application (reject jitter of an incoming clock signal by the use of an Frequency Locked Loop).

Taking a skeptic view, one might note that we shifted the problem of the noisy comparator to the one-shot that needs an accurate on-time to keep  $Q_{out}$  fixed. We will show in Section III though, that we can apply this technique without the need for this one-shot.

Before doing so, we will first calculate the theoretical phase noise performance limit for the circuit in Fig. 4, which uses current sources instead of resistors and will also devise a FoM-enhancement circuit design strategy.

## B. Noise current fed to a capacitor

The noise calculations that will follow all relate to the case where a noise current is fed to a C with parallel "leakage resistor" for some time, which will be analyzed first.

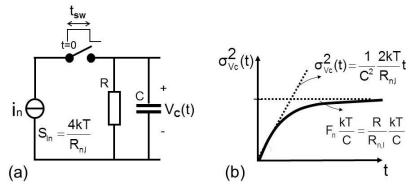

Fig. 5: a) Equivalent circuit for noise calculations; b) Variance of the capacitor voltage noise

In Fig. 5a, we see the RC circuit, which is assumed to be noiseless and initially fully discharged ("reset"). The white noise current  $i_n$  is modeled by parameter  $R_{n,I}$  (see Fig. 5a; note this is an *equivalent noise resistance*, not an impedance like R; only in specific cases it will be equal to R). Current  $i_n$  is fed to the RC network during switch conduction time  $t_{sw}$ . The resulting variance of the noise voltage across the capacitor can written as [2]:

$$\sigma_{\text{Vc}}^{2}(t) = F_{n} \frac{kT}{C} \left( 1 - e^{\frac{-2t}{RC}} \right) \begin{cases} t << RC \\ \approx F_{n} \frac{kT}{C} \frac{2t}{RC} = \frac{1}{C^{2}} \frac{2kT}{R_{n,I}} t \end{cases}$$

$$F_{n} = \frac{R}{R_{n,I}}$$

$$t >> RC \\ \approx F_{n} \frac{kT}{C} = \frac{R}{R_{n,I}} \frac{kT}{C}$$

$$0 \le t \le t_{\text{SW}}$$

$$(1)$$

where k is the Boltzmann constant, T is the absolute temperature and  $F_n$  is a dimensionless "excess noise factor", equal to the ratio of the resistance R and the equivalent noise resistance  $R_{n,I}$ , i.e.  $F_n = R / R_{n,I}$ . If the noise current is caused by the same resistance with which it is filtered (e.g. in Fig. 1), the noise excess factor will be unity.

Fig. 5b contains a plot of (1), in which we see that it takes some time before the variance of the capacitor voltage reaches its steady state value. Only after sufficient time, and if  $F_n=1$ , the well-known value kT/C arises. Intuitively, this steady-state results because, for a given time interval, the current source on average adds the same amount of noise charge to the capacitor as the resistor removes (charging and discharging noise contributions are then in equilibrium).

# C. Minimum period jitter of the oscillator

We will now calculate the minimum period jitter of the relaxation oscillator of Fig. 4. In this calculation, we presume that the noise sources can be considered small-signal and that the oscillator has reached a periodic steady-state (PSS). As motivated in the introduction, we only consider noise sources that cause  $1/f^2$  colored phase noise. The period jitter is calculated by accumulating the charge noise contributions to the main capacitor over a nominal oscillation period and converting the resulting voltage variance to time variance via the slew-rate [9]. For a rising edge which produces an output edge, we find:

$$\sigma_{J}^{2} = \frac{\sigma_{V_{C1,tot}}^{2}}{\left(\frac{dV_{C1}}{dt}\right)^{2}\Big|_{V_{L}=V}} = \frac{\sigma_{V_{C1,tot}}^{2}}{\left(\frac{I_{1}}{C_{1}}\right)^{2}} = \frac{\sigma_{Q_{C1,tot}}^{2}}{I_{1}^{2}}$$

(2)

The *minimum* period jitter of the oscillator will now be derived applying this to the topology in Fig. 4, where the jitter contributions of interest are the white noise sources of the charging current source  $I_I$ , the discharging current source  $I_2$ , the comparator  $cmp_{osc}$  and the one-shot<sup>2</sup>. The first two contributions are functionally required for timing and will fundamentally limit phase noise. We will show later that the latter two contribution can be eliminated. Evaluating (1) for  $I_1$  and  $I_2$  noise contributions to  $V_{C1}$ , gives:

$$\sigma_{V_{C_{1,1}}}^{2} \ge \frac{1}{C_{1}^{2}} \frac{2kT}{R_{n,11}} T_{osc}

\sigma_{V_{C_{1,2}}}^{2} \ge \frac{1}{C_{1}^{2}} \frac{2kT}{R_{n,12}} T_{pulse}$$

(3)

where  $R_{n,II}$  and  $R_{n,I2}$  are the equivalent noise resistances of current source  $I_1$  and  $I_2$ , respectively (see also Appendix B). Note that the charging current source  $I_I$  contributes noise during the entire oscillation period  $T_{osc}$ , while the discharging current source  $I_2$  contributes only during  $T_{pulse}$ . Note also that the upper approximation in (1) becomes exact for a relaxation oscillator containing an *ideal* current integrator, i.e. for  $R \rightarrow \infty$  [2]. As the contributions in (5) are uncorrelated, the total accumulated voltage noise variance can be written as:

<sup>&</sup>lt;sup>2</sup> Comparator/buffer *cmp<sub>out</sub>* is "outside the loop" and its noise is not integrated by the oscillator itself, i.e. does not contribute 1/f<sup>2</sup> phase noise.

$$\sigma_{V_{C1,tot}}^{2} \ge \sigma_{V_{C1,10}}^{2} + \sigma_{V_{C1,12}}^{2} \ge \frac{1}{C_{1}^{2}} \left( \frac{2kT}{R_{n,11}} T_{osc} + \frac{2kT}{R_{n,12}} T_{pulse} \right)$$

(4)

In Appendix B we show that for constant current I, reducing noise in a current source requires more voltage headroom  $\Delta V$ . Moreover, we show that practical MOS-current sources are noisier than a linear resistance, i.e.  $R_{n,I} < \Delta V / I$ , so that the latter equation should be used for deriving a (best case) theoretical FoM-limit. Doing so, using (4) and Q=C·V, the total accumulated charge noise variance in  $[C^2]$  becomes:

$$\sigma_{Q_{CI,tot}}^{2} = C_{1}^{2} \sigma_{V_{CI,tot}}^{2} \ge 2kT \left( \underbrace{I_{1} T_{osc}^{Q_{in}}}_{\Delta V_{1}} + \underbrace{I_{2} T_{pulse}}_{\Delta V_{2}} \frac{1}{\Delta V_{2}} \right)$$

$$(5)$$

where  $\Delta V_1$  and  $\Delta V_2$  are the voltage headroom "reserved" to realize current source 1 and 2 (see Fig. 4). As periodic steady-state oscillation implies  $Q_{in} = Q_{out}$ , the accumulated charge variance (5) can be written as:

$$\sigma_{Q_{C1,tot}}^2 \ge 2kT I_1 T_{osc} \frac{\Delta V_1 + \Delta V_2}{\Delta V_1 \Delta V_2}$$

(6)

Introducing an "effective reserved voltage headroom"  $\Delta V_{eff}$ :

$$\Delta V_{\text{eff}} = \frac{\Delta V_1 \, \Delta V_2}{\Delta V_1 + \Delta V_2} \tag{7}$$

and combining (2), (6) and (7), the relative period jitter variance can be written as:

$$\frac{\sigma_{J}^{2}}{T_{\text{osc}}^{2}} = \frac{\sigma_{Q_{\text{C1,tot}}}^{2}}{(I_{1} T_{\text{osc}})^{2}} \ge \frac{2kT f_{\text{osc}}}{\Delta V_{\text{eff}} I_{1}}$$

(8)

We see here that the period jitter due to noise from current sources, expressed as a fraction of the period time, is fundamentally limited by oscillation frequency, the value of the current and the effective voltage headroom available to realize the current sources. Clearly, high  $\Delta V_{eff}$  is good for jitter and  $1/f^2$  phase noise, maximizing headroom is crucial.

## D. Minimum FoM

We can now also calculate the minimum FoM of the relaxation oscillator of Fig. 4. In [3] it has been shown that:

$$\frac{\sigma_{\rm j}^2}{T_{\rm osc}^2} = N_{\rm osc} f_{\rm osc} \tag{9}$$

where  $\sigma_J/T_{osc}$  is the relative period jitter exclusively caused by the white noise sources that translate into  $1/f^2$  phase noise and where  $N_{osc}$  is the oscillated number, obtained from extrapolation of the  $1/f^2$  phase noise to  $f_{osc}$  as indicated in Fig. 2. Substituting (14) in (8), we get:

$$N_{osc} = \sigma_J^2 f_{osc} \ge \frac{2kT}{\Delta V_{eff} I_1}$$

(10)

Using (10), the FoM in Fig. 2 on linear scale becomes:

$$FoM = \sigma_J^2 f_{osc} \frac{P_{core}}{1mW} \ge \frac{2kT}{\Delta V_{osc}} \frac{P_{core}}{1mW}$$

(11)

Unlike the oscillator number, the FoM is typically bound by thermodynamics. Thus one can define a minimum FoM:  $FoM_{min}$ . As  $P_{core} = V_{DD} I_{core}$ , it can be written as:

$$FoM_{min} = min(FoM) = min\left(\frac{2kT}{1mW} \frac{V_{DD}}{\Delta V_{eff}} \frac{I_{core}}{I_{1}}\right)$$

(12)

As  $I_{core}$  includes  $I_I$  by definition, the optimal case occurs for  $I_{core} = I_I$ . Given (7), we conclude that  $\Delta V_{eff}$  is maximized when  $\Delta V_I = \Delta V_2 = V_{DD}/2$ . As a result, the minimum FoM of the topology in Fig. 4 can be written as:

$$FoM_{min} = 8 \frac{kT}{1mW} \qquad [Hz^{-1}]$$

(13)

This corresponds to -165dBc/Hz, the minimum value for I-C relaxation oscillators indicated in Fig. 3. Taking the ratio of this minimum FoM and the actually achieved FoM results in the *oscillator design efficiency* [10]:

$$ODE = \frac{FoM_{min}}{FoM}$$

(14)

This oscillator design efficiency quantifies the quality of the oscillator design regarding its  $1/f^2$  phase noise performance<sup>3</sup>. This design efficiency can be written as:

$$ODE = \frac{FoM_{min}}{FoM} = \frac{1}{4} \frac{V_{DD}}{\Delta V_{eff}} \frac{I_{core}}{I_{l}}$$

(15)

Both (12) and (22) are optimized if  $\Delta V_{eff}$  is maximized. From the topology in Fig. 4, we can observe that  $V_{DD} = \Delta V_1 + \Delta V_2 + \Delta V_3$ , in which  $\Delta V_3$  is the allowed voltage swing across the capacitor<sup>4</sup>. This leads to the counterintuitive conclusion that the  $1/f^2$  phase noise performance FoM and ODE of the topology in Fig. 4 is optimized if there is no voltage swing across the capacitor. For most types of oscillators, the oscillation amplitude is important for the  $1/f^2$  phase noise performance, for instance in LC oscillators [11]. However, for this specific type of relaxation oscillator that contains an ideal current integrator, the oscillation (voltage) amplitude is unimportant for the  $1/f^2$  phase noise performance. Inspecting (8) gives indicates why: it is the ratio of the stochastic and the deterministic charge contribution to the capacitor that matters. Capacitor size determines oscillation amplitude and the voltage headroom available for the current sources but does not affect this charge ratio. As  $N_{osc}$  and FoM are proportional to this charge ratio, while  $f_{osc}$  is cancelled combining (8) and (14), voltage swing nor capacitor size affects  $1/f^2$  phase noise.

However, there is more than  $1/f^2$  phase noise. While in a Phase Locked Loop,  $1/f^3$  noise can often be suppressed to an insignificant level [4], this is not true for the wideband white noise floor. For a given oscillation frequency and waveform, a decrease in amplitude means a decrease in slew-rate, degrading the phase noise floor caused by the *voltage-sensing* output comparator/buffer *cmp<sub>out</sub>*. Once again, note that this "output comparator/buffer" is *not* in the oscillator loop, hence its decisions are not memorized and integrated to  $1/f^2$  phase noise (white noise causes white phase noise). Minimizing the white noise floor means maximizing the slew-rate across the capacitor, i.e. maximizing the swing  $\Delta V_3$  in Fig. 4, which compromises the voltage headroom for current sources  $I_1$  and  $I_2$ . We conclude that this particular circuit does not allow for simultaneous optimization of the  $1/f^2$  and white phase noise. However, we will see in Section III that a change in topology does help.

#### E. Theoretical FoM limit equal to ring oscillator limit

The previous calculations show that the relaxation oscillator topology of Fig. 4 has a theoretical FoM limit (13) which is in decibel equal to -165dBc/Hz@290K. This phase noise performance limit is 4dB higher than that of the topology of Fig. 1 [1]. To get an intuitive feel for this difference note that the topology of Fig. 4 acts as an *ideal* current integrator, whereas the topology of Fig. 1 acts as a *leaky* current integrator, which "forgets" part of the charge noise during operation. Interestingly, the phase noise performance limit of the circuit in Fig. 4 is equal to that of ring oscillators [1].

# F. Design strategy to approach the theoretical FoM limit

Based on the insight developed above, the following design strategy to optimize overall phase noise performance of a relaxation oscillator is proposed:

1) Maximize both  $\Delta V_{eff}/V_{DD}$  and  $\Delta V_3$ , i.e. maximize the voltage headroom reserved for the charging and discharging currents on the one hand (for  $1/f^2$  noise), and the voltage swing across the capacitor on the

<sup>&</sup>lt;sup>3</sup> In [1] the inverse of the oscillator design efficiency is called the "wastefulness factor". Note also that lower FoM is better.

<sup>&</sup>lt;sup>4</sup> Note the difference between  $V_3$  and  $\Delta V_3$  in Fig.4:  $V_3$  is the actual voltage across capacitor  $C_1$  and  $\Delta V_3$  is the assigned voltage swing across capacitor  $C_1$  (a design choice;  $V_{3,max}$ - $V_{3,min}$  should always be larger than  $\Delta V_3$ ).

other (for white noise). Choose a circuit topology that allows for independent optimization, or, if a trade-off exists, balance noise contributions.

2) Maximize  $I_1/I_{core}$  so that current is mainly spend for the fundamentally required charging function. Remove the avoidable phase noise contribution of the loop comparator cmp<sub>osc</sub>, which relaxes its bias current requirements. Moreover, as comparator delay now no longer affects the period of oscillation, this will also improve frequency tuning linearity, as in the sawtooth oscillator proposed in [2][12][13].

## III. SWITCHED-CAPACITOR RELAXATION OSCILLATOR

We will now develop the switched-capacitor relaxation oscillator topology [7] step-by-step on the basis of the above design strategy. Afterwards we will show that expression (13) and this design strategy also hold for this new relaxation oscillator topology.

Fig. 6: A grounded capacitor is replaced by a charge-to-voltage converter, so that  $\Delta V_{\rm eff} = \Delta V_1 \Delta V_2 / (\Delta V_1 + \Delta V_2)$  and  $\Delta V_3$  can be maximized simultaneously.

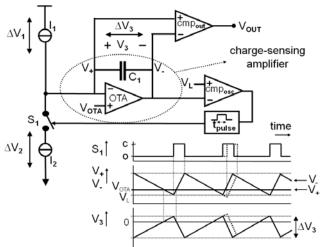

Fig. 7: Alternative discharging mechanism by a switchedcapacitor, which does not require an accurate one-shot time (current-limited OTA assumed for constant slopes)

#### A. Step-by-step development

As a first step, take the topology of Fig. 4 and replace the grounded capacitor by a charge-sensing amplifier (CSA), i.e. a charge-to-voltage converter as shown in Fig. 6. The OTA in this CSA turns capacitor-node  $V_+$  into a virtual ground node biased to  $V_{OTA}$ . This means that  $\Delta V_1 = V_{DD} - V_{OTA}$  and  $\Delta V_2 = V_{OTA}$ . Using (7), the maximum of  $\Delta V_{eff} / V_{DD}$  is 1/4 and is reached by choosing  $V_{OTA} = V_{DD}/2$ . The charging current source  $I_I$  is still charging the capacitor, but now via the OTA. As a result, the voltage at node  $V_-$  decreases linearly and when it crosses  $V_L$ , comparator  $cmp_{osc}$  issues a discharge signal. This signal activates the discharging mechanism which discharges the capacitor by a *fixed* amount of charge, again via the OTA. The allowed voltage swing across the capacitor can now be maximized as well, i.e.  $\Delta V_3 \approx V_{DD}$ . Note furthermore that the output comparator/buffer  $cmp_{out}$  does not need an additional reference voltage now (which can be noisy) as the capacitor voltage can be sensed differentially. This intermediate topology allows maximizing  $\Delta V_{eff}/V_{DD}$  and  $\Delta V_3$  simultaneously (goal 1 in section II-F).

As a second step, observe that the combination of current  $I_2$  and one-shot time  $t_2$  effectively removes a charge packet  $I_2t_2$  from capacitor  $C_1$ . Realizing an accurate one-shot time is a challenge especially with low jitter. However, the discharge charge packet can also be implemented by a (switched-) capacitor in combination with the OTA, as shown in Fig. 7.

The operation of this discharging mechanism is as follows. At the beginning of the oscillation period, capacitor  $C_2$  is discharged to ground. When comparator  $cmp_{osc}$  issues signal X (discharge  $C_1$ ), capacitor  $C_2$  is connected to node  $V_+$  (virtual ground node of the OTA) and is charged from 0 to  $V_{OTA}$  by current source  $I_1$  together with the OTA. During this action, capacitor  $C_1$  is discharged by *a fixed* charge packet of  $C_2V_{OTA}$ . Still, as for Fig. 4, the noise of comparator  $cmp_{osc}$  does not matter (see Fig. 7).

Although the switched-capacitor topology does not contain a one-shot, it does contain an additional OTA (which can be noisy as well). In Section IV we will show that part of the noise of this OTA is prevented to translate into colored  $1/f^2$  phase noise by the settling/filtering of capacitor  $C_2$ . In Appendix C, it is shown that the minimal phase noise contribution of this switched-capacitor discharging mechanism is equal to that of the original discharging mechanism so that expression (13) and the design strategy of section II-F still applies. Voltage  $\Delta V_2$  can now be interpreted as the allowed voltage swing across capacitor  $C_2$ . Note that for the topology of Fig. 7 still  $\Delta V_1 = V_{DD} - V_{OTA}$ ,  $\Delta V_2 = V_{OTA}$  and  $\Delta V_3 \approx V_{DD}$  holds, just like for Fig. 6.

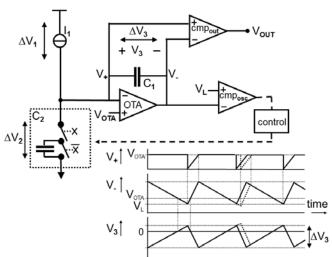

A final improvement step is to reverse the switched-capacitor instead of discharging it to ground, see Fig. 8. When comparator  $cmp_{osc}$  issues a discharge signal, a divide-by-two is toggled (toggle control block) and capacitor  $C_2$  is reversed.  $C_2$  is now charged from  $-V_{OTA}$  to  $+V_{OTA}$  by current source  $I_1$  and the OTA and capacitor  $C_1$  is discharged by a fixed discharge packet of  $2C_2V_{OTA}$  (doubled compared to Fig. 7). This means that  $\Delta V_1 = V_{DD} - V_{OTA}$ ,  $\Delta V_2 = 2V_{OTA}$  and  $\Delta V_3 \approx V_{DD}$ , i.e. this final topology allows for doubling  $\Delta V_2$  and hence  $\Delta V_{eff} / V_{DD}$  without increasing current consumption ( $C_1$ -discharge time defines the required current, to maintain voltage waveforms of Fig. 7,  $C_2$  needs to be halved for Fig. 8).

In Section IV we will show how a switched-capacitor relaxation oscillator can be implemented without much overhead, but first we coarsely estimate performance.

Fig. 8: Switched-capacitor oscillator in which  $C_2$  is reversed (flipped) to increase  $\Delta V_{eff}$  (OTA is current-limited)

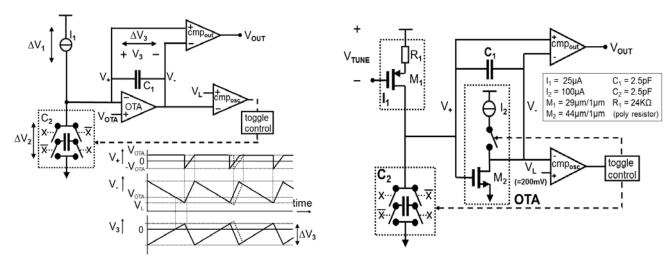

Fig. 9: Implementation of the switched-capacitor relaxation oscillator.

# B. Comparison of typical phase noise performance

To get some feeling for the practical achievable phase noise performance, consider Fig. 4 and assume  $V_{DD}$  is equally divided over charging, discharging and signal swing, i.e.  $\Delta V_1 = \Delta V_2 = \Delta V_3 = V_{DD}/3$ , so  $\Delta V_{eff}/V_{DD} = 1/6$ . The current consumption is at least  $I_{core} = I_1$ , which does not include the current consumption of the one-shot.

For the topology of Fig. 8, as  $\Delta V_I = V_{DD} - V_{OTA}$  and  $\Delta V_2 = 2V_{OTA}$ , the maximum of  $\Delta V_{eff}$  occurs for  $V_{OTA} = (\sqrt{2} - I)V_{DD}$ . A close choice for the OTA reference voltage, which is still nearly optimal and gives easy comparison numbers is  $V_{OTA} = V_{DD}/3$ . A practical OTA circuit would furthermore limit the swing across capacitor  $C_I$ , e.g. to  $\Delta V_3 = 2V_{DD}/3$ . This would mean  $\Delta V_I = \Delta V_2 = \Delta V_3 = 2V_{DD}/3$ , so  $\Delta V_{eff}/V_{DD} = 1/3$ . If the OTA is class-A and is able to discharge  $C_1$  in the same time it is charged, an OTA bias-current equal to  $I_I$  is required, i.e. the total core current consumption is at least  $I_{core} = 2I_I$ . Note that this *does* include all the dominant sources of current consumption, in contrast to the one-shot case in Fig. 4.

Comparing the above predicted phase noise of the two circuits, neglecting the one-shot contribution, we find an equal FoM = -163dBc/Hz at 290K, which is indeed close to the theoretical best value of -165dBc/Hz (Fig. 3). However, to make the phase noise contribution of the one-shot in the topology of Fig. 4 insignificant, its current consumption will be significant, seriously degrading FoM. This in contrast to the calculation for Fig. 8 in which we already accounted for OTA-current. From a FoM

perspective, the situation is now somewhat similar to ring oscillators, where the "inverter" transistors not only implement the charging and discharging function, but also the toggling between the two states. Thus there is no additional noise for this "comparator" function as for the circuit in Fig. 8.

#### IV. TRANSISTOR IMPLEMENTATION

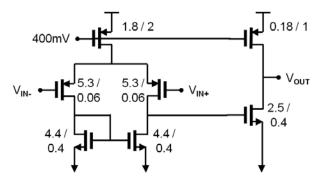

To demonstrate in practice that we can come close to the theoretical minimum FoM of -165dBc/Hz for I-C relaxation oscillators (eqn.13), we will now design a transistor circuit implementation. Fig. 9 shows a transistor implementation of the switched-capacitor relaxation oscillator topology of Fig. 8. Component values are equal to the case described in Section III-B, i.e.  $\Delta V_1 = \Delta V_2 = \Delta V_3 = 2V_{DD}/3$ , meaning  $\Delta V_{eff} = V_{DD}/3$ . The frequency control linearity and output resistance of current source  $I_I$  should both be high and it is therefore implemented by a long PMOST that is heavily resistively degenerated. The voltage across the resistor is approximately  $V_{RI} = V_{DD}/2$  and the drain-source voltage is  $\Delta V_{I} = V_{DD}/6$ . This thick gate-oxide PMOST allows for both setting  $V_{DSsat} = V_{DD}/6$  and  $V_{TUNE} = V_{DD}$  at the maximum oscillation frequency. The noise performance of this current source approaches that of a linear resistance. To tune the oscillation frequency we change  $V_{TUNE}$ , i.e. we implement a voltage-controlled oscillator. However, reducing  $V_{TUNE}$  significantly deteriorates the noise performance as we use less  $\Delta V$  ("throw away" available headroom). Noise performance could be maintained by splitting current source  $I_I$  into many small current sources, all biased at  $V_{TUNE} = V_{DD}$ , selecting them digitally (digitally-controlled oscillator).

To reduce power consumption during charging, the NMOST in the OTA implementation is biased exclusively by current source  $I_I$  through  $C_I$  such that  $V_{GS} = V_{OTA} = \Delta V_2 / 2 = V_{DD} / 3$ . Only when V. crosses  $V_L = V_{DD} / 6$  and comparator  $cmp_{osc}$  issues a  $C_1$ -discharge signal, current source  $I_2$  in the OTA, implemented by a PMOST, is on for activation time  $T_{act} < T_{osc}$ . It supplies a *fixed* discharging current  $I_2 = I_1 T_{osc} / T_{act}$ . As  $T_{act}$  is independent of frequency and is not very critical, it was implemented by a fixed RC delay. Note that this RC delay does not have to be accurate as opposed to the pulse width of the one-shot. To allow  $\Delta V_3 = 2V_{DD} / 3$ , both the NMOST and PMOST (realizing  $I_2$ ) in the OTA are biased near weak-inversion. Such a basic implementation of the charge-sensing amplifier has some attractive characteristics: it only consumes  $I_I$ , it results in a low excess noise factor and it has a low closed-loop input impedance ( $I/g_{m2}$ ). This input impedance should be low such that the voltage on capacitor  $C_2$  is allowed to settle accurately between the moment that current source  $I_2$  is deactivated and the moment that capacitor  $C_2$  is reversed again ( $C_2/g_{m2} << T_{osc,min} - T_{act}$ ).

The non-linearity of the OTA, i.e. the non-linearity of the gate-source voltage of transistor  $M_2$  versus  $I_1$  in Fig. 9, can largely compensate the non-linearity of the  $V_{TUNE}$ - $I_1$  relation (assuming square-law devices, they are inverse functions<sup>5</sup>). Put differently, their effect on oscillation frequency is opposite:  $Q_{in} = I_1(V_{TUNE})T_{osc} = Q_{out} = 2C_2V_{GS2}(I_1)$ .

Fig. 10: Transistor implementation of the oscillator comparator (cmp<sub>osc</sub>).

As mentioned briefly in Section III, part of the noise of the OTA is prevented to translate into colored phase noise, namely the noise of  $I_2$  contributed during discharging. To understand why, first note that

<sup>&</sup>lt;sup>5</sup> Only during chip measurements we realized this linearization exists but we didn't design for it.

$T_{act}$ , the activation time of current source  $I_2$ , is chosen small enough to allow the voltage on capacitor  $C_2$  to fully settle to  $V_{GS2}(I_1)$  during the rest of the oscillation period  $T_{osc}$ - $T_{act}$ . During this settling, the noise charge contribution on  $C_1$  originating from discharge current  $I_2$  has enough time to leak away (via output resistances of current sources). By the time capacitor  $C_2$  is reversed again, its contribution to the  $1/f^2$  colored phase noise can be negligible. This means that only the noise of the NMOST in the OTA implementation contributes to  $1/f^2$  colored phase noise as further detailed in Appendix C.

We will now calculate the process technology and application specific dimensioning. The available 65nm CMOS process sets  $V_{DD}=1.2V$ . As we aim to demonstrate low phase noise at high power efficiency, we aim for a low frequency application in which the required power is set by noise requirements, and not by speed requirements. The target application that we used as a proof-of-concept application (a digital audio application) sets  $f_{osc,max}=12.5MHz$  and  $N_{osc}=-151dBc/Hz$  at 290K, which is equivalent to about 100ppm relative period jitter. According to (10) this results in  $I_1=2kT/(\Delta V_{eff}N_{osc})=25\mu A$ . Periodic steady-state furthermore implicates  $Q_{in}=I_1$   $T_{osc}=Q_{out}=C_2\Delta V_2$ , meaning  $C_2=I_1/(f_{osc}\Delta V_2)=2.5pF$ . We choose  $T_{act}=1/(4 f_{osc,max})=20ns$  to allow sufficient time for the settling of capacitor  $C_2$ , even at the maximum oscillation frequency. This results in  $I_2=I_1T_{osc}/T_{act}=100\mu A$ . Finally we set  $\Delta V_3$  by choosing  $C_1=(\Delta V_2/\Delta V_3)C_2=2.5pF$ .

The oscillator comparator and its reference are designed to consume about  $10\mu A$  and  $5\mu A$ , respectively. Fig. 10 shows the transistor implementation of the oscillator loop-comparator ( $cmp_{osc}$  in Fig. 9). The output comparator/buffer is designed to drive  $50\Omega$  phase noise measurement equipment and therefore consumes about 2.5mA, but this could be reduced to  $10\mu A$  if we would drive an on-chip inverter chain. The circuitry to switch  $I_2$  and reverse  $C_2$  reliably consumes about  $5\mu A$ . As a result,  $I_{core} = 70\mu A = 2.8I_1$ . According to (11) the FoM is expected to be -161.7dBc/Hz at 290K. In terms of the oscillator design efficiency in (22) this means ODE=-4dB, i.e. this implementation of the topology of Fig. 8 shows a  $1/f^2$  phase noise performance that is only 4dB from its theoretical limit. Further simulation results will now be presented in Section V as well as measurement results.

#### V. IC IMPLEMENTATION AND MEASUREMENTS

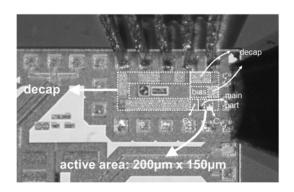

We will now discuss measurements that demonstrate correct functional operation of the oscillator and a noise performance close to the theoretical prediction. Fig. 11 shows the baseline 65nm LP CMOS implementation of the switched-capacitor relaxation oscillator of Fig. 9. The circuit is measured using a battery supply and probes. Fig. 12 and Fig. 13 show the simulated and measured waveforms respectively.

Fig. 11: Die micrograph of baseline 65nm LP CMOS design.

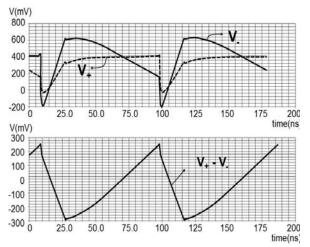

Fig. 12: Simulated waveforms for the oscillator in Fig. 9.

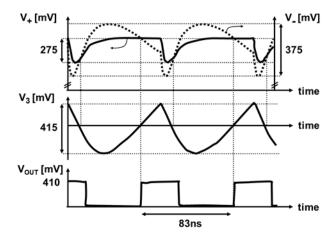

Fig. 13: Measured waveforms for the oscillator in Fig. 9.

These waveforms differ somewhat, and detailed analysis shows this is because current source  $I_2$  is active for somewhat less than  $T_{osc}I_1/I_2$ . This can be easily corrected in a re-design and hardly affects the phase noise performance.

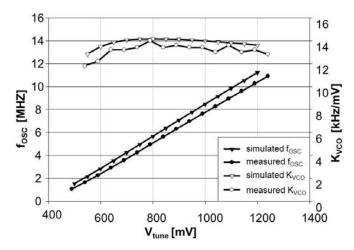

Fig. 14 shows that the frequency tuning range is both large and linear: 1-11MHz. Measured frequencies are slightly lower than simulated.

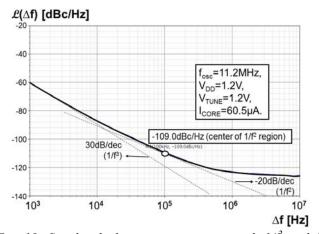

In Fig. 15 the simulated phase noise is plotted, at the maximum frequency  $f_{osc}$ =11.2MHz for  $V_{DD}$ =1.2V. In the center of the  $1/f^2$  region, we find  $\mathcal{L}(100\text{kHz})$ =-109dBc/Hz at 60.5 $\mu$ A@1.2V. Substitution in eqn.(22) renders a FoM of -161.4dBc/Hz at 290K, which is very close to the -161.7dBc/Hz predicted in Section II-E. The simulated  $1/f^3$  corner frequency is about 10kHz.

Fig. 16 provides a detailed summary of the contributors to the simulated phase noise. At 100KHz, nearly all the 1/f² phase noise is indeed caused by the charging and discharging mechanisms and only a few % by the loop-comparator. Explorative simulations have shown that the jitter produced by the same comparator, when applied in the traditional oscillator of Fig. 1 without the "trick" of Fig. 4, would add more 1/f² phase noise than all other noise sources together. The fact that the loop-comparator has high noise is still evident from its high contribution to the white-noise phase noise floor at 1MHz (last column in Fig. 16; 66.37% contribution).

Fig. 14: Simulated and measured frequency tuning range and frequency tuning gain (R&S FSP spectrum analyzer).

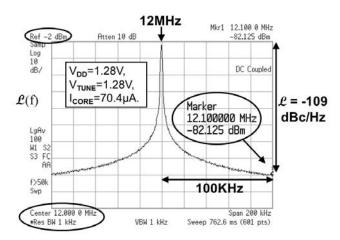

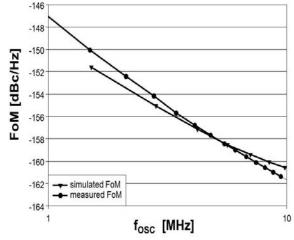

Fig. 17 shows the measured output spectrum at 12MHz measured with a 1.28V battery. Using the data a 100kHz offset frequency, the FoM is -161dBc/Hz, which fits well to both theory and simulation results mentioned in the previous paragraph. Fig. 18 shows how this FoM varies over the tuning range. The

FoM deteriorates for lower oscillation frequencies as expected, as discussed in the first paragraph of section IV. Ten samples have been measured and all have similar FoMs. This FoM is only 4dB from the theoretical limit of this topology and to date still is the best reported one as shown in Fig. 19 (although more recent designs are quite close). It is also similar to that of state-of-the-art ring oscillators [1] (see also Fig. 3).

| contributor           | £(1K) (%)                                                                                                                                                        | £(10K) (%)                                                                                                                                                                                                                                                                                                                                            | £(100K) (%)                                                                                                                                                                                                                                                                                                                                                                                                                                                          | £(1M) (%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R1 - flicker          | 0,74                                                                                                                                                             | 0,38                                                                                                                                                                                                                                                                                                                                                  | 0,06                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ~ 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| R1 - thermal          | 4,12                                                                                                                                                             | 20,61                                                                                                                                                                                                                                                                                                                                                 | 33,92                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9,03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| M1 - flicker          | 43,76                                                                                                                                                            | 22,42                                                                                                                                                                                                                                                                                                                                                 | 3,60                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0,10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| M1 - thermal          | 0,57                                                                                                                                                             | 2,85                                                                                                                                                                                                                                                                                                                                                  | 4,69                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1,24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| M2 - flicker          | 39,14                                                                                                                                                            | 20,07                                                                                                                                                                                                                                                                                                                                                 | 3,26                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0,11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| M2 - thermal          | 4,08                                                                                                                                                             | 20,37                                                                                                                                                                                                                                                                                                                                                 | 33,30                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9,03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| switches C2 - thermal | 1,72                                                                                                                                                             | 8,55                                                                                                                                                                                                                                                                                                                                                  | 13,96                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3,88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| cmposc - flicker      | 4,28                                                                                                                                                             | 2,22                                                                                                                                                                                                                                                                                                                                                  | 0,74                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1,35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| cmposc - thermal      | 0,30                                                                                                                                                             | 1,53                                                                                                                                                                                                                                                                                                                                                  | 5,03                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 66,37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| bias cmpose - thermal | 0,05                                                                                                                                                             | 0,19                                                                                                                                                                                                                                                                                                                                                  | 0,67                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7,03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| rest                  | 1,29                                                                                                                                                             | 0,81                                                                                                                                                                                                                                                                                                                                                  | 0,77                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1,86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| total                 | 100                                                                                                                                                              | 100                                                                                                                                                                                                                                                                                                                                                   | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                       | (1/f3 region)                                                                                                                                                    | (transition)                                                                                                                                                                                                                                                                                                                                          | (1/f2 region)                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (white floor)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       | R1 - flicker R1 - thermal M1 - flicker M1 - thermal M2 - flicker M2 - thermal switches C2 - thermal cmposc - flicker cmposc - thermal bias cmposc - thermal rest | R1 - flicker     0,74       R1 - thermal     4,12       M1 - flicker     43,76       M1 - thermal     0,57       M2 - flicker     39,14       M2 - thermal     4,08       switches C2 - thermal     1,72       cmposc - flicker     4,28       cmposc - thermal     0,30       bias cmposc - thermal     0,05       rest     1,29       total     100 | R1 - flicker     0,74     0,38       R1 - thermal     4,12     20,61       M1 - flicker     43,76     22,42       M1 - thermal     0,57     2,85       M2 - flicker     39,14     20,07       M2 - thermal     4,08     20,37       switches C2 - thermal     1,72     8,55       cmposc - flicker     4,28     2,22       cmposc - thermal     0,30     1,53       bias cmposc - thermal     0,05     0,19       rest     1,29     0,81       total     100     100 | R1 - flicker         0,74         0,38         0,06           R1 - thermal         4,12         20,61         33,92           M1 - flicker         43,76         22,42         3,60           M1 - thermal         0,57         2,85         4,69           M2 - flicker         39,14         20,07         3,26           M2 - thermal         4,08         20,37         33,30           switches C2 - thermal         1,72         8,55         13,96           cmposc - flicker         4,28         2,22         0,74           cmposc - thermal         0,30         1,53         5,03           bias cmposc - thermal         0,05         0,19         0,67           rest         1,29         0,81         0,77 |

Fig. 15: Simulated phase noise spectrum with  $1/f^2$  and  $1/f^2$  asymptotes

Fig. 16: Simulated phase noise summary

Fig. 18: Simulated and measured phase noise FoM (evaluated in the  $1/f^2$  region) vs. oscillation frequency

Fig. 19: Phase noise FoM of previous relaxation oscillator designs.

#### VI. CONCLUSIONS

We have shown that the comparator in an relaxation-oscillator loop can be prevented from contributing to  $1/f^2$  colored phase noise and degrading control linearity. We described a relaxation oscillator topology that does this in a power-efficient way, leaving only the white noise of the charging and the discharging mechanism to contribute significantly to  $1/f^2$  phase noise. We derived simple though precise expressions that predict the theoretical phase noise performance limit of these relaxation oscillators and a proposed a design strategy to approach this limit.

A 65nm CMOS implementation shows a large and linear frequency tuning range of 1-11MHz. The phase noise FoM is -161dBc/Hz at room temperature, only 4dB from the theoretical limit of this topology. This FoM is similar to that of state-of-the-art ring oscillators, but this relaxation oscillator also features a linear control characteristic.

#### VII. APPENDICES

## A. Jitter and Phase Noise metrics

Timing uncertainty or frequency instability can be described in different ways, and can be related to each other under certain condition that we will summarize briefly here. Suppose we compare an ideal zero-jitter clock with a practical jittery one, where timing deviations compared to the ideal clock are denoted  $\Delta t$ . Three common jitter metrics are now: *absolute* jitter  $\sigma_A$ , *period* jitter  $\sigma_J$  and *adjacent period* jitter  $\sigma_{\Delta J}$  [23]. These refer to the standard deviation of these 0-th, 1<sup>st</sup> and 2<sup>nd</sup> order differences, respectively:

$$\sigma_{A} = \sqrt{E[(\Delta t)^{2}]}$$

(16)

$$\sigma_{\rm J} = \sqrt{E\left[\left(\Delta t_{\rm N} - \Delta t_{\rm N-1}\right)^2\right]} \tag{17}$$

$$\sigma_{\Delta J} = \sqrt{E[(\Delta t_{N} - \Delta t_{N-1})]}$$

$$\sigma_{\Delta J} = \sqrt{E[((\Delta t_{N} - \Delta t_{N-1}) - (\Delta t_{N-1} - \Delta t_{N-2}))^{2}]}$$

(18)

where index N identifies the N-th timing deviation, i.e. the N-th threshold-crossing. Period jitter is sometimes also called cycle-jitter and adjacent period jitter also cycle-to-cycle jitter. Although these jitter metrics are very useful in the time-domain, they do not provide much information regarding the spectral distribution or single-sideband phase noise  $S_{\phi}(f)$ . As measuring the amplitude power spectral density  $S_X(f)$  is often easier, the single-sideband metric  $\mathcal{L}(f)$  is commonly used, which can be related to  $S_X(f)$ , power of the carrier  $P_s$  and phase noise as:

$$\mathcal{L}(f) = \frac{S_X(f_c + f)}{P_s} \approx \frac{S_{\Phi}(f)}{2}$$

(19)

where the approximation holds for  $f_{crL} << f << f_c$  [5], in which  $f_{crL}$  is the linewidth of the oscillator and  $f_c$  the oscillation frequency. As motivated in the introduction, the  $1/f^2$  noise often dominates, in which case [5]:

$$\frac{\sigma_{\rm J}^2}{T_{\rm osc}^2} = N_{\rm osc} f_{\rm osc} \tag{20}$$

where  $T_{osc}$  is the period of oscillation and  $\sigma_J / T_{osc}$  is the relative period jitter exclusively caused by the white noise sources that translate into  $1/f^2$  phase noise, and where  $N_{osc}$  is the oscillator number [5]:

$$N_{osc} = \mathcal{L}(f_{f-2}) \left(\frac{f_{f-2}}{f_{osc}}\right)^2$$

(21)

where  $f_{f-2}$  is equal to a frequency offset somewhere in the  $1/f^2$  region (see Fig. 2) and  $f_{osc}$  is the oscillation frequency. The oscillator number can be thought of as an extrapolation of the  $1/f^2$  region at an offset frequency equal to the oscillation frequency, see Fig. 2. The oscillator number specifies the  $1/f^2$  phase noise behavior and provides an indication of how difficult it is to achieve, by normalizing for offset and oscillation frequency. It can also be shown that the oscillator number is equal to the phase diffusion coefficient associated with white noise, i.e.  $c_w$  in [5].

Normalizing the oscillator number to the power consumption of the oscillator core  $P_{core}$  (excluding 14

auxiliary output buffers) renders the well-known FoM [5][6]:

$$FoM = \mathcal{L}(f_{f-2}) \left(\frac{f_{f-2}}{f_{osc}}\right)^2 \frac{P_{core}}{1mW} = N_{osc} \frac{P_{core}}{1mW}$$

(22)

This FoM quantifies the oscillator's  $1/f^2$  phase noise performance, taking into account power consumption. We will use this for benchmarking the oscillators. The ratio of the performance of a given oscillator topology (FoM) and the target phase noise specification ( $N_{osc}$ ) gives an indication of the necessary power consumption ( $P_{core}$ ).

# B. Noise behavior of practical CMOS current sources

Relaxation oscillators require a charge current which also produces noise. In this section we model the noise performance of a resistor and MOS transistor (MOST) based current source and relate it to the bias current I and voltage headroom  $\Delta V$ . We will show that for a fixed bias current, lowering noise requires more voltage headroom  $\Delta V$  and that the resistor achieves the best noise performance.

For a simple resistor R with only thermal noise, the equivalent noise resistance  $R_n=R$ , which is also equal to  $R_n=\Delta V/I$ . The equivalent current noise of this resistance is:

$$\sigma_{I,Rn}^2 = \frac{4kT}{R_n} \Delta f = \frac{4kT \cdot I}{\Delta V} \Delta f \tag{23}$$

For a MOST in strong inversion with a square-law characteristic, the noise current variance can be written in the following form [24]:

$$\sigma_{I,\text{thermal}}^{2} = 4kT\gamma \cdot g_{m}\Delta f = 4kT\gamma \frac{2I_{D}}{V_{GT}}\Delta f \ge 2\gamma \frac{4kT \cdot I}{\Delta V}\Delta f \tag{24}$$

With  $\gamma$ =2/3 for a long channel transistor, while practical sub-micron transistor typically show a  $\gamma$  in the range of 1-1.5. To minimize noise current variance, we want a low  $g_m$ , which implies high  $V_{GT}$  and high headroom  $\Delta V$ , if the current is fixed. The minimum voltage headroom to be reserved to keep a MOST in saturation is  $\Delta V \ge V_{GT}$ . Comparing (21) to (24), we conclude that the noise performance of such a current source implementation is at least  $2\gamma$  times worse than (24). Furthermore, note that both (24) and (21) are proportional to  $I/\Delta V$ , i.e. for a fixed bias current, lowering noise requires more voltage headroom.

For a MOST in weak inversion, a few times kT/q is needed as voltage headroom and the noise due to shot noise is:

$$\sigma_{I,Shot}^2 = 2qI\Delta f = 4kT \frac{qI}{2kT}\Delta f \tag{25}$$

This noise performance is only better than (24) and (21) if  $\Delta V < 2kT/q$ , but for such a low  $\Delta V$  the MOST in weak inversion does work as current source. Note furthermore that this conclusion also holds for a current source consisting of a BJT. If more voltage headroom that 2kT/q is available, it is a good idea to resistively degenerate the above transistor implementations of a current source<sup>6</sup>. The noise performance of such a current source implementation would still ultimately be limited by the degeneration resistance though and will not be lower than (24). Thus we conclude that (24) renders the best case noise, i.e. if we want to lower noise for a current source with current I, we need to "reserve more voltage headroom  $\Delta V$ ". As (24) renders the best case noise, it constitutes a good basis for deriving fundamental limits in phase noise of current-source based oscillators.

## C. Switched-capacitor relaxation oscillators

We will now show the validity of the derived phase noise expressions for the switched-capacitor relaxation oscillator topology of Fig. 7. As the charging mechanism is still implemented by current source  $I_I$ , the noise variance of the charging mechanism is still given by the upper part of (5). So we

<sup>&</sup>lt;sup>6</sup> Note that this also increases output resistance and lowers 1/f noise of the current source, as resistors show much lower 1/f noise than MOSFETs.

only have to show that the minimal phase noise contribution of the switched-capacitor discharging mechanism in Fig. 7 is equal to that of the original discharging mechanism, i.e. current source  $I_2$  in Fig. 4. This is done, by applying eqn. (1) of Section II three times.

At the beginning of an oscillation period, the switched-capacitor  $C_2$  is reset to ground via a resistive switch which is on for sufficient time to result in the steady-state voltage variance kT/C. Thus  $F_n=1$  ( $R_{n,I}=R$ ), and (1) converted to charge variance becomes  $kTC_2$ . After connecting  $C_2$  to node  $V_+$  and allowing the capacitor voltage sufficient time to settle to  $V_{OTA}$ , the additional charge noise variance due to the charging current noise becomes  $F_nkTC_2$ , in which the excess noise factor  $F_n$  depends on the specific implementation of the OTA. If we implement the OTA as shown in Fig. 10, with a single transistor  $M_2$ , it can be considered as a noise current source as in the model of Fig. 5. Treating it as other current sources we again take  $F_n=1$  as the best case for the derivation of the fundamental FoM-limit. Assuming the noise contributions are uncorrelated, the lower limit of total charge noise variance becomes 2 times  $kTC_2$  plus the contribution of the charging mechanism:

$$\sigma_{Q_{C1,tot}}^{2} \ge \frac{2kT}{R_{n,11}} T_{osc} + 2kTC_{2} = 2kT \left( \overline{I_{1}} T_{osc} \frac{1}{\Delta V_{1}} + \frac{Q_{out}}{\Delta V_{2}} \right)$$

$$= 2kT I_{1} T_{osc} \frac{\Delta V_{1} + \Delta V_{2}}{\Delta V_{1} \Delta V_{2}}$$

(26)

Where we again use the condition that  $Q_{in}=Q_{out}$  for steady state oscillation. This result is equal to (6) and we can then apply the theory of section II also for this switched-capacitor relaxation oscillator.  $\Delta V_1$  and  $\Delta V_2$  now have the more general meaning of the voltage headroom reserved for the charging and discharging mechanism respectively. Showing the validity of the used phase noise expressions for the switched-capacitor relaxation oscillator topology of Fig. 8 is similar and results in (25) as well.

#### VIII. ACKNOWLEDGMENTS

First of all, the authors would like to thank Sander Gierkink for his greatly appreciated contribution. We would also like to thank NXP Semiconductors for chip fabrication and D. Leenaerts and C. Vaucher for useful discussions.

# IX. REFERENCES

- [1] R. Navid, T. H. Lee, R. W. Dutton, "Minimum Achievable Phase Noise of RC Oscillators," *IEEE J. Solid-State Circuits*, vol. 40, no. 3, pp. 630-637, Mar. 2005.