Received 4 September, 2014; revised 20 February, 2015; accepted 24 February, 2015. Date of current version 22 April 2015.

The review of this paper was arranged by Editor Y.-C. Yeo.

Digital Object Identifier 10.1109/JEDS.2015.2409303

# On Device Architectures, Subthreshold Swing, and Power Consumption of the Piezoelectric Field-Effect Transistor ( $\pi$ -FET)

RAYMOND J. E. HUETING<sup>1</sup> (Senior Member, IEEE), TOM VAN HEMERT<sup>1,3</sup>, BUKET KALELI<sup>1,3</sup>, ROB A. M. WOLTERS<sup>1,2</sup>, AND JURRIAAN SCHMITZ<sup>1</sup> (Senior Member, IEEE)

<sup>1</sup> MESA+ Institute for Nanotechnology, University of Twente, Enschede 7500AE, The Netherlands

<sup>2</sup> NXP Semiconductors, Eindhoven 5656 AA, The Netherlands

<sup>3</sup> Now at ASML, Veldhoven 5504 DR, The Netherlands

CORRESPONDING AUTHOR: R. J. E. HUETING (e-mail: r.j.e.hueting@utwente.nl)

This work was supported in part by the Dutch Technology Foundation Stichting Toegepaste Wetenschappen (STW), an Applied Science Division of Nederlandse organisatie voor Wetenschappelijk Onderzoek (NWO), and in part by NanoNextNL, a Micro and Nanotechnology Programme of the Dutch Ministry of Economic Affairs,

Agriculture and Innovation (EL&I) and 130 partners.

**ABSTRACT** This paper describes the potential of tunable strain in field-effect transistors to boost performance of digital logic. Voltage-controlled strain can be imposed on a semiconductor body by the integration of a piezoelectric material improving transistor performance. In this paper, we derive the relations governing the subthreshold swing in such devices to improve the understanding. Using these relations and considering the mechanical and technological boundary conditions, we discuss possible device architectures that employ this principle. Further, we review the recently published experimental and modeling results of this device, and give analytical estimates of the power consumption.

INDEX TERMS Piezoelectric effect, MOSFET, CMOS, subthermal device, steep-subthreshold device.

## I. INTRODUCTION

In recent years, the performance improvement of transistors from generation to generation has slowed down, as a result of lagging gate length scaling. So-called performance boosters have been introduced in Complementary Metal-Oxide-Semiconductor (CMOS) technology to further improve the circuit performance in new process generations [1]. These performance boosters include metal-gate-high-k stacks [2], [3], channel strain [4]–[6], and ultra-thin body configurations (e.g., ultra-thin body silicon-on-insulator substrates [7] and FinFETs [8], [9]). Both higher on-currents and lower off-currents are achieved through these measures.

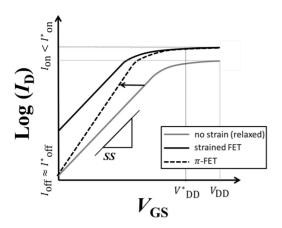

For the further advancement of CMOS, devices must exhibit a high on/off ratio at low power supply voltage. The key limiting factor in conventional MOS transistors is the subthreshold swing (SS), see also Fig. 1, defined as [10]:

$$SS \equiv \frac{dV_{\text{GS}}}{d\log(I_{\text{D}})} = \frac{dV_{\text{GS}}}{d\ln(I_{\text{D}})} \cdot \ln(10) = m \cdot u_T \cdot \ln(10), \quad (1)$$

where  $V_{GS}$  is the gate-source voltage,  $I_D$  is the drain current,  $u_T$  is the thermal voltage, and m is the ideality factor.

In a classical FET the subthreshold swing is limited by diffusion of charge carriers and is  $\geq$ 60 mV/dec at room temperature whereas for future CMOS a lower, i.e., subthermal, SS, is required. Several device concepts aiming at a subthermal SS have been proposed and are currently under investigation; see [11]–[19] and the other articles of this Special Issue.

In recent articles we proposed the addition of piezoelectric material to the FinFET as a further performance booster [20], [21]. In this device, dubbed  $\pi$ -FET, the converse piezoelectric effect is employed to achieve active modulation of the channel strain. Instead of permanent strain, we can now turn on the strain only in the on-state, leading to an advantageous on/off ratio, as visualized in Fig. 1. We earlier reported on experimental realizations of prototype devices following this principle [22].

In this work we further analyze the potential of the  $\pi$ -FET by technological and performance considerations. This article

FIGURE 1. Illustration of the  $I_D$ - $V_{GS}$  characteristics of a FET on semi-logarithmic scale. The characteristics are shown for a device with no strain (i.e., relaxed condition), constant strain, and strain formed by the converse piezoelectric effect (i.e., the  $\pi$ -FET). The subthreshold swing (SS) is also indicated.

describes the envisaged  $\pi$ -FET configurations, presents analytical relations of the SS, and estimates the power consumption based on analytical relations and roadmap projections [1].

This work is outlined as follows. In Section II we detail the principle of operation and derive the equations for the SS. In Section III we explain several device configurations. In Section IV we address the power consumption of the  $\pi$ -FET. Finally, in Section V the conclusions of this work are drawn.

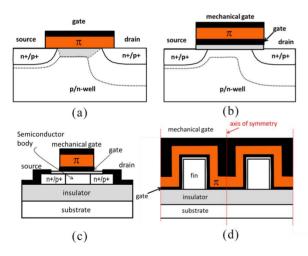

FIGURE 2. Schematic cross section of several envisaged  $\pi$ -FET configurations. (a) Bulk  $\pi$ -FET in which the  $\pi$ -layer has been directly placed on the silicon (the gray region indicates the depletion region), and devices in which there is only a mechanical contact between the  $\pi$ -layer and the channel such as (b) bulk  $\pi$ -FET and ultrathin body (UTB) devices in (c) planar/double-gate  $\pi$ -FET configuration, and (d)  $\pi$ -FinFET configuration (perpendicular to the current flow direction). For the  $\pi$ -FinFET, the vertical dotted line indicates the axis of symmetry. The dimensions are not to scale. Note for maximum strain effect the mechanical gate should be preferably made out of a stiff metal and fixed e.g., in the third dimension.

### II. BASIC PRINCIPLE

Before treating the possible device configurations we first discuss the basic principle and for the first time derive relations for the SS applicable to most types of  $\pi$ -FETs for improving the basic understanding. For a classical Si transistor, when there is good electrostatic gate control over I<sub>D</sub>, SS equals 60 mV/dec at room temperature as illustrated in Fig. 1 (no strain). In CMOS technology so-called strain, i.e., mechanical deformation, is employed in Si to increase the mobility hence the performance. This type of strain is typically constant depending on the surrounding materials and leads to a relatively high  $I_{\text{off}}$  and  $I_{\text{on}}$  provided all other process parameters are kept the same [5], [23], as illustrated in Fig. 1 (strained FET). Recently, we have proposed a new device called the PiezoFET ( $\pi$ -FET) [20], [21] in which a piezoelectric  $(\pi -)$  layer is incorporated in the device, see e.g., Fig. 2. The basic idea is that the strain in the semiconductor body can be tuned by the converse piezoelectric effect [24]. As a result, during device operation the body is relaxed in the off-state, resulting in a low  $I_{\text{off}}$ , and it is strained in the on-state. As mentioned before the strain has an effect on the mobility, however, also on the band alignment. In particular the change in band alignment reduces the SS as predicted by [21], schematically illustrated in Fig. 1. However, [21] presented numerical calculations with a focus on ultrathin body (UTB) configurations. To grasp the basic principle it is important to derive closed form relations for the SS of the  $\pi$ -FET in bulk and UTB configurations.

For determining the SS we need to study the electrostatics of a FET starting from:

$$V_{\rm GS} = V_{\rm ins} + V_{\rm s},\tag{2}$$

with  $V_{\rm ins}$  and  $V_{\rm s}$  being the voltage drop across the gate insulator and semiconductor, respectively.

Neglecting the mobile charge and nonidealities such as fixed charge in the gate dielectric, the following holds in subthreshold [10], [25]:

$$V_{\rm GS} = -\frac{Q_{\rm dep} + Q_{\rm it}}{C_{\rm ins}} + \psi_{\rm s} + \varphi_{\rm m} - \varphi_{\rm s}, \tag{3}$$

where  $Q_{\rm dep}$  is the depletion charge per unit area,  $Q_{\rm it}$  is the interface trap charge per unit area,  $C_{\rm ins}$  is the gate insulator capacitance per unit area,  $\psi_{\rm s}$  is the surface potential and  $\varphi_{\rm m}$ ,  $\varphi_{\rm s}$  are the workfunctions of the metal gate and semiconductor, respectively.

In particular  $\varphi_s$  is important for the  $\pi$ -FET, since it depends on the semiconductor electron affinity  $\chi_s$  and the bandgap  $E_g$ . Both these parameters are affected by the strain, and therefore by the converse piezoelectric effect [21], see also Section III.

For an n-type bulk MOSFET holds that

$$\varphi_{\rm s} = \chi_{\rm s} + \frac{E_{\rm g}}{q} + \frac{kT}{q} \ln \left( \frac{N_{\rm V}}{N_{\rm A}} \right),$$

(4)

and for a p-type bulk MOSFET

$$\varphi_{\rm s} = \chi_{\rm s} + \frac{kT}{q} \ln \left( \frac{N_{\rm C}}{N_{\rm D}} \right). \tag{5}$$

ELECTRON DEVICES SOCIETY

Finally for an ultrathin body (UTB) device, e.g., double-gate FET or FinFET, holds

$$\varphi_{\rm s} = \chi_{\rm s} + \frac{E_{\rm g}}{2q} + \frac{kT}{2q} \cdot \ln\left(\frac{N_{\rm C}}{N_{\rm V}}\right),\tag{6}$$

for both n- and p-type FETs.  $N_{A,D}$  is the acceptor and donor concentration,  $N_{C,V}$  is the effective density-of-states in the conduction and valence band, k is Boltzmann's constant, and T is the temperature. Further,

$$Q_{\rm dep} \approx \mp \sqrt{\pm 2 \cdot q \cdot \varepsilon_{\rm s} N_{\rm A,D} \psi_{\rm s}},$$

(7)

with  $\varepsilon_s$  the semiconductor permittivity. The upper (lower) sign corresponds to an n-type (p-type) FET. The depletion charge in long channel UTB devices can generally be neglected.

Since the potential barrier hence band alignment exponentially determines the subthreshold current (see also Eq. (11)), while transport parameters such as mobility  $\mu_{n,p}$  and  $N_{C,V}$  will have a less pronounced effect, in this work for simplicity we consider  $\mu_{n,p}$  and  $N_{C,V}$  to be independent of the strain hence the bias over the  $\pi$ -layer.

From Eqs. (3)–(6) it can then be derived for the n-type bulk MOSFET that

$$\frac{dV_{\text{GS}}}{d\psi_{\text{s}}} = \frac{C_{\text{ins}} + C_{\text{dep}} + C_{\text{it}}}{C_{\text{ins}} \cdot \left(1 + \frac{d\chi_{\text{s}}}{dV_{\text{GS}}} + \frac{1}{q} \cdot \frac{dE_{\text{g}}}{dV_{\text{GS}}}\right)},\tag{8}$$

and for the p-type bulk MOSFET

$$\frac{dV_{\text{GS}}}{d\psi_{\text{s}}} = \frac{C_{\text{ins}} + C_{\text{dep}} + C_{\text{it}}}{C_{\text{ins}} \cdot \left(1 + \frac{d\chi_{\text{s}}}{dV_{\text{GS}}}\right)},\tag{9}$$

while for the UTB FET

$$\frac{dV_{\text{GS}}}{d\psi_{\text{s}}} = \frac{C_{\text{ins}} + C_{\text{it}}}{C_{\text{ins}} \cdot \left(1 + \frac{d\chi_{\text{s}}}{dV_{\text{GS}}} + \frac{1}{2q} \cdot \frac{dE_{\text{g}}}{dV_{\text{GS}}}\right)}.$$

(10)

Here,  $C_{\rm dep}$  and  $C_{\rm it}$  are the depletion respectively interface trap capacitance per unit area ( $C_{\rm dep} = -\frac{dQ_{\rm dep}}{d\psi_{\rm s}}$ , see Eq. (7)). The terms depending on  $\chi_{\rm s}$ , and  $E_{\rm g}$  in the denominators

The terms depending on  $\chi_s$ , and  $E_g$  in the denominators of Eqs. (8)–(10) form the tunable strain parameters caused by the converse  $\pi$ -effect. These parameters strongly depend on the device configuration as is discussed in Section III.

Generally the following relation holds for the subthreshold current:

$$I_{\rm D} = \pm I_0 \cdot \exp\left(\pm \frac{\psi_{\rm s}}{u_T}\right) \cdot \left(1 - \exp\left(\mp \frac{V_{\rm DS}}{u_T}\right)\right), \quad (11)$$

with  $u_T = kT/q$  the thermal voltage. The upper (lower) sign holds for n-type (p-type) FETs.

The prefactor  $I_0$  depends on the type of FET. So holds for the long channel bulk FET [10]:

$$I_0 = \mu_{\rm n,p} \frac{n_{\rm i}^2}{N_{\rm A,D}} u_T^2 \cdot C_{\rm dep} \frac{W}{L},\tag{12}$$

with  $\mu_{n,p}$ , W, L is the charge carrier mobility, gate width, and channel length, respectively.

For long channel UTB devices holds:

$$I_0 = q\mu_{n,p}n_iu_T \cdot \frac{A_{\text{body}}}{L} \tag{13}$$

with  $A_{\text{body}} = W \cdot t_{\text{s}}$  for the double-gate FET [26],  $A_{\text{body}} = W_{\text{FIN}} \cdot H_{\text{FIN}} \cdot N_{\text{FIN}}$  for the FinFET, and  $A_{\text{body}} = \pi \cdot R^2 \cdot N_{\text{FIN}}$  for the gate-all-around (GAA) FET [27].  $N_{\text{FIN}}$ ,  $W_{\text{FIN}}$ ,  $H_{\text{FIN}}$ ,  $t_{\text{s}}$ , R are the amount of wires or fins, fin width, fin height, semiconductor thickness, and nanowire radius, respectively.

So far there have been no reports in case of an aggressively scaled UTB  $\pi$ -FET below the ballistic limit, i.e., for a channel length that is near or less than the mean free path  $\lambda$ . For deriving a closed form relation for the subthreshold current below the ballistic limit the so-called flux method [29]–[31] or scattering matrix approach (SMA) [28], [32] can be used. For the nanoscale FET the electrostatics are not fundamentally different [33]. Neglecting short-channel effects and considering three scattering matrices through the source, channel and drain region it can be derived that basically Eq. (11) holds with

$$I_0 = q \cdot (v_R B_O) \cdot n_i \cdot A_{\text{body}}, \tag{14}$$

where  $v_R$  is the Richardson velocity and

$$B_{Q} = \frac{T_{0} \cdot (1 - r)^{2}}{1 - 2(1 - T_{0})r + (1 - 2T_{0})} = \frac{1 - r}{1 + r}.$$

(15)

Here the transmission coefficient  $T_0 = \lambda/(\lambda + L)$  is assumed to be unity in the ballistic regime  $(L \to 0)$  and the source/drain backscattering coefficients to be the same  $r_S = r_D = r$ . An important difference between Eq. (13) and Eqs. (14), (15) is that for the former in principle the integral of the potential barrier is important, while for the latter the peak potential barrier matters most. For a long channel device  $B_Q \approx \lambda/L$  and Eq. (13) is re-obtained. Note that for narrow UTB devices the channel quantum well in the subthreshold condition results in a constant offset of the band edges; this has no effect on the SS and therefore is not taken into account.

In Eqs. (4)–(6) and Eqs. (12)–(14) both  $I_0$  and  $\psi_s$  depend on  $V_{\rm GS}$ . The former through  $n_{\rm i}$ , hence  $E_{\rm g}$ , the latter because of  $\chi_{\rm s}$ ,  $E_{\rm g}$  and the electrostatics.

Hence from Eqs. (11)–(14) we obtain

$$\frac{d\ln(I_{\rm D})}{dV_{\rm GS}} = \mp \frac{1}{a \cdot kT} \cdot \frac{dE_{\rm g}}{dV_{\rm GS}} + \frac{1}{u_T} \cdot \frac{d\psi_{\rm s}}{dV_{\rm GS}}, \quad (16)$$

with a = 1, 2 for the bulk FET and UTB FET respectively. Again the upper (lower) sign holds for n-type (p-type) FETs.

Substituting Eqs. (8)–(10) in Eqs. (1) and (16) and after some manipulation we obtain for the n-type bulk FET:

$$m = \frac{C_{\text{ins}} + C_{\text{dep}} + C_{\text{it}}}{C_{\text{ins}} \cdot \left(1 + \frac{d\chi_s}{dV_{\text{GS}}}\right) - \frac{(C_{\text{dep}} + C_{\text{it}})}{q} \cdot \frac{dE_g}{dV_{\text{GS}}}},$$

(17)

and for the p-type bulk FET:

$$m = \frac{C_{\text{ins}} + C_{\text{dep}} + C_{\text{it}}}{C_{\text{ins}} \cdot \left(1 + \frac{d\chi_{\text{s}}}{dV_{\text{GS}}}\right) + \frac{\left(C_{\text{ins}} + C_{\text{dep}} + C_{\text{it}}\right)}{q} \cdot \frac{dE_{\text{g}}}{dV_{\text{GS}}}}.$$

(18)

For the n-type UTB FET we obtain:

$$m = \frac{C_{\text{ins}} + C_{\text{it}}}{C_{\text{ins}} \cdot \left(1 + \frac{d\chi_{\text{s}}}{dV_{\text{GS}}}\right) - \frac{C_{\text{it}}}{2q} \cdot \frac{dE_{\text{g}}}{dV_{\text{GS}}}},$$

(19)

and finally for the p-type UTB FET we arrive at:

$$m = \frac{C_{\text{ins}} + C_{\text{it}}}{C_{\text{ins}} \cdot \left(1 + \frac{d\chi_s}{dV_{\text{GS}}}\right) + \frac{2C_{\text{ins}} + C_{\text{it}}}{2q} \cdot \frac{dE_g}{dV_{\text{GS}}}}.$$

(20)

In case of a negligible amount of strain we obtain the traditional text book equations [10], [25]: all terms in the denominators are zero except for  $C_{ins}$ .

For the  $\pi$ -FET, on the other hand, the parameters  $\chi_s$  and  $E_g$  depend on the strain hence applied bias  $V_{\rm GS}$  across the  $\pi$ -layer.  $\chi_s$  needs to increase, hence the minimum conduction band  $E_{\rm C}$  needs to drop, with increasing strain values for the n-type  $\pi$ -FET while for the p-type  $\pi$ -FET the maximum valence band  $E_{\rm V}$  needs to increase as confirmed by numerical calculations [21]. Therefore the following conditions for the  $\pi$ -FET should hold:

$$\frac{d\chi_{\text{S}}}{dV_{\text{GS}}} = -\frac{1}{q} \frac{dE_{\text{C}}}{dV_{\text{GS}}} > 0 \qquad (\text{n-type})$$

$$\frac{dE_{\text{V}}}{dV_{\text{GS}}} = q \frac{d\chi_{\text{S}}}{dV_{\text{GS}}} - \frac{dE_{\text{g}}}{dV_{\text{GS}}} < 0 \text{ (p-type)}$$

(21)

From Eqs. (1), (17), and (19) and the given conditions it can be concluded that the SS drops in the n-type  $\pi$ -FET compared to the same device without the  $\pi$ -layer. For the p-type FET this is more difficult to see. By checking the denominators of Eqs. (18) and (20) more carefully the terms  $C_{\rm ins} \cdot (1 + d\chi_{\rm S}/dV_{\rm GS})$  and  $(C_{\rm ins}/2q) \cdot dE_{\rm g}/dV_{\rm GS}$  add up to  $(C_{\rm ins}/q) \, (1 - dE_{\rm V}/dV_{\rm GS})$ . Hence, we can also conclude that for p-type  $\pi$ -FET SS drops. However it will be less pronounced compared to an n-type  $\pi$ -FET [21] because  $|(1/q) \, dE_{\rm V}/dV_{\rm GS}| < |d\chi_{\rm S}/dV_{\rm GS}|$ , as addressed in Section III.

Further, it indeed appears that a subthermal SS value ( $< \ln(10) \cdot u_T \approx 60 \text{ mV/dec}$ ) can be obtained in UTB devices provided that  $C_{it}$  is sufficiently low. However for the bulk FETs the SS strongly depends on the  $C_{\text{dep}}$  (and of course  $C_{it}$ ), though for the p-type bulk FET this is more important because of the additional positive right term in the denominator of Eq. (18). We will use Eqs. (17)–(20) for the discussion in the next section.

### III. DEVICE CONFIGURATIONS

To achieve subthermal switching performance as described in the previous paragraph, the transistor channel strain must be modulated by a control voltage. In recent work we have proposed to implement this by the integration of a piezoelectric material such as PZT or AlN [21], [22]. Fig. 2 shows the envisaged configurations of field effect transistors with a piezoelectric strain modulation layer.

The most straightforward and compact arrangement is obtained by replacing the gate dielectric by a piezoelectric insulator and hence by placing it directly on the silicon, as depicted in Fig. 2(a). This arrangement benefits from the fact that piezoelectric materials exhibit a relatively high dielectric constant, but it is expected that a subthermal *SS* is not reached for this case. The reason for this is that the dielectric should be surrounded by charge, preferably a lot. In case of a long channel FET in subthreshold condition this

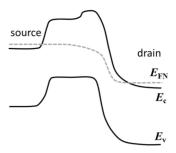

FIGURE 3. Schematic band diagram of the  $\pi$ -FET (Fig. 1) in the current flow direction just underneath the gate-dielectric. A potential barrier is formed at the drain side because of the high gate and drain potential. It is expected that this reduces the DIBL effect.

basically should be the depletion charge (or  $C_{\rm dep}$ ) in the grey area: the higher the amount of charge the higher the field, hence  $\pi$ -effect. However, when we check Eqs. (17)–(18) we see that  $C_{\rm dep}$  counteracts with the  $\pi$ -effect. Therefore the SS will be reduced by the  $\pi$ -effect but won't reach a subthermal value.

Related to this, simply replacing the gate dielectric by a piezoelectric insulator in a long channel UTB FET configuration will change the strain only slowly in the subthreshold regime as not all of the voltage drops over the dielectric ( $C_{\rm dep}$  can be neglected). Hence the strain will indeed be modulated in this arrangement, but only strongly in accumulation and inversion. Further, the carrier mobility may deteriorate in the presence of a polar material such as a piezoelectric layer.

There is one more topic to consider and that is the shortchannel effect (SCE). When we reduce the device dimensions of course the high amount of charge present in the source and drain regions will become dominant that increases the  $\pi$ -effect. As a result, there might be a reduced SS but again no subthermal values, both for bulk and UTB FETs. Also, depending on the shape of the source/drain doping profiles band-to-band tunneling will become more important because of the strain-induced  $E_g$  narrowing. Related to this, when using short channel  $\pi$ -FETs the drain-induced barrier lowering (DIBL) effect will be less compared to the classical counterpart. Since the gate-drain voltage at maximum current is near zero the field through the  $\pi$ -layer at the drain side will be low, and as a result the band alignment in the semiconductor is not affected. We basically obtain a change in the band alignment along the current flow direction, where a potential barrier is formed at the drain side, see Fig. 3. This makes the subthreshold current less sensitive to the drain bias. Of course this should be verified experimentally.

From the technology point of view there is another issue. A  $\pi$ -material with a high piezoelectric response such as lead zirconate titanate (PZT) [34], [35] and Si (or perhaps any other semiconductor) technology are mutually not compatible. To combine these materials, and to avoid ferroelectric performance degradation and atom interdiffusion through interfaces, a so-called buffer or seed layer is required [36]–[38] to avoid direct contacting on a semiconductor.

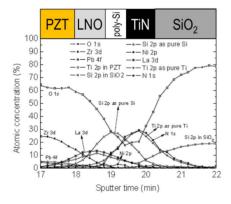

FIGURE 4. Schematic cross section of a metal-ferroelectric-metal (MFM) capacitor on top of a semiconductor substrate. In our experiments [39], we used for the top electrode (source) Pt/Ti, for the bottom electrode (gate) an LNO/poly-Si/TiN stack, and for the gate dielectric SiO<sub>2</sub> was used. For the discussion in the layer thicknesses are indicated. The dimensions are not to scale.

Earlier we did some experiments on metal-ferroelectric-metal (MFM) capacitors on top of a gated Si channel, see Fig. 4. For these capacitors a lanthanum nickelate, LaNiO<sub>3</sub> (LNO), layer was used as a buffer layer for the PZT layer on top of a traditional poly-Si/TiN/SiO<sub>2</sub> gate stack [39]. X-ray photoelectron spectroscopy (XPS) was used here to obtain the compositional depth profile of the fabricated multi-film stack. XPS analysis is generally used to get information on the material distribution in different layers and on interfaces. It can detect diffusion of impurity atoms (e.g., Pb) into the silicon channel below the PZT/LNO/poly-Si/TiN/SiO<sub>2</sub> stack. This is important to know since the impurity diffusion can degrade the performance of the underlying transistor.

Fig. 5 shows the XPS depth profile in such a capacitor. Starting from the surface the PZT layer is recognized. Below that layer the LNO buffer, poly-Si and TiN layers can be observed. Further down is the  $SiO_2$  gate dielectric. No diffusion of Pb in the Si layer is observed within the resolution limit of XPS ( $\sim 0.5$  at. %). This gives an indication that, when deposited on devices, there will be no degradation on the transistor properties as confirmed in our Si  $\pi$ -FinFET data [22].

FIGURE 5. XPS depth profile of the MFM capacitor from top to SiO<sub>2</sub> layer. In this experiment, LNO is used as buffer layer, the poly-Si and TiN layers are used as a gate, and the SiO<sub>2</sub> layer is used as a gate dielectric. The layer stack is schematically drawn on top of the graph to guide the eye.

Given these considerations we chose to study the configurations in Fig. 2(b)–(d) in more detail. Here, the piezoelectric

film is positioned *outside* the gate stack. The gate metal both shields the horizontal (source-drain) field and may act as a diffusion barrier. Depending on the  $\pi$ -material additional buffer layers may be required. So basically there is no electrical contact between the  $\pi$ -layer and semiconductor body, rather an indirect mechanical contact. Of course, tunnel FETs [13], [20] or Junction-less transistors [40] could also be formed in each of these configurations.

One advantage is that  $Q_{\rm dep}$  in all devices is no longer important for the  $\pi$ -effect because the full  $V_{\rm GS}$  can be applied over the  $\pi$ -layer. In case of long channel devices we can omit all  $C_{\rm dep}$  terms in Eqs. (17) and (18). This means that irrespective the use of a bulk  $\pi$ -FET of any UTB  $\pi$ -FET a subthermal SS can be obtained. Note that in these configurations  $C_{\rm ins}$  in Eqs. (17)–(20) no longer depends on the  $\pi$ -layer properties.

So far we have not discussed the mechanics and the mechanical boundaries. For planar devices, such as those depicted in Fig. 2(a)-(c), when we apply a voltage over the  $\pi$ -layer depending on the polarity of the voltage and  $\pi$ -material the  $\pi$ -layer thickness will deform. In conventional planar FET designs the top (or gate) metal is more or less free, i.e., mechanically floating. This means when we apply a bias over the  $\pi$ -layer some, perhaps most, of the electromechanical energy is not used to strain the semiconductor body and hence is lost. It is therefore advisory to mechanically fix the top metal in the third dimension using e.g., anchors attached to the either a substrate of (preferably) a stiff dielectric. This problem is more or less solved in the symmetric  $\pi$ -FinFET configuration as depicted in Fig. 2(d). In this case we have a symmetric mechanical boundary condition. However, in this configuration we need to have a good step coverage of the  $\pi$ -layer around the device, which is a problem since for this uniform deposition techniques such as atomic-layer deposition may be required [22] which is not straightforward in particular for ternary or quaternary compounds. For this AlN can be used as an alternative piezoelectric material, which can be deposited by ALD [41], [42]. However, as mentioned before AlN has a ten times lower piezoelectric response compared to PZT. In addition, the issue of the mechanical boundary condition can also be elegantly solved by utilizing a GAA device geometry encapsulated in stiff material.

There is an indirect mechanical contact between the  $\pi$ -layer and semiconductor body in the configurations of Fig. 2(b)–(d), which requires more effort to reduce SS effectively. When the mechanical gate is connected to the source it can be derived for the strain in the (100) oriented semiconductor body [21]:

$$s_{\rm S} = -\frac{\frac{e_{\pi} V_{\rm GS}}{c_{\pi} c_{\rm S}}}{\left(\frac{t_{\rm S}}{c_{\rm S}} + \frac{t_{\rm ins}}{c_{\rm ins}} + \frac{t_{\rm g}}{c_{\rm g}} + \frac{t_{\pi}}{c_{\pi}}\right)},\tag{22}$$

where  $t_{\pi,\text{ins},g}$  is the thickness of the  $\pi$ -, insulator and gate metal layer (see also Fig. 4),  $c_{\pi,\text{ins},s,g}$  is the stiffness of the  $\pi$ -, insulator, semiconductor and gate metal layer,

and  $e_{\pi}$  is the piezoelectric (charge) constant. Note that the physical parameters  $e_{\pi}$  and  $c_{\pi, ins, s, g}$  are tensors but in this one-dimensional relation have been assumed to be scalars for simplicity sake. Consequently, shear strain components have been ignored as well. In real life these parameters, in particular  $c_{\pi}$  and  $e_{\pi}$ , depend on the crystal (and device) orientation and field direction. From Eq. (22) we can derive the  $\chi_s$  and  $E_g$  strain dependence via the deformation potentials in the conduction band and valence band. Basically it can be summarized that:

$$\chi_{\rm s}(s_{\rm s}) = \chi_{\rm s0} - \Xi_{\rm C,eff} \cdot s_{\rm s}, \tag{23}$$

$$E_{g}(s_{s}) = E_{g0} + \left(\Xi_{C,eff} - \Xi_{V,eff}\right) \cdot s_{s},\tag{24}$$

with  $E_{g0}$  and  $\chi_{s0}$  are the bandgap and workfunction of the relaxed semiconductor, and  $\Xi_{C,eff}$ ,  $\Xi_{V,eff}$  are the "effective" deformation potential in the conduction band and valence band of the semiconductor, respectively. These "effective" parameters are introduced to avoid numerous details [21], [43]–[47] which are not important for this discussion. More importantly, in case of III-V materials a tensile (compressive)  $s_s$  value is required for the n-type (p-type) FET because  $\Xi_{C,eff}$  and  $\Xi_{V,eff}$  are both negative in sign. For germanium (Ge), Si on the other hand a compressive  $s_s$  value is required irrespective of the type of FET ( $\Xi_{C,eff}$ ,  $\Xi_{V,eff}$  is positive respectively negative in sign) [21]. Also  $|\Xi_{C,eff}| > |\Xi_{V,eff}|$  for all materials and consequently the converse  $\pi$ -effect is in principle more effective for n-type FETs. From Eqs. (22)-(24) we obtain relations for  $d\chi_s/dV_{GS} = -\Xi_{C,eff} \cdot s_s/V_{GS}$  and  $dE_g/dV_{GS}$  $(= (\Xi_{C,eff} - \Xi_{V,eff}) \cdot s_s/V_{GS})$  needed for the SS, see Eq. (21).

From Eqs. (22)–(24) we can also conclude the following. First, for reducing mechanical losses ultrathin and relatively stiff interfacial layers in between the  $\pi$ - and semiconductor body are required (e.g., hafnium-oxide (HfO<sub>2</sub>) instead of SiO<sub>2</sub>). In particular the stiffness is important for the gate metal since the workfunction of the metal could also depend on the amount of strain. This effect has been reported before for titanium-nitride (TiN) [48]–[50]. Because of its high stiffness relatively high stress values are required to change the workfunction. Second, the semiconductor body should preferably have a low stiffness and a high deformation potential (e.g., germanium, III-Vs [44], [47]), and third, the  $\pi$ -material should preferably have a high piezoelectric response, but also a high breakdown field  $E_{cr}$  [21].

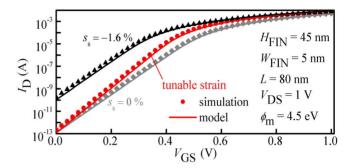

Fig. 6 shows simulation data for three types of n-type Ge FinFETs [21]: a device without strain (i.e., relaxed), one with a fixed strain value of 1.6%, and another device with tunable strain (the  $\pi$ -FinFET) with PZT as a piezoelectric layer. In the latter the maximum strain level is 1.6% at  $V_{\rm DS} = 1$  V. The simulations were performed in mixed-mode: Comsol Multiphysics was used for the mechanical domain and used as input for the TCAD Sentaurus (Synopsys) simulation tool used for the electrical domain. For comparison the analytical model obtained from [26] has been plotted in the same graph in which the conduction band has been adjusted depending on the amount of strain according to

Eq. (23) where  $\Xi_{C,eff} \approx 12.4$  eV for Ge [43]. The results show that for an increased fixed strain value the subthreshold current increases exponentially while the SS does not change. However, for the  $\pi$ -FinFET the SS has been reduced to 50 mV/dec (T=300 K), indicating that subthermal SS values can be obtained.

FIGURE 6. Simulated and modeled  $I_{\rm D}$ - $V_{\rm GS}$  characteristics of an n-type Ge FinFET (Fig. 2(d)) with tunable strain ( $\pi$ -FinFET) and with constant strain [21] ( $T=300~{\rm K}$ ). All devices have a 1.5-nm thick hafnium-dioxide (HfO<sub>2</sub>) layer for the gate dielectric and a 3-nm thick titanium-nitride (TiN) layer for the gate metal. The  $\pi$ -FinFET consists of a 10-nm thick PZT layer.

In summary, depending on the boundary conditions in the processing, mechanics and device physics several device configurations have been proposed and discussed for the  $\pi$ -FET concept. These configurations could potentially reach subthermal SS values.

### IV. POWER CONSUMPTION

The reason to investigate steep subthreshold slope devices is the promise of a lower power consumption. In this section we estimate the effect of strain modulation on the power consumption of a transistor that is used in digital logic circuitry. The total power consumption can be divided into two parts. The first is the dynamic power  $P_{\rm dyn}$ , which in digital logic is the energy required to switch the transistor state [51] and multiplied by the number of switches per second. The second is the static power  $P_{\rm stat}$ , given by the leakage current multiplied by the supply voltage.

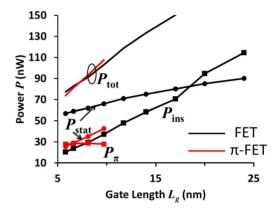

The strain modulation effect can be employed in different ways. For instance either the supply voltage  $V_{\rm DD}$  can be kept the same and consequently the leakage current  $I_{\rm off}$  is reduced, resulting in a lower  $P_{\rm stat}$ , or the  $I_{\rm off}$  can be kept constant and the  $V_{\rm DD}$  is reduced, resulting mostly in a lower  $P_{\rm dyn}$ . In the  $\pi$ -FinFET a piezoelectric capacitance is added parallel to the gate capacitance. For each cycle both must be charged and discharged, and as a result this adds up to  $P_{\rm dyn}$ . Hence it is unlikely that the  $\pi$ -FinFET is able to reduce the  $P_{\rm dyn}$ . However, it can reduce the  $P_{\rm stat}$  at the cost of an increased  $P_{\rm dyn}$ . We follow [51], and note that the  $P_{\rm dyn}$  is given by the sum of the charge required to charge both the oxide  $P_{\rm ins}$  and the piezoelectric layer  $P_{\pi}$  and find

$$P_{\text{ins}} = W \cdot L_{\text{g}} \cdot \alpha \cdot f_{\text{clk}} f_{\text{o}} \frac{V_{\text{DD}}^2}{2} C_{\text{ins}}$$

(25)

$$P_{\pi} = W \cdot L_{g} \cdot \alpha \cdot f_{\text{clk}} f_{0} \frac{V_{\text{DD}}^{2}}{2} \left( \frac{\varepsilon_{\pi}}{t_{\pi}} + \frac{s_{\pi} \cdot e_{\pi}}{V_{\text{DD}}} \right)$$

(26)

$$P_{\text{stat}} = I_{\text{off}} \cdot V_{\text{DD}} \cdot \exp\left(\frac{\Xi_{\text{C,eff}} \cdot s_{\text{s}}}{u_T}\right)$$

(27)

where  $\alpha$  is the switching activity factor,  $f_{\rm clk}$  is the clock frequency,  $f_{\rm o}$  is the tapering factor (the number of switches each transistor has to drive), W is the gate width,  $L_{\rm g}$  is the gate length, and  $I_{\rm off}$  is the off-current of a device without strain (see e.g., Eqs. (11) and (13), with  $V_{\rm DS}=V_{\rm DD}$ ,  $V_{\rm GS}=0$ ). Note that the leakage through the piezoelectric layer can be ignored in this discussion since its current density is less than  $\sim 10^{-4}$  A/cm² which is much less than the value reported for the gate leakage [52], [53].

The band deformation due to the induced strain is given by  $\Xi_{C,eff} \cdot s_s$ , where  $\Xi_{C,eff}$  is the effective deformation potential. Further,  $t_{\pi}$ ,  $\varepsilon_{\pi}$ , and  $s_{\pi}$  is the thickness, permittivity, and strain in the  $\pi$ -layer, respectively.  $t_{\pi}$  is calculated by assuming that the maximum field  $E_{cr}$  is over the  $\pi$ -layer when  $V_{DS} = V_{DD}$ , i.e.,  $t_{\pi} = V_{DD}/E_{cr}$  [21]. The strain values  $s_s$ ,  $s_{\pi}$  can be calculated using Eq. (22).

Hence, the piezoelectric power scales with the sum of the permittivity and the strain in the piezoelectric layer. The equations can be used to estimate whether strain modulation can reduce the power consumption of a transistor. In the general case we can only answer that it strongly depends on all the material parameters, device dimensions, frequency of operation and usage of the devices. However, we can state that strain modulation can reduce the  $P_{\rm stat}$  at the cost of an increased  $P_{\rm dyn}$ , hence it can only be beneficial in circuits where  $P_{\rm stat}$  dominates the total power consumption.

An estimation for the device parameters in the future can be found in the ITRS roadmap [1]. We used the device parameters from the 2011 edition for the FEP4 Low Standby Power Devices Technical Requirements, other parameters used are summarized in Table 1. For the  $\pi$ -layer we considered PZT, for the semiconductor Ge, for the gate metal layer TiN, and gate insulator HfSiO. From this roadmap we estimated the expected  $P_{\text{stat}}$  and  $P_{\text{dyn}}$  for an n-type transistor, and these are shown in Fig. 7. The graph shows that  $P_{\text{stat}}$  exceeds  $P_{\text{dyn}}$  for technologies with gate lengths below 18 nm. Next, following Eqs. (26) and (27) we estimated the effect piezoelectric strain modulation can have on the power consumption. We tuned the piezoelectric layer thickness, and thus the strain modulation and corresponding power  $P_{ins}$ , to obtain a minimal total power. To illustrate the numbers at L = 5 nm, the tuned piezoelectric thickness is 48 nm, its dielectric constant is assumed to be 150, while the gate oxide thickness is 0.5 nm. We found that from  $\sim$  8 nm gate length onward the estimated  $P_{\text{stat}}$  is significantly higher than  $P_{\text{dyn}}$ . There the strain modulation can reduce the total power consumption of a transistor, even at the cost of the additional  $P_{\rm dyn}$  of the  $\pi$ -layer.

TABLE 1. Device parameters used for estimating the power consumption of the  $\pi$ -FET (see Fig. 7).  $E_{\rm Cr}$  is the breakdown field for PZT used to scale  $t_{\pi}$  (=  $V_{\rm DD}/E_{\rm Cr}$ ). Other parameters such as  $t_{\rm ins}$ ,  $V_{\rm DD}$ ,  $I_{\rm off}$ , and gate length have been taken from [1]. Note that for the permittivity of PZT the high field (near  $E_{\rm Cr}$ ) value has been used.

| α                   | 0.01 [54] | $c_{\rm ins}$        | 70 GPa                |

|---------------------|-----------|----------------------|-----------------------|

| $c_{\rm g}$         | 660 GPa   | $c_{\mathrm{s}}$     | 131 GPa               |

| $c_{\pi}$           | 117 GPa   | $arepsilon_{ m ins}$ | 13                    |

| $\varepsilon_{\pi}$ | 150       | $e_{\pi}$            | 23.3 C/m <sup>2</sup> |

| $E_{\rm cr}$        | 1 MV/cm   | $f_{0}$              | 3 [54]                |

| $t_{ m g}$          | 5 nm      | $t_{ m S}$           | 5 nm                  |

| T                   | 300 K     | $\Xi_{\text{C.eff}}$ | 12.4 eV               |

FIGURE 7. Estimated power of an n-type transistor calculated from the ITRS [1] prognoses for device parameters and performance (black line). An estimate for the strain modulation effect on the power consumption is shown in red. Please note that the strain modulation is used to decrease the static power consumption. Hence, Pins is the same for both transistors

### V. CONCLUSION

In this work we have discussed the effect of the envisaged device configurations for the  $\pi$ -FET based on simple estimations. It is expected that a  $\pi$ -layer in direct contact with the semiconductor body will not result in subthermal SS values. However for the proposed device configurations subthermal SS can be reached depending upon the mechanical boundary conditions, such as mechanical material properties, interfacial layer thicknesses and device design. Based on the ITRS roadmap the main benefit in the power consumption is estimated to occur from 8 nm gate length onwards. In case of standby operation the total power consumption is primarily determined by the static power consumption which will then make the  $\pi$ -FET concept an attractive candidate. However for our experimental work more research is needed to obtain subthermal SS values following the guidelines of this work in addition to well controlled interfaces.

# **ACKNOWLEDGMENT**

The authors would like to thank the Semiconductor Components Group and MESA+ Nanolaboratory staff members for their kind support. They also would like to thank SolMateS B.V., Enschede, The Netherlands, for the material supply.

# **REFERENCES**

- Semiconductor Industry Association (SIA), International Roadmap for Semiconductors, Int. SEMATECH, Austin, TX, USA, 2013. [Online]. Available: http://www.itrs.net

- [2] C. J. Först, C. R. Ashman, K. Schwarz, and P. E. Blöchl, "The interface between silicon and a high-κ oxide," *Nature*, vol. 427, pp. 53–56, Jan. 2004.

- [3] E. Cartier et al., "Fundamental aspects of HfO<sub>2</sub>-based high-k metal gate stack reliability and implications on t<sub>inv</sub> scaling," in Proc. IEEE Int. Electron Devices Meeting, Washington, DC, USA, 2011, pp. 18.4.1–18.4.4.

- [4] J. Welser, J. L. Hoyt, and J. F. Gibbons, "NMOS and PMOS transistors fabricated in strained silicon/relaxed silicon-germanium structures," in *Proc. IEEE Int. Electron Devices Meeting*, San Francisco, CA, USA, 1992, pp. 1000–1002.

- [5] K. Rim et al., "Strained Si NMOSFETs for high performance CMOS technology," in Proc. Symp. VLSI Technol. Dig. Tech. Papers, Kyoto, Japan, 2001, pp. 59–60.

- [6] S. W. Bedell, A. Khakifirooz, and D. K. Sadana, "Strain scaling for CMOS," MRS Bull., vol. 39, no. 2, pp. 131–137, 2014.

- [7] F. Balestra, S. Cristoloveanu, M. Benachir, J. Brini, and T. Elewa, "Double-gate silicon-on-insulator transistor with volume inversion: A new device with greatly enhanced performance," *IEEE Electron Device Lett.*, vol. 8, no. 9, pp. 410–412, Sep. 1987.

- [8] D. Hisamoto et al., "A folded-channel MOSFET for deep-sub-tenth micron era," in Proc. IEEE Int. Electron Devices Meeting, San Francisco, CA, USA, 1998, pp. 1032–1034.

- [9] B. Yu et al., "FinFET scaling to 10 nm gate length," in Proc. IEEE Int. Electron Devices Meeting, San Francisco, CA, USA, 2002, pp. 251–254.

- [10] S. M. Sze and K. K. Ng, Physics of Semiconductor Devices, 3rd ed. Hoboken, NJ, USA: Wiley, 2007.

- [11] K. Gopalakrishnan, P. B. Griffin, and J. D. Plummer, "I-MOS: A novel semiconductor device with a subthreshold slope lower than kT/q," in Proc. IEEE Int. Electron Devices Meeting, San Francisco, CA, USA, 2002, pp. 289–292.

- [12] S. Banerjee, W. Richardson, J. Coleman, and A. Chatterjee, "A new three-terminal tunnel device," *IEEE Electron Device Lett.*, vol. 8, no. 8, pp. 347–349, Aug. 1987.

- [13] A. C. Seabaugh and Q. Zhang, "Low-voltage tunnel transistors for beyond CMOS logic," *Proc. IEEE*, vol. 98, no. 12, pp. 2095–2110, Dec. 2010.

- [14] A. M. Ionescu and H. Riel, "Tunnel field-effect transistors as energy-efficient electronic switches," *Nature*, vol. 479, pp. 329–337, Nov. 2011.

- [15] S. Salahuddin and S. Datta, "Can the subthreshold swing in a classical FET be lowered below 60 mV/decade?" in *Proc. IEEE Int. Electron Devices Meeting*, San Francisco, CA, USA, 2008, pp. 1–4.

- [16] A. Rusu, G. A. Salvatore, D. Jimenez, and A. M. Ionescu, "Metal-ferroelectric-metal-oxidesemiconductor field effect transistor with sub-60mV/decade subthreshold swing and internal voltage amplification," in *Proc. IEEE Int. Electron Devices Meeting*, San Francisco, CA, USA, 2010, pp. 16.3.1–16.3.4.

- [17] R. K. Jana, G. L. Snider, and D. Jena, "On the possibility of sub-60 mV/decade subthreshold switching in piezoelectric gate barrier transistors," *Phys. Status Solidi C*, vol. 10, no. 11, pp. 1469–1472, 2013.

- [18] N. Abelé et al., "Suspended-gate MOSFET: Bringing new MEMS functionality into solid-state MOS transistor," in Proc. IEEE Int. Electron Devices Meeting, Washington, DC, USA, 2005, pp. 479–481.

- [19] A. M. Ionescu et al., "The hysteretic ferroelectric tunnel FET," IEEE Trans. Electron Devices, vol. 57, no. 12, pp. 3518–3524, Dec. 2010.

- [20] T. van Hemert and R. J. E. Hueting, "Active strain modulation in field effect devices," in *Proc. Eur. Solid-State Device Res.* Conf. (ESSDERC), Bordeaux, France, 2012, pp. 125–128.

- [21] T. van Hemert and R. J. E. Hueting, "Piezoelectric strain modulation in FETs," *IEEE Trans. Electron Devices*, vol. 60, no. 10, pp. 3265–3270, Oct. 2013.

- [22] B. Kaleli, R. J. E. Hueting, M. Nguyen, and R. A. M. Wolters, "Integration of a piezoelectric layer on Si FinFETs for tunable strained device applications," *IEEE Trans. Electron Devices*, vol. 61, no. 6, pp. 1929–1935, Jun. 2014.

- [23] T. van Hemert et al., "Strain and conduction-band offset in narrow n-type FinFETs," IEEE Trans. Electron Devices, vol. 60, no. 3, pp. 1005–1010, Mar. 2013.

- [24] B. A. Auld, Acoustic Fields and Waves in Solids. New York, NY, USA: Wiley, 1973.

- [25] D. K. Schroder, Semiconductor Material and Device Characterization, 3rd ed. Piscataway, NJ, USA: Wiley, 2006.

- [26] Y. Taur, X. Liang, W. Wang, and H. Lu, "A continuous, analytic drain-current model for DG MOSFETs," *IEEE Electron Device Lett.*, vol. 25, no. 2, pp. 107–109, Feb. 2004.

- [27] D. Jiménez et al., "A continuous, analytic I-V model for surrounding-gate MOSFETs," *IEEE Electron Device Lett.*, vol. 25, no. 8, pp. 571–573, Aug. 2004.

- [28] M. S. Lundstrom, Fundamentals of Carrier Transport, 2nd ed. Cambridge, U.K.: Cambridge Univ. Press, 2000.

- [29] J. P. McKelvey, R. L. Longini, and T. P. Brody, "Alternative approach to the solution of added carrier transport problems in semiconductors," *Phys. Rev.*, vol. 123, no. 1, pp. 51–57, 1961.

- [30] J. P. McKelvey and J. C. Balogh, "Flux methods for the analysis of transport problems in semiconductors in the presence of electric fields," *Phys. Rev.*, vol. 137, pp. 1555–1561, Mar. 1965.

- [31] E. F. Pulve and J. P. McKelvey, "Ambipolar carrier transport and surface recombination velocity in semiconductor surface layers," *Phys. Rev.*, vol. 158, no. 3, pp. 779–787, 1967.

- [32] M. A. Alam, M. A. Stettler, and M. S. Lundstrom, "Formulation of the Boltzmann equation in terms of scattering matrices," *Solid-State Electron.*, vol. 36, no. 2, pp. 263–271, 1993.

- [33] M. S. Lundstrom and D. A. Antoniadis, "Compact models and physics of nanoscale FETs," *IEEE Trans. Electron Devices*, vol. 61, no. 2, pp. 225–233, Feb. 2014.

- [34] A. K. Singh et al., "Origin of high piezoelectric response of PbZr<sub>x</sub>Ti<sub>1-x</sub>O<sub>3</sub> at the morphotropic phase boundary: Role of elastic instability," Appl. Phys. Lett., vol. 92, 2008, Art. ID 022910.

- [35] Y. Cao et al., "Piezoelectric response of single-crystal PbZr<sub>1-x</sub>Ti<sub>x</sub>O<sub>3</sub> near morphotropic phase boundary predicted by phase-field simulation," Appl. Phys. Lett., vol. 97, 2010, Art. ID 252904.

- [36] Q. Zou, H. E. Ruda, and B. G. Yacobi, "Improved dielectric properties of lead zirconate titanate thin films deposited on metal foils with LaNiO<sub>3</sub> buffer layers," *Appl. Phys. Lett.*, vol. 78, no. 9, pp. 1282–1284, 2001.

- [37] N. Sama et al., "On the influence of the top and bottom electrodes— A comparitive study between Pt and LNO electrodes for PZT thin films," J. Crystal Growth, vol. 310, no. 4, pp. 3299–3302, 2008.

- [38] J. Li et al., "The thickness effect of Bi<sub>3.25</sub>La<sub>0.75</sub>Ti<sub>3</sub>O<sub>12</sub> buffer layer in PbZr<sub>0.58</sub>Ti<sub>0.42</sub>O<sub>3</sub>/Bi<sub>3.25</sub>La<sub>0.75</sub>Ti<sub>3</sub>O<sub>12</sub> (PZT/BLT) multilayered ferroelectric thin films," *Thin Solid Films*, vol. 519, no. 18, pp. 6021–6025, 2011.

- [39] B. Kaleli, M. D. Nguyen, J. Schmitz, R. J. E. Hueting, and R. A. M. Wolters, "Analysis of thin-film PZT/LNO stacks on an encapsulated TiN electrode," *Microelectron. Eng.*, vol. 119, pp. 16–19, May 2014.

- [40] C.-W. Lee et al., "Junctionless multigate field-effect transistor," Appl. Phys. Lett., vol. 94, 2009, Art. ID 053511.

- [41] J. N. Kidder, Jr., H. K. Yun, J. W. Rogers, Jr., and T. P. Pearsall, "Chemical composition of AlN thin films deposited at 523-723 K using dimethylethylamine alane and ammonia," *Chem. Mater.*, vol. 10, no. 3, pp. 777–783, 1998.

- [42] C. Ozgit, I. Donmez, M. Alevli, and N. Biyikli, "Self-limiting low-temperature growth of crystalline AlN films by plasma-enhanced atomic layer deposition," *Thin Solid Films*, vol. 520, no. 7, pp. 2750–2755, 2012.

- [43] G. L. Bir and G. E. Pikus, Symmetry and Strain-Induced Effects in Semiconductors. New York, NY, USA: Wiley, 1974.

- [44] C. G. Van de Walle, "Band lineups and deformation potentials in the model-solid theory," *Phys. Rev. B*, vol. 39, no. 3, pp. 1871–1883, 1989.

- [45] M. V. Fischetti and S. E. Laux, "Band structure, deformation potentials, and carrier mobility in strained Si, Ge, and SiGe alloys," *J. Appl. Phys.*, vol. 80, no. 4, pp. 2234–2252, 1996.

- [46] E. Ungersboeck et al., "The effect of general strain on the band structure and electron mobility of silicon," *IEEE Trans. Electron Devices*, vol. 54, no. 9, pp. 2183–2190, Sep. 2007.

- [47] J. Kim and M. V. Fischetti, "Electronic band structure calculations for biaxially strained Si, Ge, and III-V semiconductors," *Appl. Phys. Lett.*, vol. 108, 2010, Art. ID 013710.

- [48] C. Y. Kang et al., "Effects of metal gate-induced strain on the performance of metal-oxide-semiconductor field effect transistors with titanium nitride gate electrode and hafnium oxide dielectric," Appl. Phys. Lett., vol. 91, no. 3, 2007, Art. ID 033511.

- [49] D. I. Bazhanov et al., "Impact of strain on the surface properties of transition metal carbide films: First-principles study," J. Appl. Phys., vol. 107, no. 8, 2010, Art. ID 083521.

- [50] X. Yang, M. Chu, A. Huang, and S. Thompson, "Effects of mechanical-bending and process-induced stresses on metal effective work function," *Solid-State Electron.*, vol. 79, pp. 142–146, Jan. 2013.

- [51] A. Chandrakasan and R. Brodersen, "Minimizing power consumption in digital CMOS circuits," in *Proc. IEEE*, vol. 83, no. 4, pp. 498–523, Apr. 1995.

- [52] T. Ghani et al., "Scaling challenges and device design requirements for high performance sub-50 nm gate length planar CMOS transistors," in *Proc. Symp. VLSI Technol. Dig. Tech. Papers*, Honolulu, HI, USA, 2000, pp. 174–175.

- [53] M. Dai et al., "A novel atomic layer oxidation technique for EOT scaling in gate-last high-κ/metal gate CMOS technology," in Proc. Int. Electron Device Meet. Tech. Dig., Washington, DC, USA, 2011, pp. 650–653.

- [54] C. Svensson and A. Alvandpour, "Low power and low voltage CMOS digital circuit techniques," in *Proc. Int. Symp. Low Power Electron. Design (ISLPED)*, Monterey, CA, USA, 1998, pp. 7–10.

**RAYMOND J. E. HUETING** (S'94–M'98–SM'06) received the M.Sc. (*cum laude*) and Ph.D. degrees in electrical engineering from the Delft University of Technology (NL). In 2005, he joined the Semiconductor Components Group, University of Twente in the field of semiconductor device physics and modeling.

**TOM VAN HEMERT** received the B.Sc., M.Sc., and Ph.D. degrees in electrical engineering from the University of Twente. He is currently with TMC Physics. His research interest is in device concepts which aim at reducing the power consumption of integrated circuits.

**BUKET KALELI** received the B.Sc. and M.Sc. degrees in physics from the Middle East Technical University, in 2007 and 2009, respectively, and the Ph.D. degree from the University of Twente, Enschede, The Netherlands.

ROB A. M. WOLTERS received the M.Sc. and Ph.D. degrees from the University of Twente, Enschede, The Netherlands, in 1974 and 1978, respectively. He was with Philips Research and NXP Research, Eindhoven, The Netherlands. Since 2004, he has been a Part-Time Professor with MESA+ Institute for Nanotechnology and the Chair of Semiconductor Components, University of Twente.

JURRIAAN SCHMITZ received the M.Sc. (Hons.) and Ph.D. degrees in experimental physics from the University of Amsterdam, in 1990 and 1994, specializing on radiation imaging detectors for the Large Hadron Collider. He was a European Organization for Nuclear Research (CERN) Summer Student in 1990. He joined Philips Research, Eindhoven, The Netherlands, in 1994, as Senior Scientist to work on CMOS device technology, characterization, and reliability. In 2002, he was a Professor of Semiconductor

Components, University of Twente, Enschede, The Netherlands. His research interests include CMOS post-processing, novel materials, silicon devices, and wafer-level electrical characterization of devices. He has (co)-authored over 200 scientific papers and holds 16 U.S. patents.