# HIGH-VOLTAGE CLASS-D POWER AMPLIFIERS: DESIGN AND OPTIMIZATION

Haifeng Ma

# HIGH-VOLTAGE CLASS-D POWER AMPLIFIERS: DESIGN AND OPTIMIZATION

Haifeng Ma

#### The Graduation Committee:

Chairman and secretary:

Prof. dr. P.M.G. Apers

University of Twente

Promotor:

Prof. dr. ir. B. Nauta University of Twente

Assistant promotor:

Dr. ir. R.A.R. van der Zee University of Twente

Referee:

Dr. ir. M. Berkhout NXP Nijmegen

Members:

Prof. dr. ir. A.H.M. van Roermund Eindhoven University of Technology

Prof. dr. ir. C.H. Slump University of Twente

Prof. dr. ir. M. Steyaert KU Leuven

Prof. ir. A.J.M. van Tuijl University of Twente

This research is supported by the Dutch Technology Foundation STW, which is part of the Netherlands Organisation for Scientific Research (NWO) and partly funded by the Ministry of Economic Affairs (project number 10602).

CTIT Ph.D. Thesis Series No. 15-358 Centre for Telematics and Information Technology P.O. Box 217, 7500 AE Enschede, The Netherlands.

Title: High-Voltage Class-D Power Amplifiers: Design and Optimization

ISSN: 1381-3617 (CTIT Ph.D. Thesis Series No. 15-358)

ISBN: : 978-90-365-3870-1 DOI: 10.3990/1.9789036538701

http://dx.doi.org/10.3990/1.9789036538701

# HIGH-VOLTAGE CLASS-D POWER AMPLIFIERS: DESIGN AND OPTIMIZATION

#### **DISSERTATION**

to obtain

the degree of doctor at the University of Twente,

on the authority of the rector magnificus,

prof.dr. H. Brinksma,

on account of the decision of the graduation committee,

to be publicly defended

on Friday 12 June 2015 at 16:45

by

Haifeng Ma born on 24 October 1985 in Jiangsu, China This dissertation has been approved by:

Promotor: Prof. dr. ir. B. Nauta

Assistant Promotor: Dr. ir. R.A.R. van der Zee

### **ABSTRACT**

Nowadays transducers are ubiquitous as interfaces between the increasingly digital world and the real physical world. The same holds for the power amplifiers driving them. This thesis focuses on the design and optimization of high-voltage class-D amplifiers, which are used for driving capacitive piezoelectric actuator loads in active vibration/noise control applications. The main objective is to further enhance class-D power efficiency compared to existing class-D designs.

To gain insight in class D power efficiency, a detailed analysis of high-voltage class-D dissipation sources is performed and a dissipation model including all the major dissipation sources is developed. The analysis shows that switching loss is a potential dominating dissipation source in high-voltage applications, while its contribution can be minimized by fast switching to eliminate V-I overlap losses. Moreover, it is shown that when varying the class-D switching frequency, a minimum total dissipation exists, with the optimal switching frequency depending on the output power. Furthermore, idle loss reduction by increasing the switching frequency and inserting a dead time to the power stage is backed by the analysis.

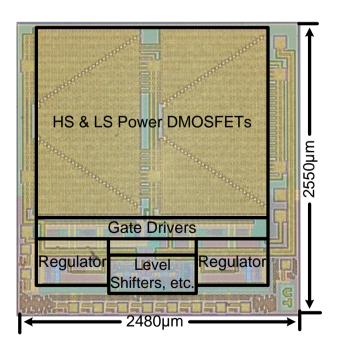

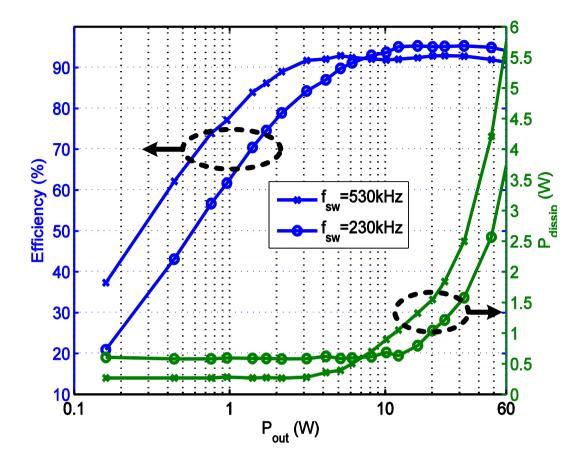

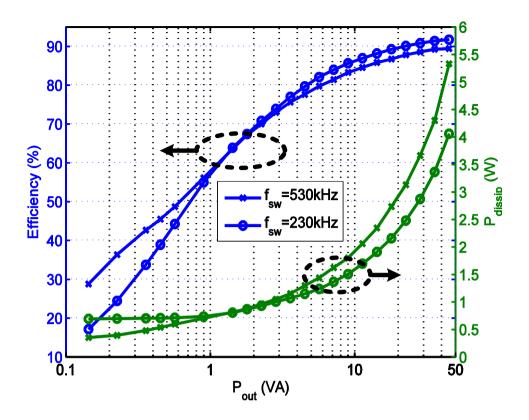

Following the analysis, a fast-switching power stage is designed to aim for switching loss minimization. This output stage design features immunity to the on-chip supply bounce, realized by internally regulated floating supplies, variable driving strength for the gate driver, and an efficient 2-step level shifter design. Fast switching transitions and low switching loss are achieved with 94% peak efficiency for the complete class-D power stage in the realized chip. In addition, gate driver sizing procedures for the class-D output stage are discussed, showing that the variable gate driving strength can greatly improve efficiency when on-chip supply bounce is the limiting factor.

Also based on the dissipation analysis, this thesis describes the design of an efficiency-improved high-voltage class-D power amplifier. The amplifier adaptively regulates its

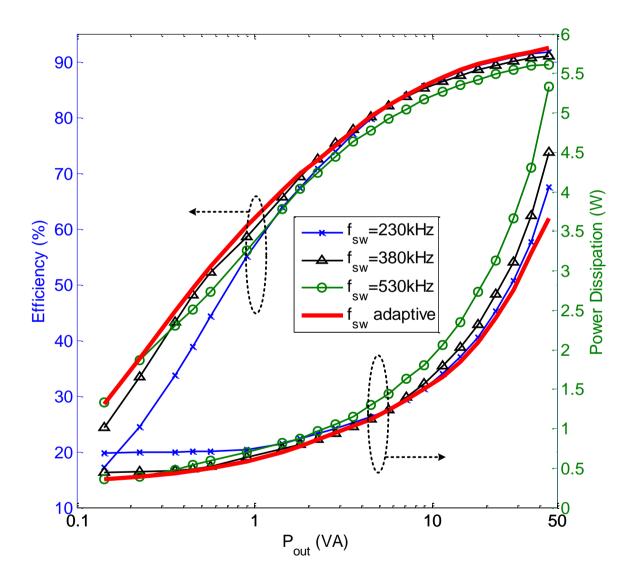

switching frequency for optimal power efficiency across the full output power range. This is based on detecting the switching output node voltage level at the turn-on transition of the power switches. For the final chip prototype, the amplifier achieves 93% efficiency at 45W output power, >80% power efficiency down to 4.5W output power and >49% efficiency down to 0.45W output power.

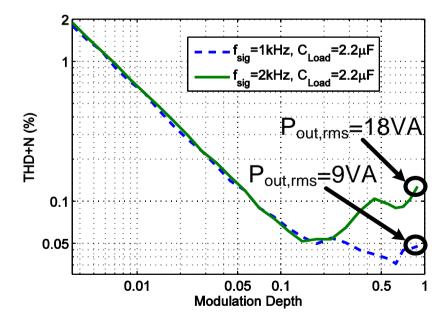

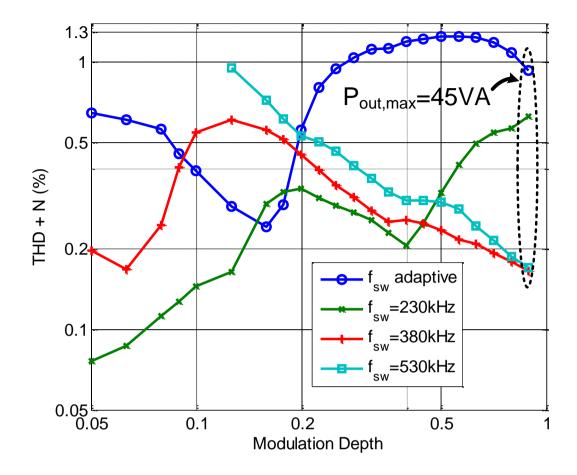

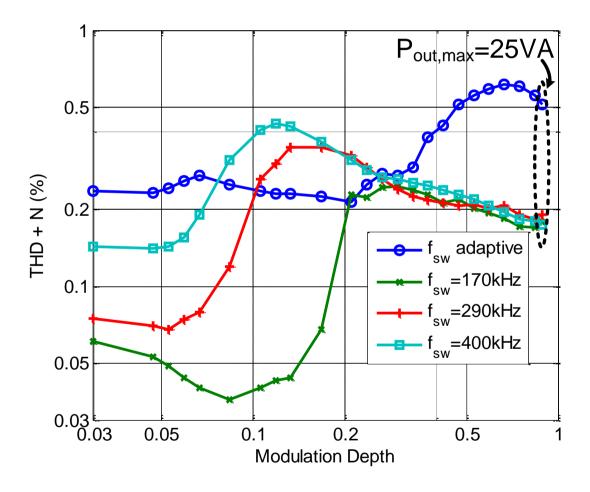

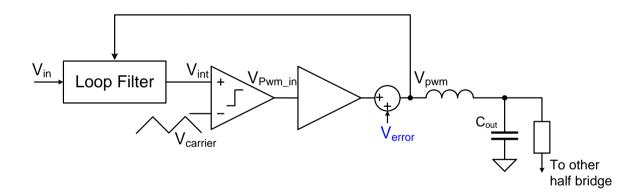

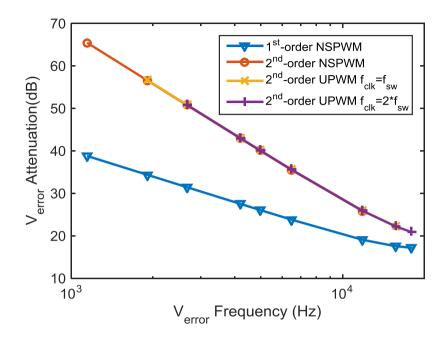

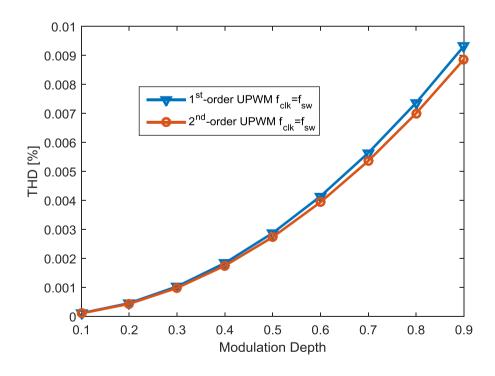

Finally, for the aim of idle loss reduction, the linearity degradation of dead time insertion and switching frequency increase is discussed in this thesis. To cope with this linearity degradation, both open-loop and closed-loop error correction techniques are explored and it is further shown that a higher-order loop filter combined with uniform sampling once per switching cycle is potentially a suitable choice for closed-loop fixed-carrier class-D implementations.

# **SAMENVATTING**

In moderne elektronica zijn sensoren en actuatoren allom vertegenwoordigd als interface tussen het toenemend digitale domein en de fysieke wereld. Hetzelfde geldt voor de vermogensversterkers om die actuatoren aan te sturen. Dit proefschrift richt zich op het ontwerp en de optimalisatie van klasse D versterkers die gebruikt worden om capacitieve piezoelektrische belastingen aan te sturen in toepassingen op het gebied van trillings- en geluidsreductie. Het voornaamste doel is het vermogensrendement van klasse D versterkers te verbeteren ten opzichte van bestaande ontwerpen.

Om meer inzicht te krijgen in het rendement van klasse D versterkers, is een model gemaakt dat de bijdrages van de verschillende dissipatiemechnismen beschrijft. Deze analyse laat zien dat schakelverliezen potentieel de belangrijkste bijdrage aan de dissipatie kunnen leveren, en dat snel schakelen deze bijdrage kan verminderen door overlap van spanning en stroom in de vermogenstransistoren te voorkomen. Verder blijkt dat als de schakelfrequentie gevariëerd wordt, er een minimum is in de totale dissipatie dat afhangt van het momentane uitgangsvermogen van de versterker. Ook blijkt dat de rustverliezen kunnen worden verminderd door een dode tijd te introduceren en de schakelfrequentie te verhogen.

Deze analyse volgend, is een snel schakelende uitgangstrap ontworpen met het doel de schakelverliezen te beperken. Deze uitgangstrap is ongevoelig voor schakeleffecten op de interne voeding door het gebruik van intern gereguleerde voedingsspanningen, een gate aansturing met variabele sterkte en een efficiënte 2-traps level shifter. Hierdoor worden snelle schakeltransisties bereikt met weinig verliezen waardoor de gerealiseerde chip met de uitgangstrap een vermogensrendement bereikt van 94%. Ook wordt een methode beschreven om de sterkte van de gate aansturing te dimensioneren, waaruit blijkt dat de gate aansturing met variabele sterkte het rendement sterk kan verbeteren als schakeleffecten op de interne voeding de limiterende factor zijn.

Ook gebaseerd op de dissipatie-analyse wordt een klasse D versterker met verbeterd rendement ontworpen en gerealiseerd. De versterker reguleert zijn schakelfrequentie op zo'n manier dat over het gehele vermogensbereik minimale dissipatie wordt bereikt. Deze techniek is gebaseerd op het waarnemen van de spanning op de schakeluitgang op het moment dat de vermogenstransistoren aanschakelen. Een prototype chip is gerealiseerd en bereikt 93% rendement op 45W uitgangsvermogen, > 80% op 4.5W en > 49% op 0.45W.

Tenslotte wordt, met het doel de rustverliezen te beperken, het effect van dode tijd en een hoge schakelfrequentie op de lineariteit van de versterker verkend. Om vermindering van de lineariteit te voorkomen worden open- en gesloten lus foutcorrectie mechanismen verkend. Aangetoond wordt dat een hogere-orde lusfilter in combinatie met uniforme bemonstering van één maal per schakelperiode een geschikte keus is voor klasse D versterkers met een vaste schakelfrequentie.

# List of Abbreviations

ESR Equivalent Series Resistance

HSw Hard Switching

LED Light Emitting Diode

NSPWM Natural Sampling Pulse Width Modulation

PA Power Amplifier

PD Pull Down

PU Pull Up

PWM Pulse Width Modulation

SSw Soft Switching

THD Total Harmonic Distortion

UGB Unity Gain Bandwidth

UPWM Uniform Pulse Width Modulation

# **CONTENTS**

| 1. IN | NTRODUCTION                                                                 | 1  |

|-------|-----------------------------------------------------------------------------|----|

| 1.1   | Power Amplifiers and Drivers                                                | 1  |

| 1.2   | Overview of Power Amplifier Types                                           | 3  |

| 1.3   | Design Aspects of Class-D Amplifiers                                        | 6  |

| 1.4   | Motivation and Thesis Outline                                               | 9  |

| 2. C  | LASS-D DISSIPATION: MODELING AND OPTIMIZATION                               | 11 |

| 2.1   | Introduction                                                                | 11 |

| 2.2   | Class-D Power Stage Dissipation Sources                                     | 12 |

| 2.3   | V <sub>pwm</sub> -Switching-Induced Power Loss Analysis                     | 15 |

| 2.4   | Verification of Loss Analysis                                               | 20 |

| 2.5   | Design Optimizations: Motivation for Research in Chapter 3-5                | 21 |

| 2.6   | Conclusions                                                                 | 23 |

|       | WITCHING LOSS REDUCTION – FAST-SWITCHING POWER ST                           |    |

| 3.1   | Introduction                                                                | 25 |

| 3.2   | Gate driver sizing issues                                                   | 27 |

| 3.3   | Floating gate driver design                                                 | 36 |

| 3.4   | Power-Efficient 2-step level shifter                                        | 44 |

| 3.5   | Measurement results                                                         | 47 |

| 3.6   | Conclusions                                                                 | 51 |

|       | XTENDING HIGH-EFFICIENCY OUTPUT POWER REGION – ITCHING FREQUENCY REGULATION | 53 |

| 4.1   | Introduction                                                                | 53 |

| 4.2   | Efficiency Improvement with Switching Frequency Regulation                  | 54 |

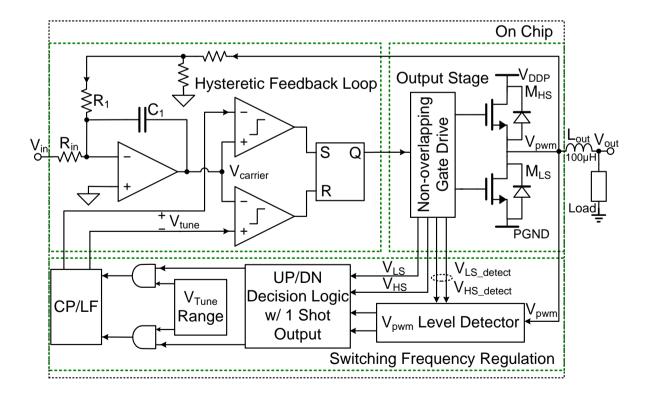

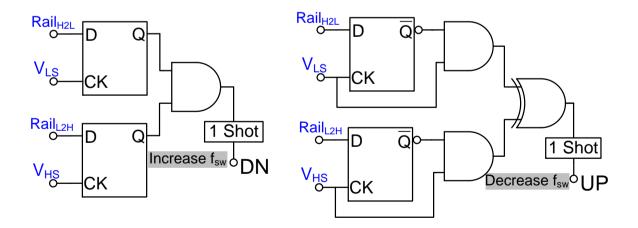

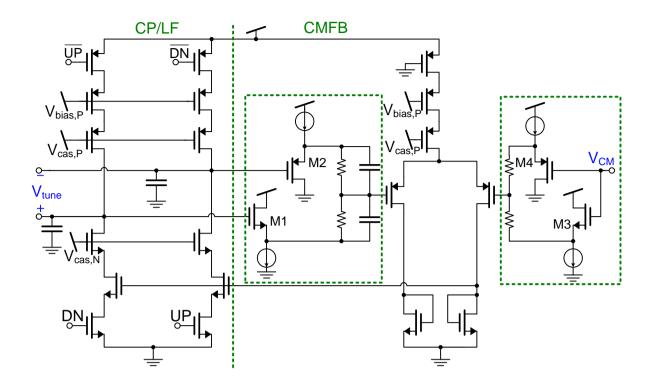

| 4.3   | Circuit implementation                                                      | 60 |

| 44    | Measurement results                                                         | 63 |

| 4.5  | Conclusions                                                     | 67 |

|------|-----------------------------------------------------------------|----|

|      | MPROVING EFFICIENCY AT IDLE/LOW OUTPUT POWER – DEAD TIME ERTION |    |

| 1110 |                                                                 | U  |

| 5.1  | Introduction                                                    | 69 |

| 5.2  | Power stage output error in SSw operation                       | 69 |

| 5.3  | Output stage error correction                                   | 72 |

| 5.4  | Feedback loop configuration                                     | 74 |

| 5.5  | Conclusions                                                     | 80 |

| 6. C | ONCLUSIONS AND FUTURE WORK                                      | 81 |

| 6.1  | Summary and Conclusions                                         | 81 |

| 6.2  | Original Contributions                                          | 84 |

| 6.3  | Recommendations for Future Work                                 | 84 |

| REF  | FERENCES                                                        | 87 |

| LIS  | Γ OF PUBLICATIONS                                               | 95 |

| ACI  | KNOWLEDGEMENTS                                                  | 97 |

| AB(  | OUT THE AUTHOR 10                                               | 01 |

## CHAPTER ONE

## 1. Introduction

#### 1.1 Power Amplifiers and Drivers

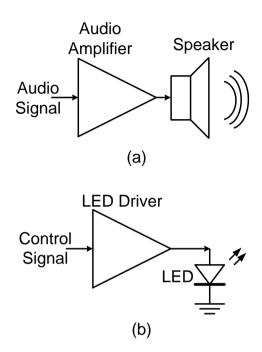

The continuous evolution of modern electronics and information technology has transformed increasingly more aspects of our daily life into the digital realm. Yet to interface with the real physical world, transducers [1] are ubiquitous, and the same holds for the power amplifiers (PAs) and drivers for driving them. Fig. 1.1 shows just two of many possible examples of such transducer applications, i.e. a loudspeaker and a Light Emitting Diode (LED). Fig. 1.1(a) illustrates the case in which the loudspeaker transforms electrical power into sound. In Fig. 1.1(b), the LED turns electrical power into light. In both cases, power drivers are required to provide the power for the transducers to function.

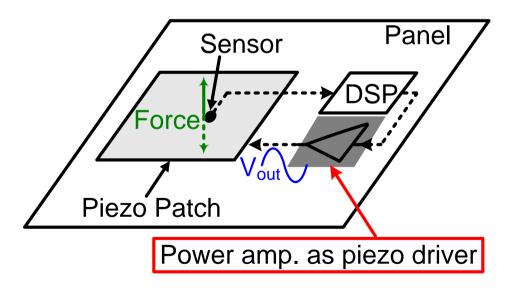

This thesis will focus on the design and optimization of high-voltage power amplifiers tailored for driving capacitive piezoelectric actuator loads. Fig. 1.2 illustrates such an application scenario where a power amplifier serves as a piezo-actuator driver in an active vibration and noise control system [2], [3], [4]. As shown in Fig. 1.2, first the vibration or noise generated through the panel structure is sensed by a sensor (e.g. an accelerometer). Then through dedicated control systems, the piezoelectric actuator, which is driven by a piezo driver, generates an anti-phase vibration to cancel or attenuate the existing vibration or noise. In these applications, the piezo driver needs to provide tens to hundreds of volts actuation voltage for the piezoelectric actuator. Besides, the signal frequency is in the range of several tens to hundreds of Hz and the piezoelectric actuator can electrically be treated as a capacitive load. With typically several tens of Watt reactive power being processed and the compactness requirement mandating the usage of small or even no heat sinks, the power amplifier for driving the piezo actuators needs to have very high efficiency. This is the main motivation

and the starting point for the research described in this thesis. For the next subsection we will review some classical power amplifier topologies and discuss their corresponding power efficiency.

Fig. 1.1. Typical examples of transducers and their corresponding power drivers (a) speakers where electrical power is transformed into sound (b) light emiting diodes where electrical power is transformed into light

Fig. 1.2. Illustration of an active vibration and noise control system where a PA is adopted as an piezo driver

#### 1.2 Overview of Power Amplifier Types

#### 1.2.1 Linear Class-B Amplifiers

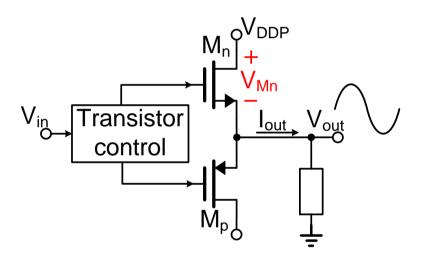

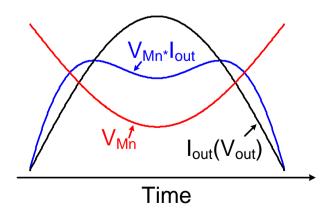

A typical push-pull output stage for class-B amplifiers [5] is shown in Fig. 1.3. The two output power transistors conduct alternately to avoid quiescent current draw from the power supplies. However, during their respective conducting phase, the output transistors have continuous V-I overlap loss, as shown in Fig. 1.4, where V<sub>Mn</sub> represents the voltage across M<sub>n</sub> during the phase that it is conducting. Consequently class-B amplifiers can only have a theoretical maximum power efficiency of 78.6% [5] for a full swing sinusoidal output voltage. For lower output powers and signals with a larger peak-to-average ratio than sinewaves, efficiency is easily an order of magnitude lower [6].

Fig. 1.3. Basic push-pull output stage for a class-B amplifier

Fig. 1.4. Illustration of continuous V-I overlap loss on a class-B output transistor

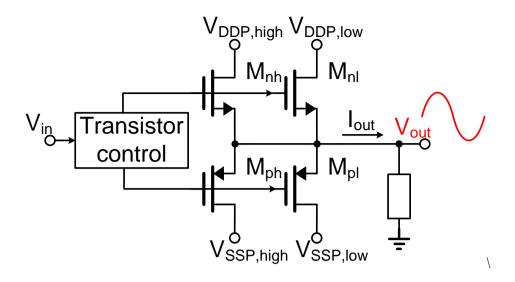

Fig. 1.5. Illustration of a class-G output stage, with two separate supply voltage sets

An improvement to the basic class-B output stage can be made by adding multiple supplies to the power stage, i.e. a class-G amplifier [7]. For the class-G topology, the amplifier switches between low- and high-voltage supplies based on the instantaneous signal amplitude. This way the V-I overlap loss can be significantly reduced, especially for low signal levels, and the efficiency is improved compared to class-B designs. Yet the continuous conduction nature of the output stage is not changed and the theoretical maximum efficiency is still limited.

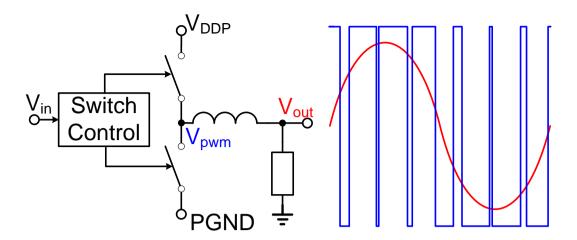

#### 1.2.2 Switching Class-D Amplifiers

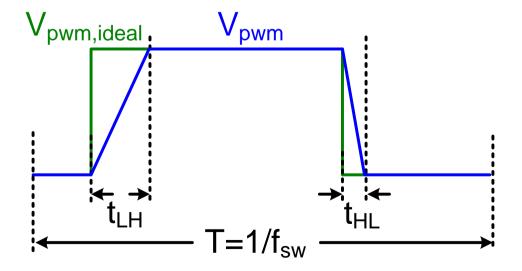

In comparison to linear amplifiers, class-D switching amplifiers (Fig. 1.6) can offer a much higher maximum power efficiency [8]- [23]. Their superior efficiency can be attributed to the switching nature of the output stage, where the continuous V-I overlap loss in the output transistors is eliminated. Fig. 1.6 shows the working principle of a class-D amplifier. An input voltage signal is converted into two control signals for controlling the output switches. The switching output node  $V_{pwm}$  is pulse-width modulated (PWM) with its duty cycle proportional to the input voltage. The output low-pass filter then filters out the high-frequency content of the  $V_{pwm}$  signal and the final  $V_{out}$  is an amplified version of the low-frequency  $V_{in}$ .

Fig. 1.6. Working principal of a class-D amplifier

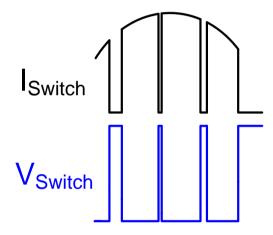

Fig. 1.7. Illustration of voltage and current waveforms in the output switches

Assuming that the output switches are ideal and the switching transitions are infinitely fast, no simultaneous voltage drop and current conduction will occur in the switches. This is shown in Fig. 1.7, where  $I_{switch}$  denotes the current flowing through the switch and  $V_{switch}$  is the voltage across the switch. Thus ideally class-D output stages have no dissipation and their power efficiency is 100%. For this reason, class-D amplifiers have gained popularity and are widely adopted for audio power amplification, both for high-power [8]- [14] and low-power [15]-[23] applications.

#### 1.2.3 Combination of Linear and Switching Amplifiers

In literature the combination of linear and switching techniques has also been explored, with either series- [24] or parallel-connected [25] linear/switching topologies. The advantage of such techniques is that the switching-induced output voltage ripple can to a large extend be eliminated. Also, the bandwidth of the amplifier can be improved. All of these are achieved without resorting to a power-consuming high switching frequency of the class-D amplifier, because the linear amplifier assists the improvements. For this reason, parallel-connected linear and switching amplifiers can be adopted in many high signal bandwidth applications where low output voltage ripple is also required [26]-[28], with better efficiency compared to the use of only switching techniques. Yet for audio-frequency applications, the addition of an extra linear or switching amplifier is not so attractive from a power efficiency point of view, since a low switching frequency is already adequate for the low signal bandwidth. The extra linear amplifier will only add extra power consumption.

#### 1.2.4 Discussion

Considering the efficiency performance of various types of linear and switching power amplifiers, this thesis will focus on the design and optimization of high-voltage class-D amplifiers, since they can offer the highest power efficiency in the kHz signal frequency range. This is especially motivated by the application discussed in this thesis. The piezoelectric load is capacitive in the signal frequency and mainly reactive output power is being processed with hardly any real power delivered to the load. Consequently the efficiency of the piezo driver [29]-[33] should be maximized. An overview of state of the art class-D designs will be given in the next subsection.

#### 1.3 Design Aspects of Class-D Amplifiers

Power efficiency and linearity are two major performance criteria used for class-D designs [8]- [23] and will be discussed next. Besides these two performance criteria, other features like incorporating the output filter in the feedback network, electro-magnetic interference minimization and robustness are also important for a class-D design and will also be discussed.

#### 1.3.1 Power Efficiency

Various dissipation sources lead class-D PA efficiency away from the ideal 100% and typical peak power efficiency is around 90%. The dissipation sources have been summarized and modeled with various level of accuracy [34]-[38]. In [34], conduction loss due to the output power switch on resistance and switching loss resulting from V-I overlap during switching are considered to be the main loss mechanisms. It is also shown that proper sizing of the power switch W/L ratio can optimize the total dissipation. Yet the modeling of the switching loss in [34] is rather simplified. Detailed modeling of the switching loss can be found in [35]-[38]. The distinction between lossless and lossy switching transitions is important, as the optimization procedure can be rather different with contributing dissipation sources varying.

Passive component losses can also contribute significantly to the total loss of the class-D output stage. These include the losses from both the output power inductors and the filtering capacitors [39]-[42]. Regarding the loss mechanisms, there exists conduction loss due to the equivalent series resistance (ESR) of these passive components. Moreover, hysteretic core loss of the output power inductors is also an important contributor [41],[42]. This loss mechanism can be attributed to the unrecoverable part of the energy required for the changing magnetization of the core material.

Moreover, efficiency optimization should also be done for low output powers and for signals with high peak-to-average ratio. Light load efficiency improvement can be realized by identifying the dominating dissipation source for light load condition and find methods to minimize it [22], [43]-[46]. In this respect, adaptive techniques are usually being used. In [22] changing the power transistor size according to output power level is used while in [44] and [46] switching frequency is adaptively changed.

#### 1.3.2 Linearity

Class-D power stage non-idealities introduce distortion to the amplifier's output signal [47],[48]. Feedback loop gain can suppress these error and various high-order feedback loops with sufficient loop gain are implemented for this reason [49]-[51]. Yet it has been shown that higher-order loop filters does not necessarily mean better linearity performance due to the extra error introduced by the PWM-based feedback loop itself [52]-[54]. This error is

related to the PWM residual ripple voltage not being completely attenuated by the loop filter. For getting minimum aliasing error, in [52] a minimum aliasing error loop filter is adopted to suppress the ripple-induced error. In [55] sampling after the loop filter is used to significantly reduce this ripple voltage.

#### 1.3.3 Full Output Filter Control

Conventional class-D feedback networks are connected to the switching output node of the power stage instead of the actual output node of the amplifier [8]-[23]. This is considering the two additional poles introduced by the second-order low-pass filter between the switching output node and the actual output. To get high loop gain for error suppression, low frequency poles, which is at frequencies much lower than the poles' frequency of the second-order low-pass filter, have to be introduced to the feedback loops. Thus additional zeros should be introduced for frequency compensation when the output filter is included in the feedback loop. This has been done for both self-oscillating [56],[57] and fixed-carrier [58],[59] class-D topologies, by properly compensating the phase lag resulting from the output filter. The most significant advantage of incorporating the output filter in the feedback loop is that the non-linearity of the power inductor is no longer important, since its error can also be corrected. Low-cost and compact size power inductors are then feasible for the output filter [59].

#### 1.3.4 Electro-Magnetic Interference (EMI) Issues

Compared to linear amplifiers, the switching nature of class-D amplifiers causes them to have potential EMI issues, because of the high frequency harmonics generated through the switching actions. From a system design point of view [60], proper shielding and grounding of the amplifier is necessary. Besides, the PCB design should avoid long traces and loops interfacing with external and on-chip components. From a circuit design point of view, proper switching sequences [61] as well as slow switching transitions [62],[63] can help reducing EMI. Moreover, similar to switched-mode power supply designs [64]-[68], spread spectrum techniques can be applied to class-D designs for EMI reduction [69].

#### 1.3.5 Protection Circuitry

Robustness is another important requirement for power amplifiers and thus various protection circuits for the power stage are required. These include over current protection, over temperature protection etc. Especially for high-voltage designs, the over current protection circuit design is not straightforward since the switching output node has a voltage swing higher than any maximum gate source voltage allowable. Proper isolation and accurate over current detection circuits can be found in [9] and [70]. In addition, for speaker protection in audio applications, accurately sensing the load current in the switching output stage is also challenging and has been addressed in [19] and [23].

#### 1.4 Motivation and Thesis Outline

#### 1.4.1 Motivation – Power Efficiency

As discussed previously, class-D PAs can offer the highest power efficiency in the kHz signal frequency range among the various PA types. Yet how to achieve this high efficiency and whether further optimization is possible is rarely being addressed in a systematic way in literature [8]-[23]. In this thesis the main research motivations/questions are listed as follows,

- 1) What are the main dissipation sources in an integrated high voltage class-D amplifier?

- 2) How can we further improve its efficiency performance?

- 3) In circuit design how can we implement these improvements?

#### 1.4.2 Thesis Outline

The remainder of the thesis is organized as follows:

With efficiency improvement being the primary motivation for this work, chapter 2 starts with a detailed analysis on class-D dissipation sources. A dissipation model is established that can accurately predict the class-D dissipation across different load conditions as well as different switching scenarios. This dissipation analysis serves as the guideline for the following chapters, with three feasible power efficiency optimization methods given for further exploration in the following chapters. The three optimization directions aim for

minimizing the switching loss, extending the high-efficiency output power range as well as improving efficiency at idle/low output power, respectively.

Chapter 3 focuses on minimizing switching loss in an integrated high-voltage class-D power stage realization. It is shown that fast switching is required to minimize the switching loss associated with V-I overlap. But with parasitic inductances between the on-chip power stage and the external power supplies present, fast switching causes large di/dt and in turn significant on-chip supply bounce. On-chip floating supply regulators and in-cycle variable gate driver strength are introduced to minimize the influence of on-chip supply bounce and realize fast switching transitions. In addition, the design of robust level shifter circuits for logic signal communication between different supply domains are also discussed in this chapter.

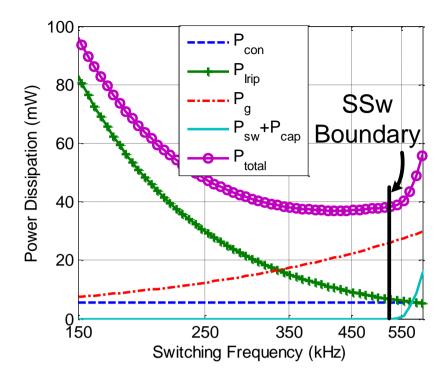

Chapter 4 presents an optimal-efficiency-tracking switching frequency regulation technique for extending the high-efficiency output power range. It is analyzed here that the inductor ripple loss is the dominant dissipation source at low output power levels, as long as the switching transitions on the switching output node is lossless soft switching. A regulation loop is designed that can always ensure that switching transitions are at the boundary between lossless soft switching and hard switching, thus simultaneously minimizing switching loss and inductor ripple loss. The realized amplifier can maintain high efficiency over orders of magnitude output power variation.

Chapter 5 discusses methods for further improving efficiency at idle/low output power. This is by inserting dead time in the output stage as well as operating the power stage with higher switching frequency. However, this will make the linearity performance worse. Methods for optimizing the linearity are discussed, both for open-loop and closed-loop situations.

Finally chapter 6 gives conclusions and recommendations for future work.

## **CHAPTER TWO**

# 2. Class-D Dissipation: Modeling and Optimization

(Section 2.2 to section 2.3 are taken from part of the author's paper accepted to IEEE Journal of Solid-State Circuits in 2015 [88].)

#### 2.1 Introduction

This chapter will focus on analyzing and developing a dissipation model for high-voltage class-D power stages. The main purpose for developing such a model is to identify the dominating dissipation sources in class-D power stages with high supply voltage (in the range of 100V). Subsequently with all the dominating dissipation mechanisms identified, various methods for improving the power stage efficiency can be developed. These efficiency improvement methods will serve as design guidelines for the following chapters in this thesis.

In literature, switching power stage dissipation has been modeled with various levels of accuracy [34]-[38]. However, with the switching stage operating conditions (switching frequency, supply voltage) varying by orders of magnitude over operating conditions, the dominating dissipation sources are different for each case. No dissipation models clarifying the dominating loss mechanisms of a high-voltage class-D power stage are available, especially when considering that dominating dissipation sources can vary for different output power levels. For this reason, it is necessary to develop a comprehensive model with all the dissipation sources that can contribute significantly to the high-voltage case included. Subsequently, with the developed model it can be clearly seen what the dominating dissipation sources are and how they can be optimized.

This chapter is organized as follows: section 2.2 shows all the contributing dissipation sources for a class-D power stage. With the switching loss being an important dissipation source, section 2.3 analyzed this loss mechanism in detail. The developed dissipation model is verified against transistor-level simulation results in section 2.4. Finally, section 2.5 draws conclusions and discusses efficiency improvements that are investigated in the subsequent chapters.

#### 2.2 Class-D Power Stage Dissipation Sources

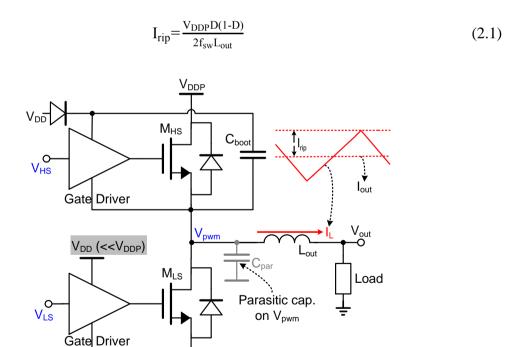

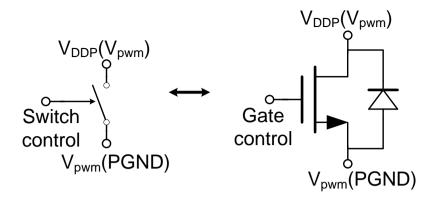

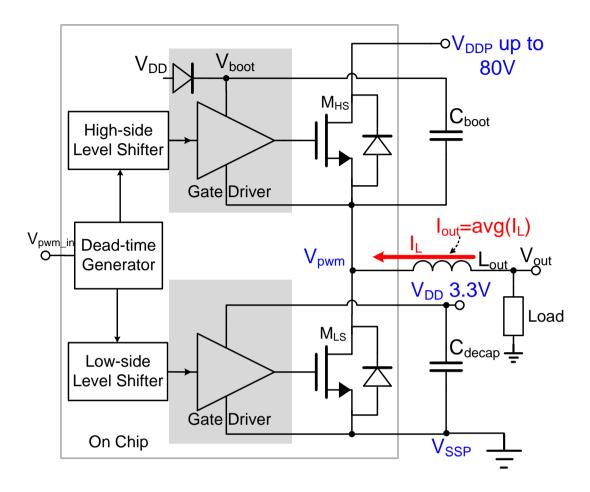

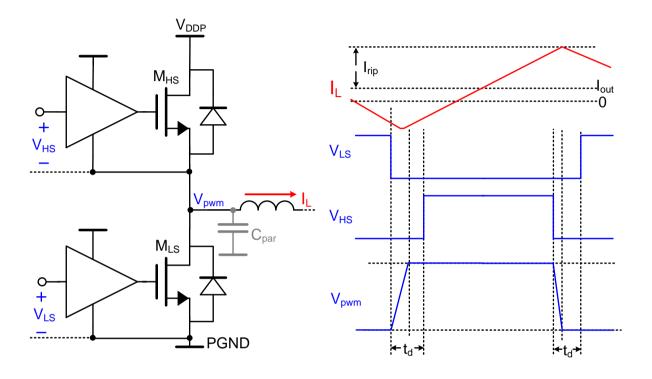

For class-D dissipation analysis, a basic class-D power stage topology is shown in Fig. 2.1. Two N-type DMOSFETs are used as power switches (Fig. 2.2) and their on/off state is controlled by two gate driver circuits. Typically the maximum  $V_{ds}$  of the DMOSFETs is much higher than their  $V_{gs}$ , therefore the gate driver supply  $V_{DD}$  is much lower than the output stage supply  $V_{DDP}$ . The current  $I_L$  flowing through the power inductor  $L_{out}$  can be divided into two parts: the average load current within one switching cycle with value  $I_{out}$  and the inductor ripple current with amplitude  $I_{rip}$  expressed as [71]:

Fig. 2.1. Basic topology of a high-voltage class-D power stage

**PGND**

Fig. 2.2. N-type DMOS FET devices as both high-side and low-side power switches for high-voltage class-D amplifier implementation.

where  $f_{sw}$  is the class-D switching frequency and D is the  $V_{pwm}$  duty cycle. As we can see from (2.1),  $I_{rip}$  is influenced by numerous circuit operating parameters. This makes the ratio between  $I_{out}$  and  $I_{rip}$  also dependent on these parameters. Yet the  $I_{out}$ - $I_{rip}$  ratio is important for identifying the different dissipation contributions at changing output power levels, as will be discussed in the following.

The main dissipation sources in a class-D power stage are listed in TABLE I. Among them, conduction loss  $P_{con}$  is due to  $I_{out}$  flowing through the on resistance of the power transistors  $(r_{on})$  and the equivalent series resistance of  $L_{out}$   $(r_{esr})$ ,

$$P_{con} = I_{out}^2(r_{on} + r_{esr})$$

$$(2.2)$$

Ripple loss  $P_{Irip}$  is caused by the  $I_{rip}$  conduction in  $r_{on}$  and  $r_{esr}$ , as well as the magnetic core loss in  $L_{out}$ . Assuming  $I_{out}$  is constant during one switching cycle with the triangle  $I_{rip}$  superimposed on it, the conduction loss contribution of  $I_{rip}$  can be expressed as,

$$P_{\text{Irip,cond}} = \frac{1}{3} I_{\text{rip}}^{2} (r_{\text{on}} + r_{\text{esr}})$$

(2.3)

There is also magnetic core loss, related to the hysteresis of the B-H loop of the inductor core material. This loss is the unrecoverable part of the energy required for the changing magnetization of the core material and is expressed as [41],

$$P_{\text{Irip,core}} = K(\text{Vol})(f_{\text{sw}})^{x} (\Delta B)^{y}$$

(2.4)

where K is a constant for core material, Vol is the core volume, x is the power factor for switching frequency  $f_{sw}$  and y is a power factor for the changing magnetic flux density with amplitude  $\Delta B$ . The changing magnetic field  $\Delta H$ , which varies together with  $\Delta B$  following the B-H curve, is directly proportional to  $I_{rip}$ . Thus by adopting x=1 and y=2 as a simplified power factor [72], (2.4) can be rewritten using  $I_{rip}$  as.

$$P_{\text{Irip,core}} = \frac{1}{3} I_{\text{rip}}^2 r_{\text{eq}} \tag{2.5}$$

with  $r_{eq}$ = 3K(Vol) $f_{sw}$  being the equivalent resistance for the core loss contribution. Further combining the  $I_{rip}$ -induced conduction loss (2.3) and magnetic core loss (2.5),

$$P_{Irip} = \frac{1}{3} I_{rip}^2 (r_{on} + r_{esr} + r_{eq})$$

(2.6)

Gate driver loss  $P_g$  results from charging/discharging the gate capacitance of  $M_{HS}/M_{LS}$  when turning  $M_{HS}/M_{LS}$  on/off,  $P_g$  for  $M_{HS}$  and  $M_{LS}$  combined can be expressed as:,

$$P_g = Q_g V_{DD} f_{sw}$$

(2.7)

where  $Q_g = \int_{PGND}^{V_{DD}} C_g(V) dV$  with  $C_g$  the total gate capacitance of  $M_{HS}$  and  $M_{LS}$ . Total gate charge instead of the gate capacitance is adopted here for easier and more precise power loss calculation because the parasitic capacitances of a power MOSFET show large variations over different bias conditions [36].

TABLE I. LIST OF MAIN DISSIPATION SOURCES IN A CLASS-D POWER STAGE

| Dissipation Type                 | Source                                                                                                      | Analytical Expression |

|----------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------|

| Conduction loss Pcon             | I <sub>out</sub> conduction                                                                                 | (2.2)                 |

| Ripple loss P <sub>Irip</sub>    | I <sub>rip</sub> conduction                                                                                 | (2.6)                 |

| Gate driver loss P <sub>g</sub>  | Charging/discharging the gate capacitance of M <sub>HS</sub> /M <sub>LS</sub>                               | (2.7)                 |

| Capacitive loss P <sub>cap</sub> | Charging/discharging C <sub>par</sub> on V <sub>pwm</sub> by M <sub>HS</sub> /M <sub>LS</sub>               |                       |

| Switching loss Psw               | During hard switching, V-(I <sub>L</sub> +I <sub>rr</sub> ) (2.13) overlap dissipated in the power switches |                       |

Both the capacitive loss  $P_{cap}$  and the switching loss  $P_{sw}$  are induced by the switching at the pulse-width-modulated (PWM) output node  $V_{pwm}$ . With a high-voltage  $V_{DDP}$ ,  $P_{sw}+P_{cap}$  can be significant. Yet whether these two dissipation sources exist, depends on the  $V_{pwm}$  switching

waveforms and consequently on the  $I_{out}$ - $I_{rip}$  amplitude, as will be discussed in detail in the following.

#### 2.3 V<sub>pwm</sub>-Switching-Induced Power Loss Analysis

Depending on the inductor current direction and amplitude at the moment of switching, three  $V_{pwm}$  switching types can be identified as follows (using  $V_{pwm}$  low-to-high transitions for illustration):

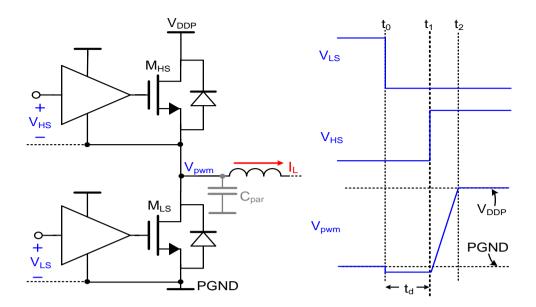

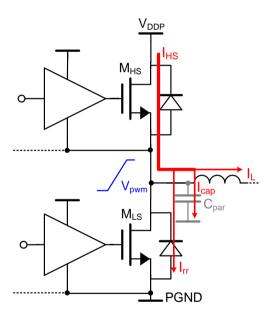

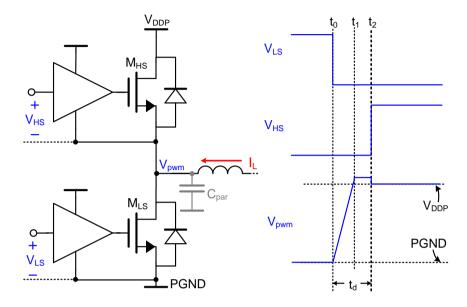

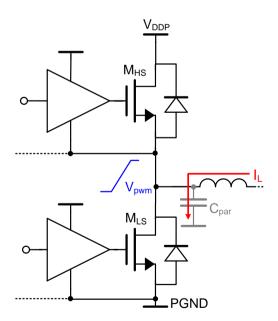

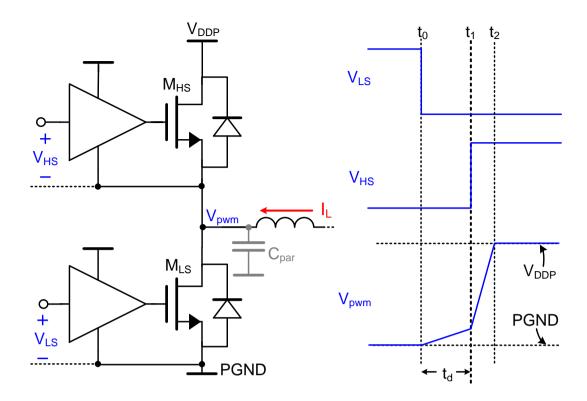

1) Hard switching (HSw). As shown in Fig. 2.3, the inductor current  $I_L$  is flowing out of the power stage as  $M_{Ls}$  is turned off at  $t_0$ . During the dead time  $t_d$ , when both power transistors are kept off,  $I_L$  has nowhere to go but through the body diode of  $M_{LS}$ . As a result  $V_{pwm}$  will stay near the PGND level. This remains until  $M_{HS}$  is turned on at  $t_1$  when the dead time  $t_d$  is finished. The switching transition begins when the current  $I_{HS}$  in  $M_{HS}$  is large enough to provide the current for charging  $C_{par}(I_{cap})$ , the reverse-recovery current [11] of the body-diode of  $M_{LS}$  ( $I_{rr}$ ), and the inductor current  $I_L$ , as illustrated in Fig. 2.4. Among these three types of current that contribute to  $M_{HS}$  dissipation, the  $I_{cap}$  contribution can be expressed as:

$$P_{\text{cap,HSw}} = \frac{1}{2} Q_0 V_{\text{DDP}} f_{\text{sw}}$$

(2.8)

where  $Q_o = \int_{PGND}^{V_{DDP}} C_{par}(V) dV$  when  $M_{HS}$  is on while  $M_{LS}$  is off. The  $Q_o$  expression is also for more precise calculation of  $P_{cap}$  considering the nonlinear  $C_{par}$ .

As for the contribution of  $I_{rr}$  and  $I_L$ , the transition time from  $t_1$  to  $t_2$  is determined by the gate driver pull-up strength [29] [35] and thus the V-I overlap part contributed by  $I_L$  will be dependent on the gate driver design. To simplify the modeling of  $P_{sw}$ , we assume that the gate driver pull-up strength is large enough to make the transition very fast and to satisfy  $I_L*(t_2-t_1)$  <<  $Q_{rr}$  (the reverse recovery charge). Then we get

$$P_{\text{sw,HSw}} = \frac{1}{2} Q_{\text{rr}} V_{\text{DDP}} f_{\text{sw}}$$

(2.9)

P<sub>cap,HSw</sub>+P<sub>sw,HSw</sub> then will be the total M<sub>HS</sub> dissipation during the hard switching transition.

Fig. 2.3. Illustration of a  $V_{pwm}$  hard switching transition, where  $M_{HS}$  has to complete the transition with V-I overlap. In this case switching-induced loss results in  $M_{HS}$ .

Fig. 2.4. Active power switches ( $M_{HS}$  in this example) has to provide current for a hard switching transition, resulting in  $V_{pwm}$  switching-induced loss.

2) Soft switching (SSw). The switching dynamic changes when the inductor current  $I_L$  is flowing into the power stage at the transition time, as shown in Fig. 2.5. In this case when  $M_{LS}$  is turned off at  $t_o$ ,  $I_L$  will immediately begin to charge  $C_{par}$  and  $V_{pwm}$  begins to rise. If the value of  $I_L$  is large enough to satisfy

$$I_L * t_d \ge Q_o'$$

(2.10)

where  $Q_o^{'} = \int_{PGND}^{V_{DDP}} C_{par}(V) dV$  when both  $M_{HS}$  and  $M_{LS}$  are off, the switching transition will finish within the dead time at  $t_1$  before  $M_{HS}$  is turned on at  $t_2$ . No V-I overlap in the active devices exists in this lossless soft switching transition (Fig. 2.6) and thus  $P_{sw,SSw} + P_{cap,SSw} = 0$ .

Fig. 2.5. Illustration of a  $V_{pwm}$  lossless soft switching transition, where the inductor current can fully charge  $V_{pwm}$  to  $V_{DDP}$  without resorting to the active devices  $M_{HS}/M_{LS}$ .

Fig. 2.6. The inductor current itself can accomplish the switching transition in lossless soft switching, without resorting to the active power switches.

3) Partial soft switching (PSSw). Same as in the case of lossless soft switching,  $I_L$  is flowing into the power stage at the transition time, as shown in Fig. 2.7. When  $M_{LS}$  turns off,  $I_L$  also immediately begins to charge  $C_{par}$ , thus  $P_{sw,PSSw}$ =0. However, if the value of  $I_L$  is too low to satisfy (2.10),  $C_{par}$  cannot be charged to  $V_{DDP}$  within the dead time.  $M_{HS}$  is turned on to finish the rest of the transition with  $P_{cap,PSSw}$  loss expressed as:

$$P_{\text{cap,PSSw}} = \frac{1}{2} F^2 Q_0 V_{\text{DDP}} f_{\text{sw}}$$

(2.11)

where F represents the ratio of the remaining  $V_{pwm}$  transition that has to be finished by the active power switches and is approximated here as:

$$F = (Q'_0 - I_L t_d)/Q'_0$$

(2.12)

To summarize the combined  $P_{sw}+P_{cap}$  for the above three switching transition scenarios, we define the inductor current in the direction of flowing out of the power stage to be positive, then

$$P_{sw} + P_{cap} = \begin{cases} \frac{1}{2} (Q_{rr} + Q_o) V_{DDP} f_{sw} & \text{if } I_{out} - I_{rip} > 0 \\ 0 & \text{if } I_{out} - I_{rip} \le 0 \text{ and } \left| I_{out} - I_{rip} \right| * t_d \ge Q_o' \\ \frac{1}{2} F^2 Q_o V_{DDP} f_{sw} & \text{if } I_{out} - I_{rip} \le 0 \text{ and } \left| I_{out} - I_{rip} \right| * t_d < Q_o' \end{cases}$$

(2.13)

As for the  $V_{pwm}$  high-to-low transition,  $I_L$  now equals  $I_{out}+I_{rip}$ , which will be always flowing out of the power stage for positive  $I_{out}$ . This is a lossless soft switching transition when  $(I_{out}+I_{rip})*t_d\geq Q_o^{'}$  is satisfied, which is typically the case.

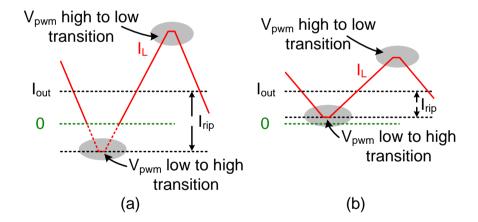

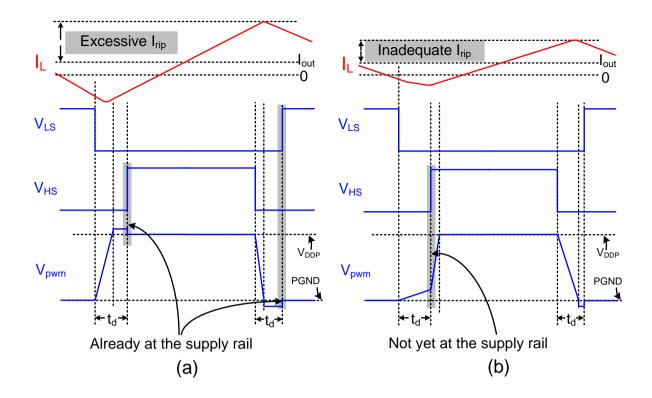

Considering the complete switching cycle with a positive  $I_{out}$  as shown in Fig. 2.8, a higher  $I_{rip}$  amplitude than  $I_{out}$  results in bidirectional  $I_L$  and consequently both switching transitions are soft switching (Fig. 2.8(a)), with partial soft switching for the low-to-high transition still possible. On the other hand, a lower  $I_{rip}$  amplitude than  $I_{out}$  results in unidirectional  $I_L$ , which means the low-to-high transition is hard switching (Fig. 2.8(b)).

Fig. 2.7. Illustration of a  $V_{pwm}$  transition partially completed by  $M_{HS}$ , resulting in  $P_{cap}$ . In this case the inductor current amplitude is not large enough to fully charge  $V_{pwm}$  to  $V_{DDP}$  within the dead time.

Fig. 2.8. Depending on the relative amplitude of  $I_{rip}$  and  $I_{out}$ , it can be that both  $V_{pwm}$  switching transitions are soft switching or one of the transitions is hard switching. (a) Bidirectional inductor current result in  $V_{pwm}$  low to high transition being soft switching. (b) Unidirectional inductor current flowing out of the power stage result in  $V_{pwm}$  low to high transition being hard switching

TABLE II. SUMMARY OF THE PARAMETERS USED IN SIMULATION

| Parameters                         | Value          |

|------------------------------------|----------------|

| Power Stage Supply VDDP            | 80V            |

| Gate Driver Supply V <sub>DD</sub> | 3.3V           |

| Output Inductance Lout             | 100μH          |

| V <sub>pwm</sub> Duty Cycle        | 0.5            |

| Dead Time t <sub>d</sub>           | 100ns          |

| DMOSFET's size                     | 56000µm/0.75µm |

TABLE III. PARAMETERS ASSOCIATED WITH THE POWER DMOSFETS FOR DISSIPATION CALCULATION

| Parameters                 | Values<br>(DMOSFET W/L=56000μm/0.75μm)              | Remarks                                                                                 |

|----------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------|

| On resistance ron          | 560mΩ                                               | On resistance of the DMOSFETs                                                           |

| Gate Charge Q <sub>g</sub> | 15nC                                                | $2*\int_{PGND}^{V_{DD}} C_g(V)dV$                                                       |

| Q <sub>o</sub>             | 8.5nC                                               | $\int_{PGND}^{V_{DDP}} C_{par}(V)dV$ (Both M <sub>HS</sub> and M <sub>LS</sub> are off) |

| Qo                         | 28nC                                                | $\int_{PGND}^{V_{DDP}} C_{par}(V) dV$ ( $M_{HS}$ is on)                                 |

| Qrr                        | [(I <sub>out</sub> -I <sub>rip</sub> )/100mA]·1.5nC | Reverse recovery charge (I <sub>out</sub> >I <sub>rip</sub> )                           |

#### 2.4 Verification of Loss Analysis

With analytical expressions for each of the dissipation sources listed in TABLE I as in (2.2), (2.6), (2.7) and (2.13), a comparison can be made between transistor-level power dissipation simulation and the analytical model. For the verification, we only consider the power loss of the transistors, i.e.  $r_{esr}$  and  $r_{eq}$  of the power inductor will not be considered yet. TABLE II shows a summary of the power stage design parameters [29] which have been used in both simulation and analytical models, while TABLE III lists the main parameters associated with the power DMOSFETs used in the analytical model.

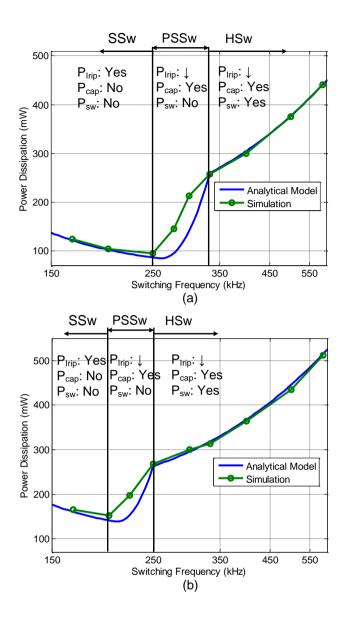

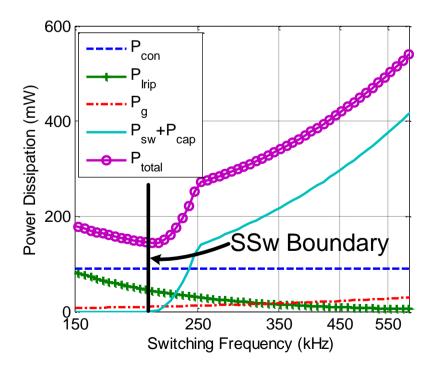

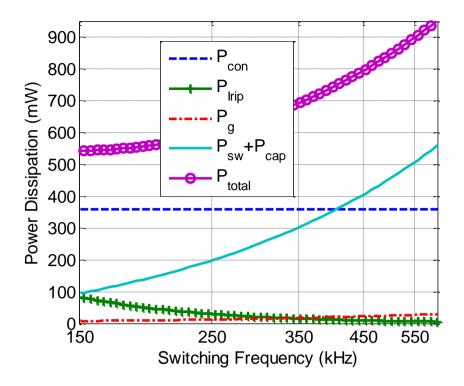

Fig. 2.9 shows the comparison between the transistor-level simulation results and the analytical model, with two different  $I_{out}$  settings. The analytical model predicts the dissipation of the power switches well across the three different switching scenarios, with the switching frequency  $f_{sw}$  varied for getting to different  $I_{rip}$  such that all three scenarios can be covered. The main discrepancy between the analytical model and the simulation lies in the PSSw region. This is due to the nonlinear  $C_{par}$ , which makes the remaining voltage and charge ratio F in (2.12) not precise.

Fig. 2.9. Comparison between analytical model and transistor-level simulation for the dissipation of the output stage. (a)  $I_{out}$ =300mA. (b)  $I_{out}$ =400mA. Here we use "yes" for the presence of a specific dissipation source and "no" for absence.

#### 2.5 Design Optimizations: Motivation for Research in Chapter 3-5

#### 2.5.1 Reducing switching loss

In the derivation of (2.9), the switching loss during hard switching, we have assumed that the V-I overlap part contributed by  $I_L$  ( $I_L*(t_2-t_1)$ ) is much smaller than the reverse recovery current contribution ( $Q_{rr}$ ). This requires that the gate driver pull-up strength is large enough

to make the transition time  $t_2$ - $t_1$  very short. The design challenges this brings with respect to supply bounce and the subsequent realization of a fast-switching class-D power stage will be discussed in Chapter 3.

#### 2.5.2 Extending high-efficiency output power range

When comparing Fig. 2.9(a) and Fig. 2.9(b), we can observe that a minimum power dissipation exists for each  $I_{out}$  case, each with a different optimal switching frequency. This motivates us to investigate on when the switching frequency is optimal and how to get to it. Then by varying  $f_{sw}$  in the desirable way we can extend the high-efficiency output power range, as will be discussed in Chapter 4.

#### 2.5.3 Improving efficiency at idle/low output power

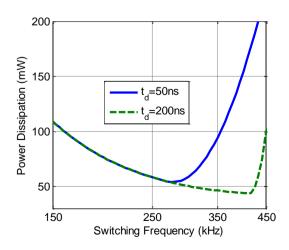

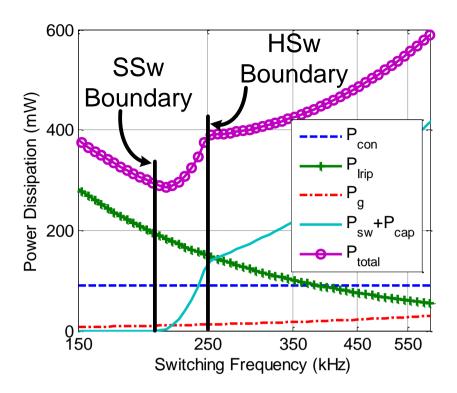

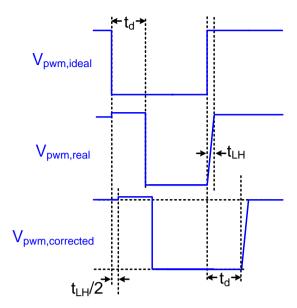

Fig. 2.10 shows the simulation result using the analytical model of the class-D power stage dissipation at two different dead time  $t_d$  settings (50ns and 200ns respectively with 200mA  $I_{out}$ ). With the larger  $t_d$  setting, the output stage can achieve a lower total dissipation. The reason is that the larger  $t_d$  allows lossless SSw with less  $I_{rip}$  and thus higher  $f_{sw}$ , where  $I_{rip}$  induced loss  $P_{Irip}$  is less. This fact can be exploited to further optimize the efficiency at idle/low output power. However, inserting a larger  $t_d$  to the output stage for efficiency improvement will compromise the distortion performance [72],[73]. The simultaneous optimization of low-power efficiency and linearity performance will be further discussed in Chapter 5.

Fig. 2.10. Analytical model simulation of the class-D power stage dissipation at  $I_{out}$ =200mA, with a dead time of 50nS and 200ns respectively.

#### 2.6 Conclusions

In this chapter, a detailed analytical modeling of the main class-D power stage dissipation sources is established. Further more, the analytical loss model is verified by comparing to transistor-level simulation results of across all load conditions and switching scenarios. Based on the power loss analysis, directions for further optimizing the power stage efficiency are given, which serve as motivations for the works done in chapter 3-5.

#### CHAPTER THREE

## 3. Switching Loss Reduction – Fast-Switching Power Stage Design

(Section 3.2 to section 3.6 are taken from the author's paper published in IEEE Journal of Solid-State Circuits in 2014 [29].)

#### 3.1 Introduction

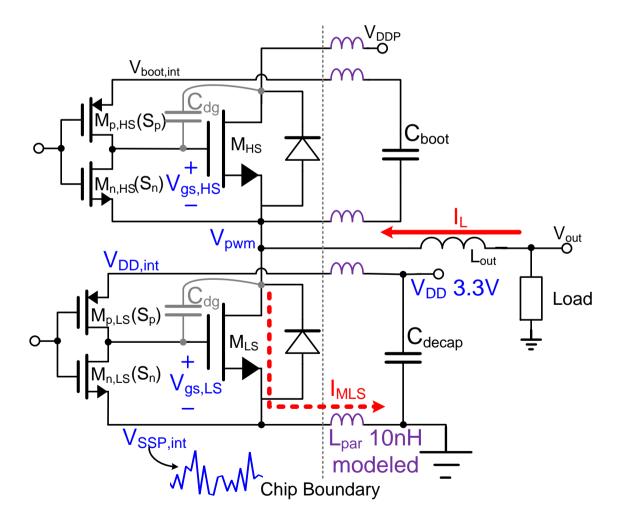

As discussed in section 2.5.1, fast switching transitions are crucial in a class-D power stage, since the V-I overlap loss dissipated in the power switches during a hard switching transition is directly proportional to the  $V_{pwm}$  transition time. Yet one significant design problem associated with a fast switching power stage is the on-chip supply bounce [8],[29]. Consequently switching speed is typically limited as to limit the on-chip supply bounce. This section will discuss the design of a power-efficient high-voltage power stage, where fast switching and the capability to handle the significant on-chip supply bounce are achieved simultaneously.

The output current switching between the high-side and low-side power switches causes a large di/dt, leading to on-chip supply bounce caused by parasitic inductances. For high-voltage DMOS output devices, the maximum allowed gate-source voltage ( $V_{gs}$ ) is the same as for normal MOS devices in the same process node and is much lower than their maximum drain-source voltage ( $V_{ds}$ ). The integration of complex signal processing functions and features on the same chip as the power blocks necessitates the power stage design in deep-submicron process nodes. However, the supply bouncing magnitude of several volts, while

not yet a problem in [8]-[14], makes the design in these smaller process nodes prone to performance degradation or even malfunction.

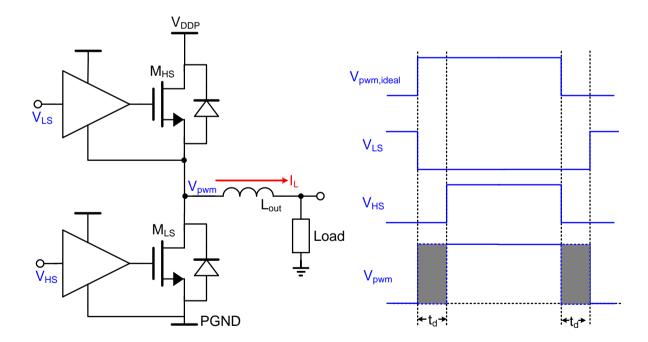

Fig. 3.1. Topology of a typical class-D power stage

In [14], parallel-connected power switches with weighted size are configured to perform staged turn-on/off for preventing inductive flyback to the supply rails. This way supply bounce can be reduced, with some tradeoff on efficiency because the turn-on of the HS and LS power switches has to be overlapped. Active clamp circuits [74] [76] can also be used as an effective way to reduce the voltage stress across the power switches and prevent damage to circuits. Yet the clamping can only mitigate power supply overshoot, while undershoot associated with the supply bounce is not clamped. In this chapter we describe a gate driver topology that overcomes the supply bouncing issue and enables a high-voltage, high-power class-D power stage design in a deep-submicron process node [29]. This is achieved by using gate drivers with on-chip regulated floating supplies, with the low-voltage driver and control circuits fully shielded from all the supply bounce. Moreover, simultaneous supply bounce

minimization and efficient switching transitions are realized by adopting an in-cycle variable gate-driving strength.

This chapter is organized as follows: in section 3.2 we show a detailed analysis of the gate driver sizing considering the on-chip supply bounce and its associated power efficiency degradation issues. The proposed floating gate driver and in-cycle variable gate-driving strength techniques for realizing efficient switching transitions are described in section 3.3. In Section 3.4 the requirement overview and circuit topology of the level shifter circuit for the class-D power stage are analyzed. Section 3.5 discusses the measurement results and in section 3.6 the conclusions of this chapter are drawn.

#### 3.2 Gate driver sizing issues

A typical class-D power stage for high-voltage high-power applications consists of two identical NDMOS devices as High Side (HS) and Low Side (LS) switches as shown in Fig. 3.1. Since for DMOS power transistors the maximum  $V_{\rm gs}$  is typically much lower than the maximum V<sub>ds</sub>, the LS gate driver is supplied by a separate low-voltage supply and externally decoupled. For the HS gate driver, an external bootstrapping capacitor can be used as the supply. Here we use the three-line earth symbol for the power ground V<sub>SSP</sub>, which is the offchip reference ground. Later in the chapter the single-line ground symbol will be adopted to represent the on-chip grounds as to distinguish them from the off-chip reference ground. The circuit parameters of this power stage used for the simulations in this chapter are summarized in TABLE IV. The switching frequency f<sub>sw</sub> is chosen at 500kHz as a typical value of class-D f<sub>sw</sub> in general [8]-[14]. For piezoelectric-actuator applications, a lower f<sub>sw</sub> can also be used if the signal bandwidth is lower. The output DC current I<sub>out</sub> is the average inductor current I<sub>L</sub> within one switching cycle. It is set at 1A with the output V<sub>pwm</sub> duty cycle being 0.5. This represents the scenario of the instant when the output stage is discharging the capacitive piezoelectric load from mid-supply. Nevertheless, the analysis itself is general and also holds for other output current and duty cycle combinations, as well as when the output stage is processing a dynamic output signal.

Fig. 3.2. Circuit diagram with combined gate driver and output power switches for analyzing class-D power stage switching dynamics

TABLE IV. SUMMARY OF THE PARAMETERS USED IN THE POWER STAGE SIMULATION

| Parameters                          | Value  |  |

|-------------------------------------|--------|--|

| Power Stage Supply VDDP             | 80V    |  |

| DMOSFET's Maximum V <sub>gs</sub>   | 3.3V   |  |

| Output Inductance Lout              | 100µH  |  |

| Switching Frequency f <sub>sw</sub> | 500kHz |  |

| Output DC Current Iout              | 1A     |  |

| V <sub>pwm</sub> Duty Cycle         | 0.5    |  |

| Dead Time t <sub>d</sub>            | 100ns  |  |

#### 3.2.1 Power Transistor Dissipation

To emphasize on evaluating the gate driver sizing influence on the switching loss, we categorize the dominating power loss in the power MOSFETs of a high-voltage Class-D output stage into three types of losses for simplicity [34]: 1)  $P_{cond}$ : conduction loss (both from  $I_{out}$  and  $I_{rip}$ , so  $P_{cond} = P_{con} + P_{Irip}$  in TABLE I on page 14) caused by the power MOSFETs'  $r_{on}$ . 2)  $P_{cap}$ : capacitive loss caused by charging and discharging parasitic capacitances on  $V_{pwm}$ ,

and 3)  $P_{sw}$ : switching losses caused by V-I overlap in the switches during switching transitions. Compared to the analysis made in Chapter 2, the gate driver loss  $P_g$  is neglected here as at most output powers it is much smaller than the three listed above. Among the three dissipation sources,  $P_{cond}$  is inversely proportional to the power transistor size S while  $P_{cap}$  is proportional to the power transistor size S. As for  $P_{sw}$ , in the optimal case (very fast switching) its dominant contribution is the intrinsic reverse-recovery current [11] and this is also proportional to the power transistor size S. The total dissipation can then be optimized by choosing the correct transistor size to balance the three power dissipation sources [34]. Under the circuit operating conditions in TABLE IV, an optimized DMOS power transistor size is derived as  $56000\mu m/0.75\mu m$ , with TABLE V listing each dissipation source and their respective contributing ratio. This optimization is considered in the ideal case, i.e. with no power supply parasitic inductances included.

Because our first attempt here is to examine what the dissipation sources should be and how they contribute to the total dissipation in the optimal case, the driver stage (Fig. 3.2) for driving the two power switches should also be designed to behave as close to ideal drivers as possible in this optimization. This has two implications 1) the drivers should turn on the power switches very fast such that the main contribution to V-I overlap is caused by the reverse-recovery current. Since we do not consider power supply parasitic inductances in this phase, the driver pull-up transistor can be increased as much as necessary to reach this minimum  $P_{sw}$ . The minimized  $P_{sw}$  is then proportional to the reverse-recovery charge in the body diode and thus proportional to the power transistor size S. 2) The driver should turn off the power switches very fast and then be able to completely keep the power switches off when required. Similarly since power supply parasitic inductances are not considered yet, the driver pull-down transistor is sized to be much larger than the pull-up transistor as to avoid cross conduction [77].

TABLE V. LIST OF EACH DISSIPATION SOURCE WITH AN OPTIMIZED POWER TRANSISTOR SIZE S OF  $56000\mu m/0.75\mu m$

| Dissipation Source          | Power Loss Type | Power Loss |     | tio   |

|-----------------------------|-----------------|------------|-----|-------|

| Total Output DMOSFETs' Loss | Balanced        | 1.2W       | 100 | 0%    |

| P <sub>cond</sub>           | ∝ 1/S           | 570mW      | 48  | %     |

| P <sub>cap</sub>            | ∝ S             | 120mW      | 10% | 52%   |

| P <sub>sw</sub>             | ∝ S             | 510mW      | 42% | J2 /0 |

However, although switching can be arbitrarily fast in this optimization procedure, in reality it will cause large di/dt, and consequently supply bounce which affects the circuit operation. In the following subsection we will show how the gate drivers influence the supply bounce (di/dt) for different switching scenarios and how efficiency deteriorates if supply bounce has to be limited by proper gate driver sizing.

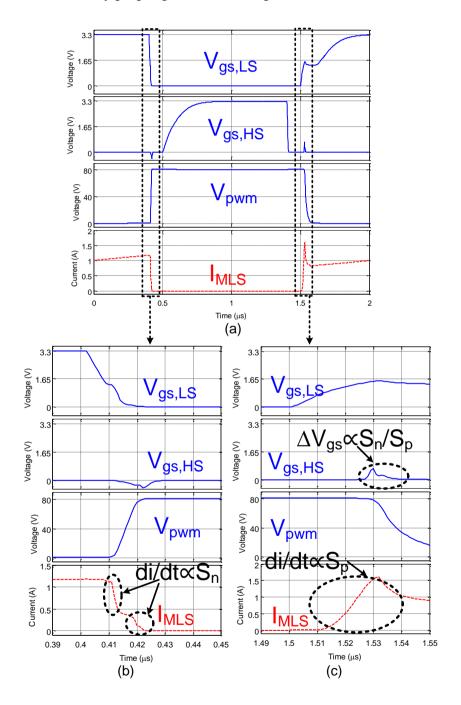

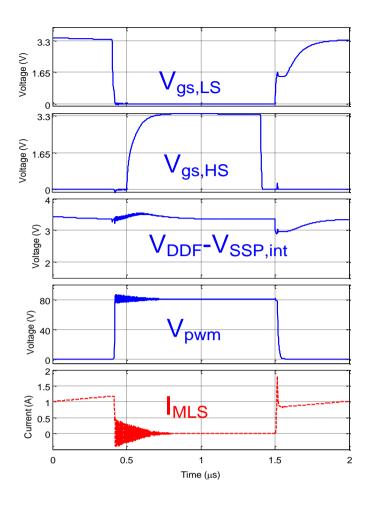

Fig. 3.3. Simulation waveforms with both  $V_{pwm}$  soft switching and hard switching transitions. (a) One complete switching cycle (b) Soft switching transition (c) Hard switching transition

#### 3.2.2 Supply Bounce Analysis and Gate Driver Sizing

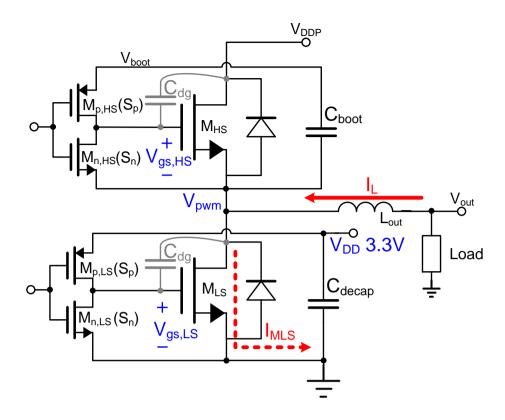

The switching behavior of a class-D output stage can be categorized into two types of switching transitions: soft switching, where  $I_L$  (dis)charges the parasitic output capacitance of the switch transistors and hard switching, where the transistors (dis)charge these parasitics [74]. Depending on the relative amplitude of the inductor ripple current and the load current,  $I_L$  can either be bidirectional with both switching transitions being soft switching or unidirectional, where one transition is soft switching and the other is hard switching. The power stage circuit diagram in Fig. 3.2 is used to illustrate the two switching transitions. The load current  $I_L$  is flowing into the power stage and keeps flowing in this direction during the full switching cycle. Fig. 3.3(a) shows the simulation waveforms in one complete switching cycle, consisting of soft and hard switching transitions while Fig. 3.3(b) and Fig. 3.3(c) shows the two edges in detail.

In Fig. 3.3(b) for the soft switching transition edge, the  $V_{pwm}$  low-to-high transition starts when  $M_{LS}$  is turning off, and  $I_L$  provides the current to charge  $V_{pwm}$  to  $V_{DDP}$  without resorting to the active devices. From the driver sizing point of view, when we look at the current flowing in  $M_{LS}$  ( $I_{MLS}$ ), first,  $I_{MLS}$  is decreased such that  $I_L$  can provide for the current necessary to charge the  $M_{LS}$  parasitic capacitances and to discharge the  $M_{HS}$  parasitic capacitances. Then there comes a period where  $V_{pwm}$  is slewing and  $I_{MLS}$  keeps nearly constant. When the slewing is over,  $I_{MLS}$  is further decreased to be conducted by the HS body diode within the dead time. During both times when  $I_{MLS}$  is decreasing, the di/dt is proportional to how fast  $M_{LS}$  is being turned off, and thus is proportional to the gate driver pull-down (PD) transistor  $M_{n,ls}$  size  $S_n$ .

For the hard switching transition as shown in Fig. 3.3(c), first  $M_{HS}$  is turned off, and the current flows through the  $M_{HS}$  back-gate diode.  $V_{pwm}$  remains high until  $M_{LS}$  has been turned on and has taken over all the load current as well as the current for discharging the  $V_{pwm}$  node. The rate at which  $I_{MLS}$  is increasing during this time is proportional to the driver pull-up (PU) transistor  $M_{p,LS}$  size  $S_p$ . After that,  $V_{pwm}$  starts slewing with a rate determined by  $C_{dg,LS}$  and the on resistance of  $M_{p,LS}$  (with size  $S_p$ ). This slewing will also cause the  $M_{HS}$  gate-source voltage to rise through  $C_{dg,HS}$  and the on resistance of  $M_{n,HS}$  (with size  $S_n$ ), so the driver PD transistor  $M_{n,HS}$  should be sized with a much lower on resistance than PU transistor  $M_{p,LS}$  to avoid cross conduction.

Because the HS and LS drivers and power switches are identical, the driver size versus di/dt analysis made above also holds for the case that the  $V_{pwm}$  high-to-low transition is soft switching while the  $V_{pwm}$  low-to-high is hard switching. The difference is that, since the HS gate driver supply is referred to  $V_{pwm}$ , the di/dt of the current flowing in  $M_{HS}$  and the subsequent supply bounce on  $V_{DDP}$  will not influence the HS gate driver supply. This will only be the case for class-D output stage topologies employing complementary output power transistors [9].

In conclusion, regarding the relationship between the gate driver sizing and the switching dynamics, 1)  $S_n$  is limited by the permissible di/dt in soft switching 2)  $S_p$  is limited by the permissible di/dt in hard switching, and 3)  $S_p/S_n << 1$  to prevent cross conduction during hard switching. From 1)-3) we further conclude that  $S_n$  in soft switching is the major concern when it comes to supply bounce.

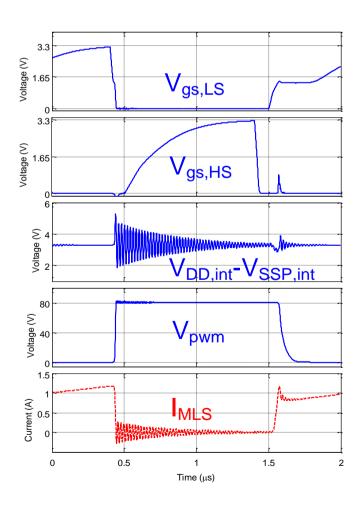

Fig. 3.4. Class-D power stage with power supply parasitic inductance included

For relating the analyzed di/dt to the on-chip supply bounce, the class-D power stage with parasitic inductances of power supply and decoupling capacitor included is shown in Fig. 3.4. The parasitic inductances consist of bond wires, lead fingers, and PCB traces between the on-chip power supply pads and the decoupling capacitors of the external power supplies, which can easily add up to tens of nano-Henrys [8]. With a modeled parasitic inductance  $L_{par}$  of 10nH, Fig. 3.5 illustrates the influence of the bounce on the power stage switching transitions with 3.3V gate driver supply. Even though in this simulation 500pF on-chip  $V_{DD}$  decoupling was added between  $V_{DD,int}$  and  $V_{SSP,int}$ , and furthermore extremely slow switching was adapted to ensure that oscillatory switching transitions [83] are overcome, 60% variation on the gate driver supply is evident with the modeled  $L_{par}$  of 10nH. The main concerns here include the robustness considerations for the low-voltage circuit blocks as well as the suboptimal switching loss  $P_{sw}$  performance. To gain insight into how efficiency gets deteriorated, the gate driver sizing procedure with constrained on-chip supply bounce is derived as follows,

Fig. 3.5. Simulation waveforms illustrating the influence of supply bouncing,  $V_{pwm}$  high-to-low transition has to be extremely slow and results in high switching loss.

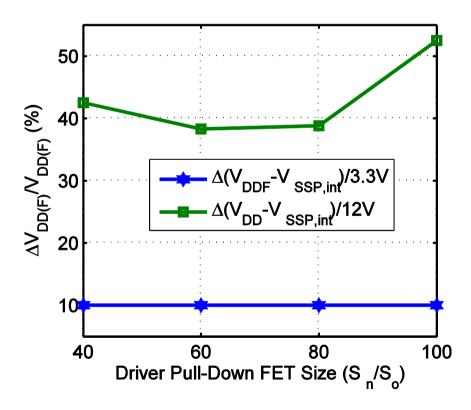

Fig. 3.6. Simulation result of different driver pull-down transistor size and the corresponding on-chip supply bouncing, under different on-chip decoupling capacitor values,  $S_n$  value is normalized to a  $S_o$  of  $3.2\mu\text{m}/0.32\mu\text{m}$ .

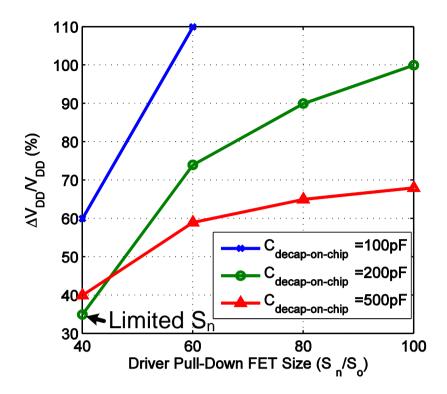

(1) Determine the driver pull-down transistor size  $S_n$ , based on the tolerable maximum gate driver supply bounce limited by soft switching transition.

Fig. 3.6 shows the simulation result of different driver pull-down transistor size and the corresponding on-chip supply bouncing, for different on-chip  $V_{DD}$  decoupling capacitor values. We see that the on-chip  $V_{DD}$  bounce increases with the driver pull-down transistor size. Also, adding more on-chip decoupling capacitor will help to decrease the bounce, but with limits. As also shown in Fig. 3.6, for a  $S_n/S_o = 40$  to limit the bounce, adding on-chip decoupling capacitor from 200pF to 500pF will not decrease the on-chip bounce anymore, primarily because the  $L_{par}$ - $C_{decap-on-chip}$  bandwidth limits the effectiveness of bounce suppression.

(2) Determine the driver pull-up transistor size  $S_p$ , limited with respect to the pull-down transistor  $S_n$  for avoiding cross conduction of the two output power DMOS switches.

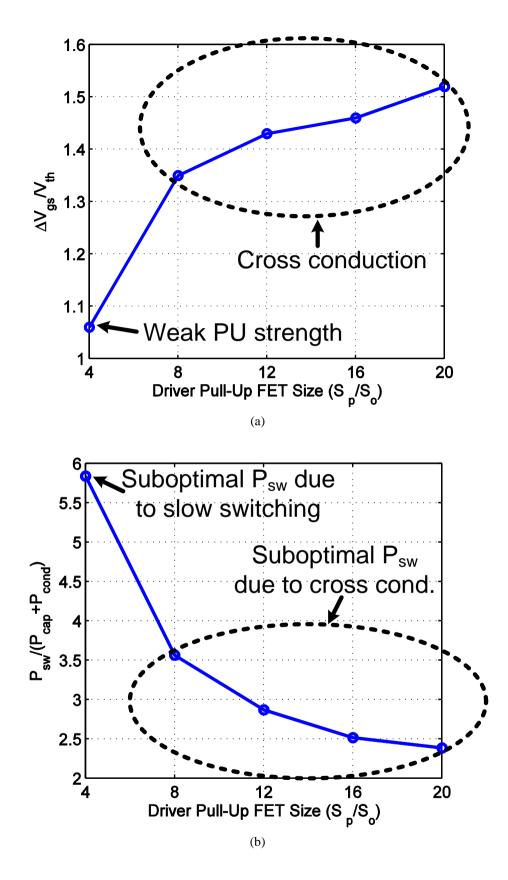

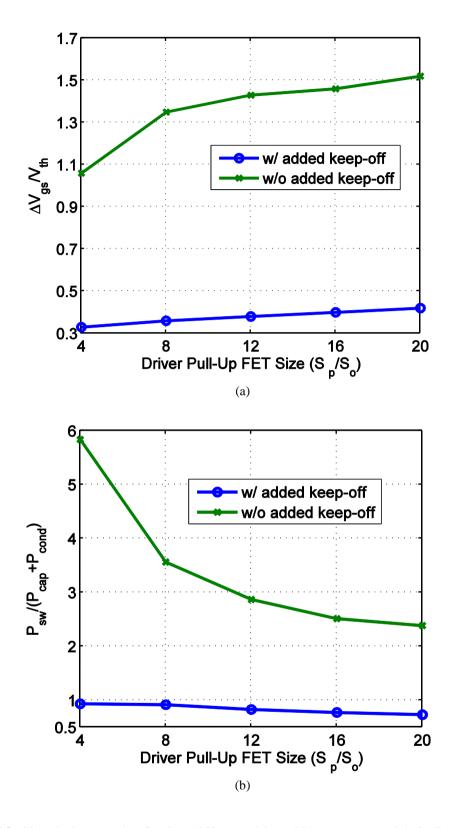

Fig. 3.7. Driver pull-up transistor sizing with  $S_n/S_o$  chosen at 40.  $S_n$  and  $S_p$  values are normalized to an  $S_o$  of  $3.2\mu m/0.32\mu m$ . (a)  $S_p$  limited for avoiding cross conduction (b) Suboptimal switching loss performance

Considering the already limited  $S_n$  for suppressing the on-chip supply bounce,  $S_p$  is further limited by the requirement to avoid cross conduction. This means that hard switching transitions have to be either extremely slow or cause cross conduction, with both cases causing suboptimal switching loss. Fig. 3.7(a) shows the  $S_p$  sizing when  $S_n/S_o$  has been chosen at 40. The efficiency degradation caused by this limitation is evident in Fig. 3.7(b).

An increase of  $S_p/S_o$  from 8 to 20 results in faster switching, which lowers  $P_{sw}$ . However, a larger  $S_p$  also results in cross conduction, adding to  $P_{sw}$ , so  $P_{sw}$  is not reduced to the optimal value compared to the other losses  $P_{cond} + P_{cap}$  (optimum ratio should be 0.72 as in TABLE V).

Since the main factor that determines the power supply bouncing during switching transitions is the driver-size-related di/dt, the analysis made above is not limited by the power transistor size chosen in TABLE V. If a different power transistor size is chosen, the driver size will have to be scaled accordingly to meet the same requirement on di/dt as well as on avoiding cross conduction. Consequently the design trade-offs for limiting the di/dt in soft switching and aiming for fast transitions in hard switching are the same. Regarding the effect of process and temperature variation on the on-chip supply bounce magnitude, the analysis of the relationship between the driver transistor size and the bounce magnitude also holds. A decrease in temperature or a fast process corner has the same effect as an increase in transistor size, which will cause more bounce. Additionally, in designs where a larger L<sub>par</sub> than the modelled 10nH exists through longer decoupling loops, e.g. larger packages than required or decoupling capacitors placed far away from the supply pins, the supply bounce magnitude will also increase.

#### 3.3 Floating gate driver design

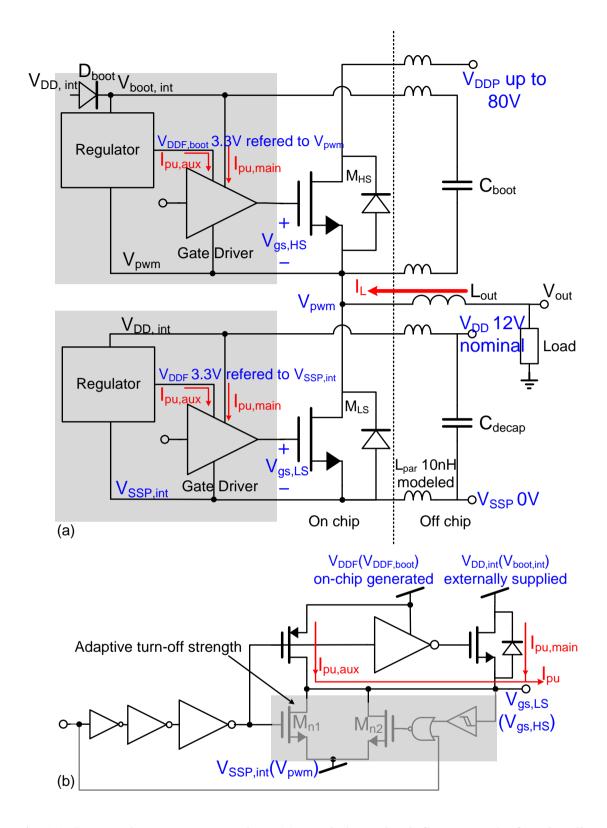

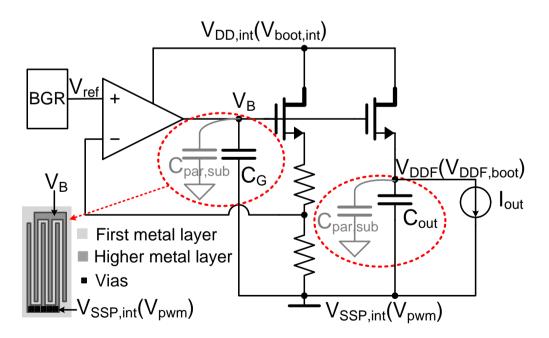

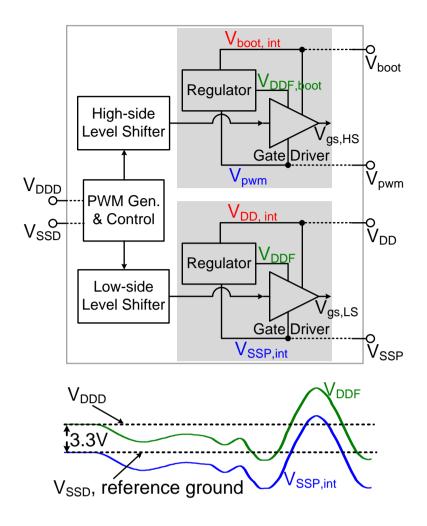

#### 3.3.1 Floating Gate Driver with Regulated Supply

To overcome the on-chip driver supply bouncing issue without sacrificing efficiency during switching transitions, we propose a gate driver topology with on-chip regulated floating supply. As shown in Fig. 3.8(a), two on-chip voltage regulators are used to provide stable on-chip supply voltages to the gate driver circuits. The two regulators track the two reference nodes  $V_{SSP,int}$  and  $V_{pwm}$  respectively, so the on-chip bouncing will not be seen by

the driver circuits. The unregulated input supply voltage for the regulators are chosen based on the estimated maximum bouncing magnitude plus the minimum operation voltage of the regulator circuits (12V unregulated  $V_{DD}$  is used here). The detailed gate driver circuit is shown in Fig. 3.8(b). The pull-up current has been divided into two parts. The main  $I_{pu}$  is supplied by the unregulated  $V_{DD}$  while an auxiliary  $I_{pu}$  is used to turn the output power transistor fully on. By this configuration the regulators are not required to supply the hundreds of milliamps for  $I_{pu}$  and their design can be simplified. For the pull-down current path, an in-cycle variable gate driving strength is implemented and will be explained next.

#### 3.3.2 In-Cycle Variable Gate-Driving Strength

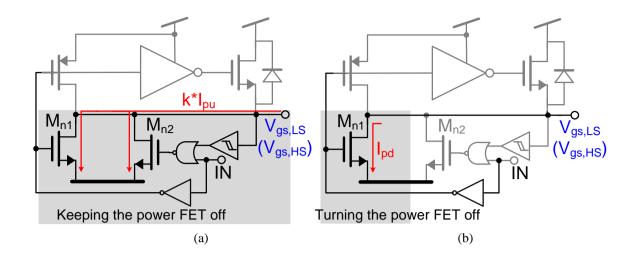

As explained in the previous section, the main reason for excessive switching loss during hard switching is because the driver PU transistor has to be much weaker than the PD transistor, other than limited by on-chip bounce considerations. To circumvent this limitation of the driver PU strength, we propose to a use an in-cycle variable gate-driving strength [11]. As shown in Fig. 3.9(a), when the driver input and output status have both been detected as already off, the combined strength of M<sub>n1</sub> and M<sub>n2</sub> will be used to keep the power transistor off when the other driver is turning on based on the  $S_p/S_n$  driver ratio requirement. However, when the driver is in the process of turning its output off and hasn't yet reached the level determined by the Schmitt trigger, only the weaker M<sub>n1</sub> will provide the pull-down current to turn off the output power transistor slowly in order to keep di/dt low (Fig. 3.9(b)). This way we have the design freedom to both choose the correct  $S_p/S_n$  ratio to avoid cross conduction, and limit the on-chip supply bounce. Simulation waveforms for comparing the effectiveness with and without the adaptive driver turn-off strength are shown in Fig. 3.10, with the modeled L<sub>par</sub> of 10nH in the simulation. Fig. 3.10(a) shows that the same effect for keeping the power transistor off is obtained while Fig. 3.10(b) illustrates that the supply bouncing is significantly reduced when a weaker PD strength can be applied for turning the power transistor off. Fig. 3.10(a) and Fig. 3.10(b) are enlarged simulation waveforms within one switching period.

Fig. 3.8. Proposed power stage topology (a) supply bouncing influence on the functionality of the gate driver is eliminated by the on-chip regulated gate-driver supply (b) Detailed gate driver structure.

Fig. 3.9. Gate driver with adaptive turn-off strength (a) Stronger pull-down transistors for keeping the power transistor off (b) Weaker pull-down transistors for turning the power transistor off

Fig. 3.10. Simulation waveforms for the on-chip supply bouncing with and without the adaptive turn-off strength within one switching cycle (a) When one power transistor turns on, the other power transistor can be kept off (b) On-chip supply bouncing can be significantly reduced.

#### 3.3.3 Sizing of the Floating Gate Drivers

Compared with the sizing of the gate driver with externally decoupled low-voltage gate driver supply, the sizing of the floating gate driver combined with the variable gate-driving strength can now have the following advantages:

(1) The gate driver PD transistor can be sized larger, since the floating gate drivers can sustain a much higher on-chip supply bouncing amplitude and the floating regulated driver supplies will not be directly influenced.

As can be seen in Fig. 3.11, although the off-chip decoupled 12V supply still has large variations during switching, the on-chip floating supply varies only 10% with the adopted floating regulator circuit discussed in section 3.3.4. This variation is mainly due to the load regulation of the regulator for providing the PU current. Also, this clean gate driver supply is achieved without using area-consuming on-chip decoupling capacitors in the hundred pF range.

Fig. 3.11. Simulation result of the on-chip floating gate driver supply variation with respect to different gate PD strengths.  $S_n$  value is normalized to a  $S_0$  of  $3.2\mu m/0.32\mu m$ .

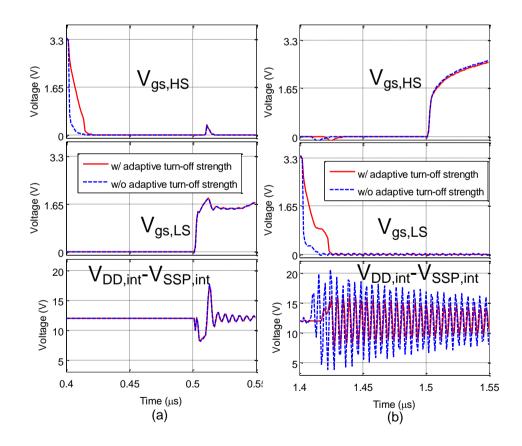

Fig. 3.12. Simulation result of using different driver PU strengths, with  $S_n/S_o$  chosen at 40.  $S_n$  and  $S_p$  values are normalized to a  $S_o$  of  $3.2\mu m/0.32\mu m$ . (a) Cross conduction is prevented by adding additional keep-off strength of  $4xS_n$ . (b) Fast hard switching transitions are realized with much smaller switching loss compared with the case using off-chip decoupled 3.3V gate driver supply

(2) The PU transistor can be sized larger to improve efficiency without getting limited by the maximum  $S_p/S_n$  ratio. Cross condition is avoided by the additional keep-off strength.

In Fig. 3.12(a) we see the effect of added keep-off strength to the PU transistor sizing. With the same  $S_n/S_o$ =40 as used in section 3.2 for limited bounce, 4x added keep-off strength can ensure that  $\Delta V_{gs}$  is far below  $V_{th}$  when choosing  $S_p/S_o$  up to 20. Fig. 3.12(b) shows that efficient hard switching transitions can be realized since now larger PU transistor size can be adopted. With  $S_p/S_o$  set to 20, the  $P_{sw}/(P_{con}+P_{cap})$  ratio is now 0.73, close to the minimized  $P_{sw}/(P_{con}+P_{cap})$  ratio of 0.72 in TABLE V.

#### 3.3.4 On-chip Floating Voltage Regulator

The on-chip floating regulator circuit for both HS and LS is shown in Fig. 3.13. For fast response and low output voltage ripple, the output  $V_{DDF}/V_{DDF,boot}$  has been excluded from the feedback loop [87]. The drawback on precision is not critical here since the regulator supplies mainly digital blocks. The output devices of the regulator are also DMOS devices to sustain the higher 12V unregulated  $V_{DD}$  as well as the bouncing superimposed on it.

Fig. 3.13. On-chip regulator and its decoupling capacitor C<sub>G</sub> implementation

Fig. 3.14. Simulation waveforms of the power stage in Fig. 3.8, V<sub>pwm</sub> high-to-low transition is fast, without disturbing the on-chip floating driver supply.

On-chip decoupling capacitor  $C_G$  is important for power supply ripple rejection. It is vital to minimize its parasitic capacitance  $C_{par,sub}$  to the substrate as any disturbance from the  $V_{SSP,int}/V_{pwm}$  node will be coupled to  $V_B$  by a ratio  $C_{par,sub}/(C_G+C_{par,sub})$ . As an example, the output voltage  $V_{PWM}$  slews 80V in a few nanoseconds; even with 1% parasitic capacitance 0.8V will be coupled to the 3.3V output, which is an unacceptable 25% variation. Consequently it is rather important that these decoupling capacitors are fully shielded from the substrate as shown in Fig. 3.13. Here for the metal fringe capacitor the whole first metal plate is connected to the  $V_{SSP,int}/V_{pwm}$  node such that  $V_B$  is fully shielded. The output decoupling capacitor  $C_{out}$  has a value of 20pF, which is much more area efficient than the decoupling capacitor of an unregulated gate-driver supply (Fig. 3.6).

Efficient switching transitions as shown in Fig. 3.14 are achieved by this gate driver topology. The on-chip floating regulators provide a reliable 3.3V supply to the gate driver circuit during both soft- and hard-switching transients. Also, thanks to the in-cycle variable

gate-driving strength, the high-to-low hard switching here is performed fast, simultaneously avoiding cross conduction and excessive bounce on the off-chip decoupled 12V supply (Fig. 3.10).

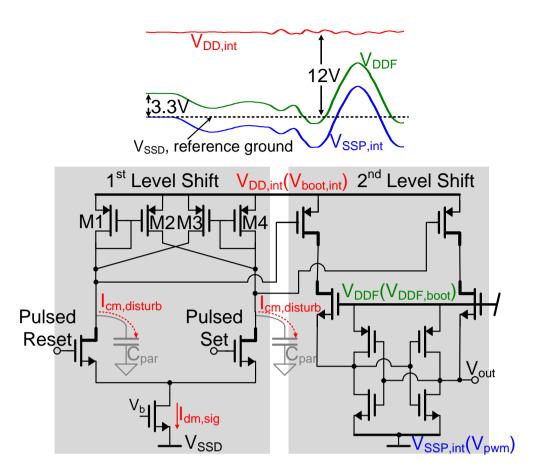

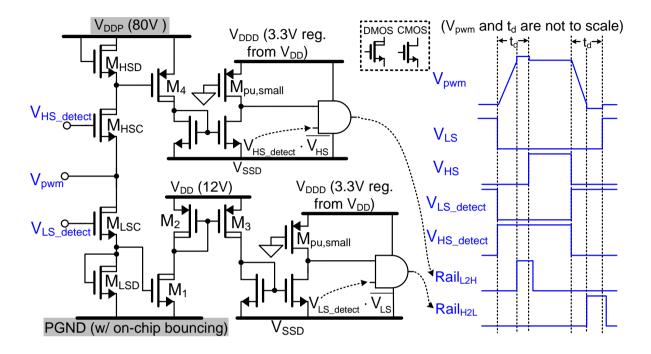

#### 3.4 Power-Efficient 2-step level shifter

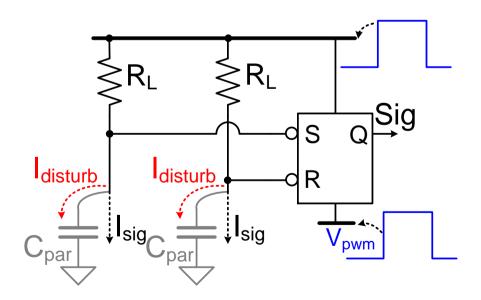

Another important circuit block for the class-D power stage is the level shifter circuit [79]-[82]. It is used for communication between signals referred to the digital ground  $V_{SSD}$  and those referred to the power ground  $V_{SSP,int}$  or the floating HS  $V_{pwm}$ , as shown in Fig. 3.15. With a 3.3V supply for both the low-voltage control blocks and the gate drivers, the on-chip supply bouncing magnitude higher than the 3.3V supply itself presents a challenge for reliable level shifting. As shown in Fig. 3.15, the >3.3V bounce causes the voltage potential between  $V_{DDF}$  and  $V_{SSD}$  to be very uncertain. This makes conventional level shifting by building a direct interface circuit using  $V_{DDF}$  and  $V_{SSD}$  as power and ground [8], [79], [80] not feasible. For reliable level shifting, a two-step approach has been adopted here, where the voltage level is first referred to the higher 12V  $V_{DD,int}$  and then to  $V_{SSP,int}$ .

In addition, compared to level shifters used for transferring to voltage levels referred to fixed supply rails [9], [81], [82], level shifting to the slewing  $V_{pwm}$  is associated with disturbance that could corrupt the transferred signal. We consider the SR latch referred to the  $V_{pwm}$  voltage domain as shown in Fig. 3.16. The supply rail referred to  $V_{pwm}$  has the same high slew rate as  $V_{pwm}$  (up to  $10kV/\mu s$  in this design). If there exist parasitic capacitances e.g. to the substrate at the input of the latch, and the stage preceding the latch has a resistive load, this directly translates to a common-mode disturbance for the latch and a possible logic output error can occur.

Fig. 3.15. Illustration of the communication between different voltage domains by the level shifter

Fig. 3.16. Slewing for the voltage levels referred to  $V_{\text{pwm}}$  can cause error output of the level shifter

Fig. 3.17. Level shifter circuit and illustration of the on-chip supply/ground waveforms which necessitates a 2-step approach for the level shifting

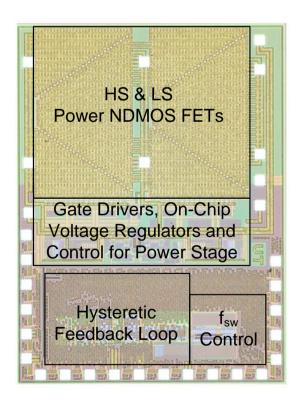

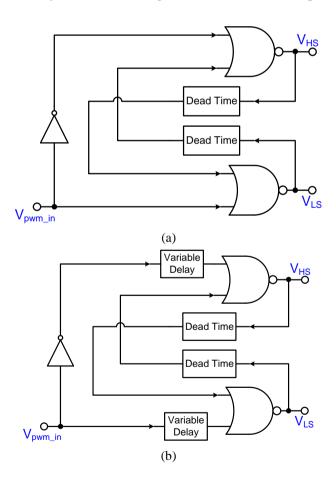

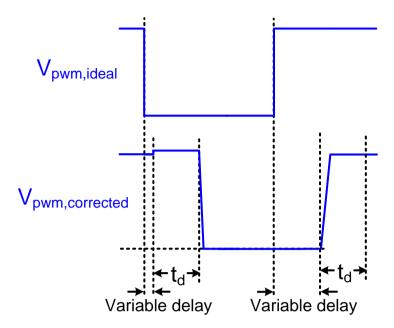

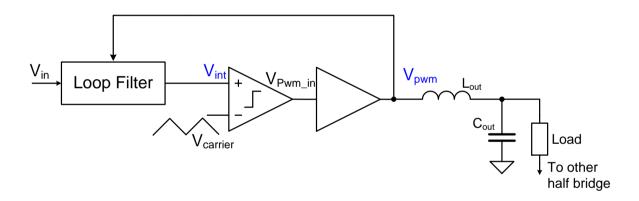

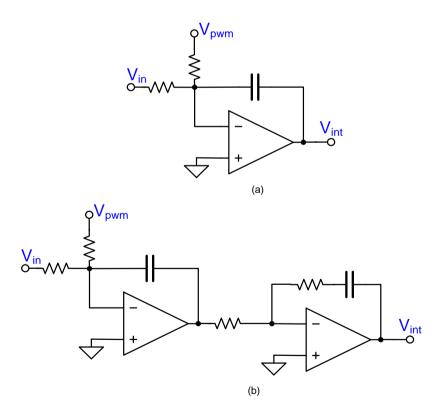

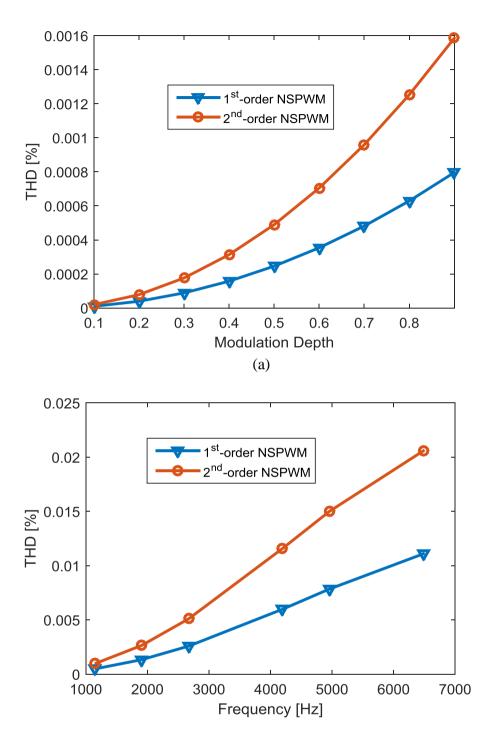

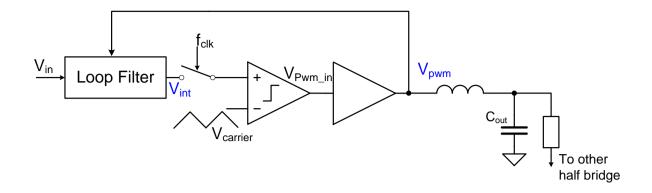

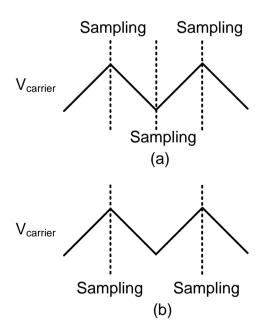

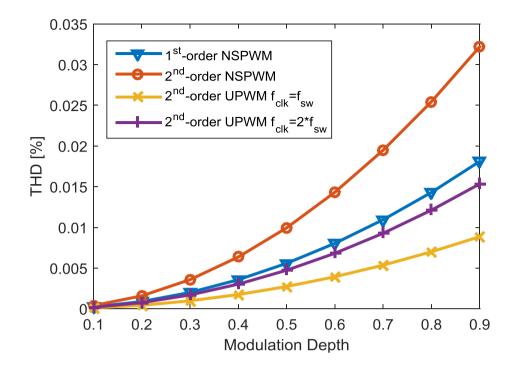

To cope with the >3.3V supply bounce, the two-step level shifting approach is shown in the circuit schematic in Fig. 3.17, where the voltage level is first referred to the higher 12V  $V_{DD,int}$  and then to  $V_{SSP,int}$ . As shown in Fig. 3.17, the already available 12V  $V_{DD,int}$  referred to  $V_{SSD}$  is not influenced too much by the bounce and thus establishing a reliable interface circuit across  $V_{DD,int}$  and  $V_{SSD}$  as the 1<sup>st</sup> level shifting step. Subsequently the 2<sup>nd</sup> level shifting transfers the signal to the one referred to  $V_{SSP,int}$ , tolerating the supply voltage variation between  $V_{DD,int}$  and  $V_{SSP,int}$ .