**GREEN CONTRACTOR** Efficient Energy Management of Multiprocessor Streaming Applications via Model Checking Waheed Ahmad

# Green Computing: Efficient Energy Management of Multiprocessor Streaming Applications via Model Checking

Waheed Ahmad

Graduation committee:

Chairman: Promotor: Co-promotor:

Members: Prof. dr. ir. B.R.H.M. Haverkort Dr. ir. J.F. Broenink Prof. dr. K.G.W. Goossens Prof. dr. W. Yi Dr. ir. P.K.F. Hölzenspies Prof. dr. P.M.G. Apers Prof. dr. J.C. van de Pol Dr. M.I.A. Stoelinga

University of Twente University of Twente Eindhoven University of Technology Uppsala University Facebook, London

CTIT Ph.D. Thesis Series No. 16-418Centre for Telematics and Information TechnologyUniversity of Twente, The NetherlandsP.O. Box 217 – 7500 AE Enschede

#### IPA Dissertation Series No. 2017-02

The work in this thesis has been carried out under the auspices of the research school IPA (Institute for Programming research and Algorithmics).

The work in this thesis is conducted within Self Energy-Supporting Autonomous Computation (SENSATION) project (318490) supported by European Commission.

ISBN 978-90-365-4290-6 ISSN 1381-3617 (CTIT Ph.D. Thesis Series No. 16-418) Available online at https://doi.org/10.3990/1.9789036542906

Typeset with IAT<sub>E</sub>X Printed by Ipskamp Drukkers Cover design © by Annelien Dam Copyright © 2017 Waheed Ahmad, Enschede, The Netherlands

# GREEN COMPUTING: EFFICIENT ENERGY MANAGEMENT OF MULTIPROCESSOR STREAMING APPLICATIONS VIA MODEL CHECKING

DISSERTATION

to obtain

the degree of doctor at the University of Twente, on the authority of the rector magnificus, Prof. dr. T.T.M. Palstra, on account of the decision of the graduation committee, to be publicly defended on Thursday, April 13th, 2017 at 12:45 hrs.

by

Waheed Ahmad

born on 4 July 1987 in Lahore, Pakistan This dissertation has been approved by:

Prof. dr. J.C. van de Pol (promotor) Dr. M.I.A. Stoelinga (co-promotor) To Prof. dr. Abdus Salam (in memoriam) Nobel Laureate in Physics 1979

# Acknowledgements

I still remember when I came to Enschede for the PhD position interview, four and half years ago. With a background in electronics engineering and knowing little of the field of formal methods, I was a bit nervous. At the end of the interview, after some discussion between Jaco and Mariëlle, I was offered this position, for which I am really thankful. In other words, thank you for offering four wonderful and unforgettable years.

Jaco, in your role as a promotor, you had a big part in shaping my academic skills. Your eye for technical details spotted the mistakes that I may have otherwise missed. Your rigorous mathematical analysis and insights during meetings and lunch talks helped me later in formulating the problem statements of papers in a clear and concise way. I was mostly impressed by your ability to grasp new ideas and concepts in a short space of time. For our ISoLA paper, you learned the whole concept of controller synthesis using UPPAAL STRATEGO in a short time, while it took me so long. Same was the reason for asking your help in finishing Chapter 8. I was also impressed by your planning skills. During the SENSATION project, your insistence on planning everything ahead helped in delivering all deliverables in a timely fashion.

Mariëlle, as my daily supervisor, I have learned the most from you. I have not seen/heard any other researcher who is so good at scientific writing. You always taught me to have clean theory, and to use simple and concise structures. I always used to think that you were better suited to being a journalist than a researcher. I also learned from you the importance of building a bridge between research and its impact on society. As my boss, you gave me complete freedom to work on my own ideas, which will help me to be an independent researcher in the long run. You are full of energy all the time. Besides your super busy schedule, it's unbelievable how you make time for your kids and family and take care of them. My deepest gratitude to you and Jaco for supporting me in the best possible way, when my daughter was in the hospital. Thank you for facilitating what turned out to be the most difficult period of my life to a great extent. Hartelijk bedankt.

In addition to my supervisors, I would also like to thank Robert de Groote for helping me to understand the vast jungle of dataflow. Thank you for your support and collaboration on our ACSD'14 paper, even though you are not a big fan of model checking. I would also like to thank Philip Hölzenspies for taking interest in my work. Your keenness to learn new concepts and ideas always inspired me. Your areas of speciality range from computer architectures and dataflow applications, to programming languages and model checking, and working and collaborating with you allowed me to acquire some taste of these areas. You are a genuine all-rounder (in cricket terms).

An important part of my PhD experience consisted of my stay in the Formal Methods and Tools (FMT) group. Thank you for being there, for having cosy chats in Rappa, and organising movie nights and of course trainings for the Batavierenrace. Big thank you to Stefano for giving feedback on my thesis, and being my paranymph. Thank you Bugra for introducing me to the world of model-driven engineering, and giving me a place to stay during the last two months of my PhD. I will always remember our trip to Italy. Thanks to Rajesh for always willing to chat on any topic. Last but not least, my heartfelt thanks to Joke and Ida, for always lending a helping hand and taking care of administrative tasks. You are truly a blessing for FMT.

I thank the members of my committee for approving my thesis and providing helpful comments. I also thank Timon ter Braak and Kim Sunesen from Recore Systems, for providing the case study and helping with analysis.

Next, I would like to thank my friends in Enschede, especially my friends from the Pakistani Student Association. Thank you for organising great events throughout the year, in particular Basant, which always made Enschede feel like home to me.

I thank my parents and siblings for their love and support over the years to chase and achieve my dreams. I thank my father -my first teacher- for cultivating my love for science and books. I also thank my mother for teaching diligence, endurance and patience. I would also convey my deepest thanks to my in-laws for their unconditional love and support.

I saved the best for my wife, Friha. Thank you for putting up with me over the past few months when I was often busy. Thank you for taking care of me during the strenuous process of writing the thesis. Luckily, we had the opportunity to spend some amazing time together. In particular, our unforgettable trips to Tunisia, Spain, Portugal and Greece. And not to forget our daughter Sabika Noor Aulakh! Thank you for bringing colours in our lives.

Nuenen March 2017

# Abstract

ONSUMER electronics such as televisions, telephones, and computers have become an essential part of a human life. An important subclass of consumer electronics termed *embedded multimedia systems* deal with applications from the multimedia and Digital Signal Processing (DSP) domain executing on multiprocessors. Such applications repetitively process an input stream of indefinite length, for example a video decoder that decodes a video stream. These applications are often referred to as *streaming applications* in literature. Examples of embedded multimedia systems are mobile phones, virtual reality gaming consoles, 3D-enabled televisions, and car navigation systems. The Synchronous Dataflow (SDF) model of computation naturally captures the characteristics of streaming applications and allows design-time analysis of timing and resource utilisation.

Embedded multimedia systems have evolved significantly in recent decades, and are becoming ubiquitous in our daily lives. This trend is also giving rise to challenges such as (1) increasing energy demand leading to global warming, (2) requirement of seamless and robust performance, and (3) growing complexity of embedded multimedia systems resulting in higher development cost and longer time-to-market.

To address these challenges, we introduce several methods that combine resource and power management with scheduling decisions. As an analysis environment, we consider model checking because of its ability to generate optimal traces (schedules).

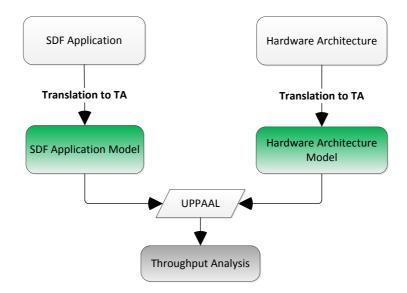

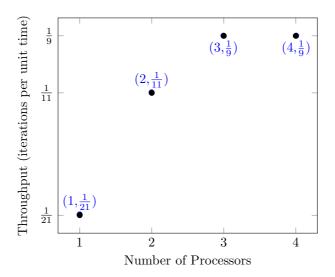

The first approach is *throughput-optimal* scheduling of SDF graphs on a given number of processors via the proven formalism of timed automata. In this work, SDF graphs along with hardware platforms are translated compositionally to timed automata. The problem of throughput optimisation is encoded as a query over timed automata. The model checker UPPAAL extracts a trace representing a throughput-optimal schedule. In this way, we can efficiently determine a trade-off between number of processors and throughput for a certain streaming application.

The second approach generates *energy-optimal* schedules of SDF graphs. The hardware architecture is decorated with novel energy management techniques like dynamic power management (DPM, switching to low power state) and dynamic voltage and frequency scaling (DVFS, throttling processor frequency). To balance flexibility and design complexity, the concept of Voltage and Frequency Islands (VFIs) is considered. It achieves fine-grained system-level power management,

by operating all processors in the same VFI at a common frequency/voltage.

In this work, we utilise priced timed automata, a model checking formalism that extends timed automata with costs, which are used to model the power consumption of processors. After SDF graphs and hardware platforms are translated to priced timed automata, the model checker UPPAAL CORA generates a trace representing an energy-optimal schedule. We demonstrate that the combination of DPM and DVFS provides an energy reduction beyond considering DVFS or DPM separately. Moreover, we show that by clustering processors in VFIs, DPM can be combined with any granularity of DVFS.

The third approach derives the Quality of Service of SDF graphs mapped on hardware platforms powered by multiple batteries. In this approach, we use hybrid automata which are an extension of timed automata with continuous variables. Furthermore, using the model checker UPPAAL SMC, we evaluate (1) system lifetime, and (2) minimum required initial battery capacities to achieve the desired application performance.

In today's agile world, there is a fierce competition that requires low development cost and short time-to-market. To achieve this purpose, an efficient modelling approach is needed which can provide modularity, extensibility and interoperability. We have developed a Model-Driven Engineering (MDE) based framework which fulfils these requirements. In this framework, we introduce the so-called *metamodels* for SDF graphs and hardware platforms. The SDF graphs and hardware platforms are translated to the model-checking domain automatically using *model transformations*.

Finally, we evaluate the performance of our approach of throughput analysis by applying it in an industrial case study of face recognition systems provided by Recore Systems, Netherlands. With this case study, the performance of our approach is validated in realistic scenarios and, thus, the problem is shown to be solvable with acceptable concessions.

# Table of Contents

# Abstract

$\mathbf{2}$

## $\mathbf{i}\mathbf{x}$

| 1 | Introduction 1 |                                               |  |  |  |

|---|----------------|-----------------------------------------------|--|--|--|

|   | 1.1            | Challenges: A Societal Perspective            |  |  |  |

|   | 1.2            | Challenges: A Consumer Perspective            |  |  |  |

|   |                | 1.2.1 Longer System Lifetime                  |  |  |  |

|   |                | 1.2.2 Robust Performance                      |  |  |  |

|   | 1.3            | Challenges: An Industry Perspective           |  |  |  |

|   | 1.4            | Problem Statement                             |  |  |  |

|   | 1.5            | Proposed Approach                             |  |  |  |

|   |                | 1.5.1 Synchronous Dataflow                    |  |  |  |

|   |                | 1.5.2 Hardware Platform Model                 |  |  |  |

|   |                | 1.5.3 Model Checking                          |  |  |  |

|   |                | 1.5.4 Model-Driven Engineering                |  |  |  |

|   | 1.6            | Thesis Structure                              |  |  |  |

|   |                | 1.6.1 Thesis Overview                         |  |  |  |

|   |                | 1.6.2 Contributions                           |  |  |  |

|   |                | 1.6.3 Contents and Origins of the Chapters 16 |  |  |  |

|   | 1.7            | Conclusions                                   |  |  |  |

|   |                |                                               |  |  |  |

| Ι | Ba             | ckground 19                                   |  |  |  |

| Dataflow Preliminaries 21 |                             |                                 |    |  |  |

|---------------------------|-----------------------------|---------------------------------|----|--|--|

| 2.1                       | Synchronous Dataflow Models |                                 |    |  |  |

| 2.2                       | Semar                       | ntics of SDF Graphs             | 24 |  |  |

|                           | 2.2.1                       | States                          | 24 |  |  |

|                           | 2.2.2                       | Auto-concurrency and Self-loops | 24 |  |  |

|                           | 2.2.3                       | Transitions                     | 25 |  |  |

|   |     | 2.2.4           | Execution $\ldots \ldots 26$                                                       | 3 |

|---|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   |     | 2.2.5           | Deadlock                                                                                                                                          | 3 |

|   |     | 2.2.6           | Consistency                                                                                                                                       | 7 |

|   | 2.3 | Model           | ling Channel Capacities                                                                                                                           | ) |

|   | 2.4 | Throu           | ghput Analysis of SDF Graphs                                                                                                                      | ) |

|   |     | 2.4.1           | Self-timed Execution                                                                                                                              | L |

|   | 2.5 | $SDF^3$ :       | Synchronous Dataflow Analysis Tool                                                                                                                | 3 |

|   |     | 2.5.1           | Layout of $SDF^3$ XML                                                                                                                             | 1 |

|   |     | 2.5.2           | Analysis Algorithms of $SDF^3$                                                                                                                    | 3 |

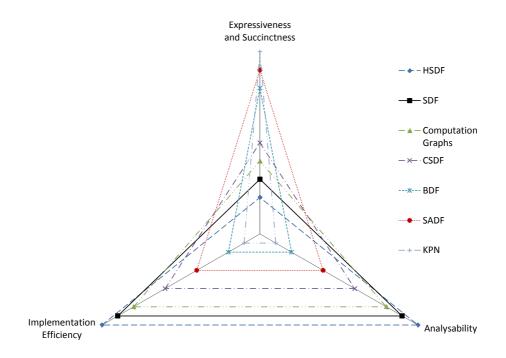

|   | 2.6 | Compa           | arison of Dataflow Models                                                                                                                         | 3 |

|   |     | 2.6.1           | Models of Computation dating to SDF Graphs 38                                                                                                     | 3 |

|   |     | 2.6.2           | Models of Computation extending SDF Graphs 39                                                                                                     | ) |

|   | 2.7 | Case S          | Studies                                                                                                                                           | ) |

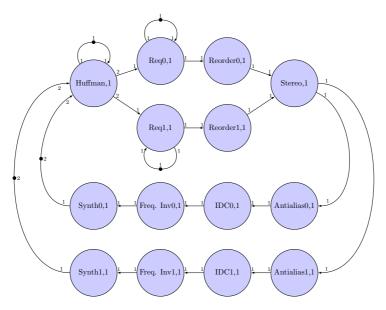

|   |     | 2.7.1           | MPEG-4 Decoder 40                                                                                                                                 | ) |

|   |     | 2.7.2           | MP3 Decoder                                                                                                                                       | L |

|   |     | 2.7.3           | MP3 Playback Application 42                                                                                                                       | 2 |

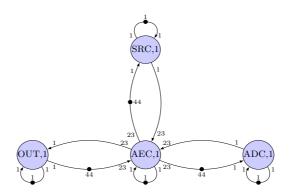

|   |     | 2.7.4           | Audio Echo Canceller                                                                                                                              | 3 |

|   |     | 2.7.5           | Bipartite Graph 44                                                                                                                                | 1 |

|   | 2.8 | Conclu          | $1sions \dots \dots$                        | 1 |

| 3 | Moo | del Ch          | ecking of Timed and Hybrid Automata 45                                                                                                            | 5 |

|   | 3.1 | Model           | Checking                                                                                                                                          | 3 |

|   |     | 3.1.1           | Temporal Logics for Model Checking                                                                                                                | 3 |

|   |     | 3.1.2           | Quantitative Model Checking                                                                                                                       | 7 |

|   | 3.2 | Timed           | l Automata                                                                                                                                        | ) |

|   |     | 3.2.1           | Definition                                                                                                                                        | ) |

|   |     | 3.2.2           | Semantics                                                                                                                                         | ) |

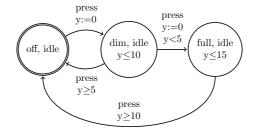

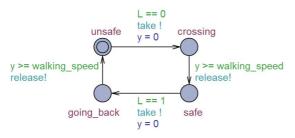

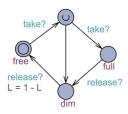

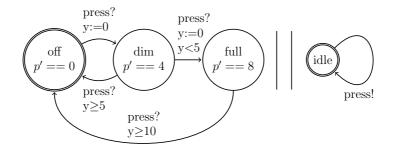

|   |     | 3.2.3           | Timed Automata in UPPAAL 52                                                                                                                       | 2 |

|   | 3.3 | Priced          | Timed Automata $\ldots \ldots 56$                                           | 3 |

|   |     | 3.3.1           | Definition $\ldots \ldots \ldots$ | 3 |

|   |     | 3.3.2           | Semantics                                                                                                                                         | 7 |

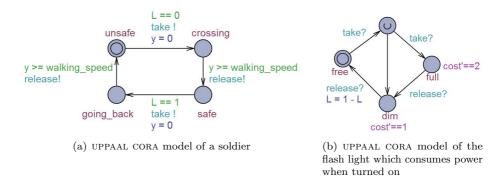

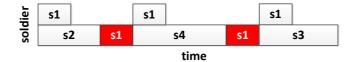

|   |     | 3.3.3           | Priced Timed Automata in UPPAAL CORA                                                                                                              | ) |

|   |     | 0.0.0           |                                                                                                                                                   |   |

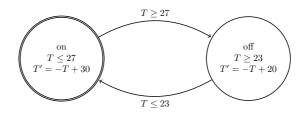

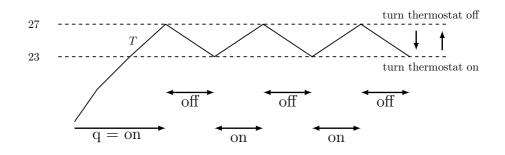

|   | 3.4 |                 | d Automata                                                                                                                                        | ) |

|   | 3.4 |                 | d Automata                                                                                                                                        | - |

|   | 3.4 | Hybrid          |                                                                                                                                                   | ) |

|   | 3.4 | Hybrid<br>3.4.1 | Definition                                                                                                                                        | 2 |

| Π | $\mathbf{S}$ | chedu  | lling and Analysis                                       | 67   |

|---|--------------|--------|----------------------------------------------------------|------|

| 4 | Res          | ource- | Constrained Scheduling                                   | 69   |

|   | 4.1          | Introd | luction                                                  | 70   |

|   | 4.2          | Relate | ed Work                                                  | 71   |

|   | 4.3          | SDF 0  | Graphs with Resource Constraints                         | 72   |

|   |              | 4.3.1  | SDF Graphs                                               | 72   |

|   |              | 4.3.2  | Platform Application Models                              | 72   |

|   |              | 4.3.3  | Example of SDF Graphs with Resource Constraints $\ldots$ | 73   |

|   |              | 4.3.4  | Semantics of SDF Graphs with Resource Constraints        | 74   |

|   | 4.4          | Throu  | ghput Analysis of SDF Graphs with Resource Constraints   | 76   |

|   | 4.5          | From   | SDF Graphs and Platform Application Models to Timed      |      |

|   |              | Autor  | nata                                                     | 80   |

|   |              | 4.5.1  | Translation of SDF Graphs and PAMs to Timed Automata     | n 80 |

|   |              | 4.5.2  | Modelling SDF Graphs and PAMs in UPPAAL                  | 82   |

|   | 4.6          | Resou  | rce-Constrained Scheduling of SDF Graphs using UPPAAL .  | 83   |

|   |              | 4.6.1  | Throughput Calculation                                   | 83   |

|   |              | 4.6.2  | Scheduling in a Heterogeneous System                     | 87   |

|   | 4.7          | Case S | Studies                                                  | 89   |

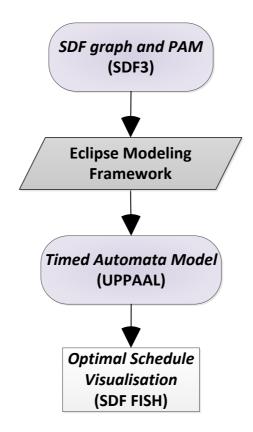

|   | 4.8          | Tool S | Support                                                  | 90   |

|   |              | 4.8.1  | Input                                                    | 90   |

|   |              | 4.8.2  | Transforming $\mathrm{SDF}^3$ Models to UPPAAL Models    | 91   |

|   |              | 4.8.3  | Output                                                   | 92   |

|   | 4.9          | Concl  | usions                                                   | 93   |

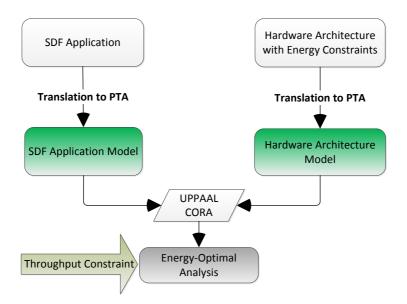

| 5 | Gre          | en Co  | mputing: Energy-Optimal Scheduling                       | 95   |

|   | 5.1          |        |                                                          | 96   |

|   | 5.2          | Relate | ed Work                                                  | 99   |

|   | 5.3          |        |                                                          | 100  |

|   | 5.4          | SDF (  | Graphs with Energy Constraints                           | 101  |

|   |              | 5.4.1  | SDF Graphs                                               |      |

|   |              | 5.4.2  | Platform Application Models                              | 102  |

|   |              | 5.4.3  |                                                          | 103  |

|   |              | 5.4.4  | Semantics of SDF Graphs with Energy Constraints          |      |

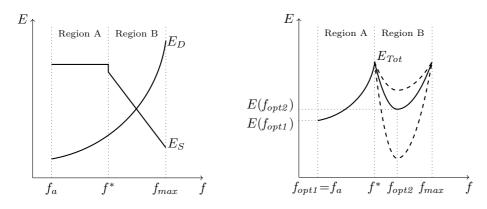

|   | 5.5          | Comp   | arison of Energy Optimisation Methods                    |      |

|   | 5.6          | -      | SDF Graphs and Platform Application Models to Priced     |      |

|   |              |        | l Automata                                               | 111  |

|   | 5.7          |        | y Optimisation of SDF Graphs using UPPAAL CORA           |      |

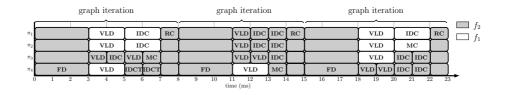

|   | 5.8        | Experimental Evaluation via MPEG-4 Decoder                                                                                                      |

|---|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|   |            | 5.8.1 Fixed Number of Processors                                                                                                                |

|   |            | 5.8.2 Varying Number of Processors                                                                                                              |

|   |            | 5.8.3 Quantitative Analysis $\dots \dots \dots$ |

|   | 5.9        | Other Case Studies                                                                                                                              |

|   | 5.10       | Tool Support                                                                                                                                    |

|   |            | 5.10.1 Input                                                                                                                                    |

|   |            | 5.10.2 Transforming Models to UPPAAL CORA Models 124                                                                                            |

|   |            | 5.10.3 Output                                                                                                                                   |

|   | 5.11       | Conclusions                                                                                                                                     |

| 6 | Mod        | del Checking and Evaluating QoS of Batteries 127                                                                                                |

|   | 6.1        | Introduction                                                                                                                                    |

|   | 6.2        | Background                                                                                                                                      |

|   | 6.3        | Methodology and Contributions                                                                                                                   |

|   | 6.4        | Related Work                                                                                                                                    |

|   | 6.5        | System Model Definition                                                                                                                         |

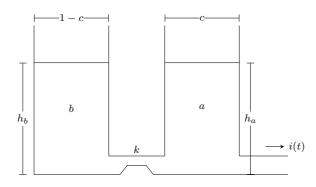

|   |            | 6.5.1 Kinetic Battery Model                                                                                                                     |

|   |            | 6.5.2 SDF Graphs                                                                                                                                |

|   |            | 6.5.3 Platform Application Model                                                                                                                |

|   | 6.6        | Translation of System Model to Hybrid Automata 138                                                                                              |

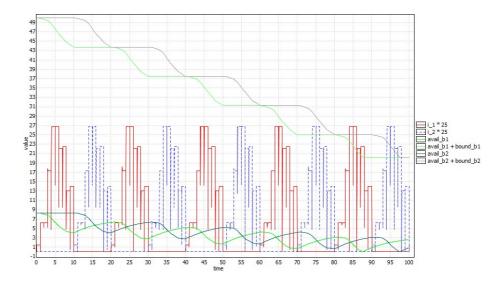

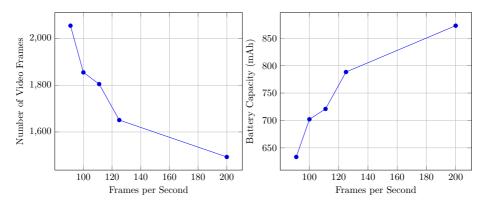

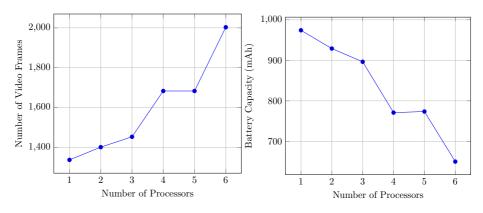

|   | 6.7        | Experimental Evaluation via MPEG-4 Decoder                                                                                                      |

|   |            | 6.7.1 Varying Frames per Second                                                                                                                 |

|   |            | 6.7.2 Varying Number of Processors                                                                                                              |

|   |            | 6.7.3 Varying Number of Batteries                                                                                                               |

|   |            | 6.7.4 Comparison with PTA-KiBaM $\ldots \ldots \ldots \ldots \ldots 143$                                                                        |

|   | 6.8        | Model Checking via MPEG-4 Decoder                                                                                                               |

|   | 6.9        | Conclusions                                                                                                                                     |

| п | ΙN         | Modelling and Validation 149                                                                                                                    |

| 7 |            |                                                                                                                                                 |

| ' | 7.1        | del-Driven Engineering for Dataflow Applications       151         Introduction       152                                                       |

|   | 7.1<br>7.2 | Related Work         152                                                                                                                        |

|   | 1.4        | 7.2.1         HW-SW Co-Design         155                                                                                                       |

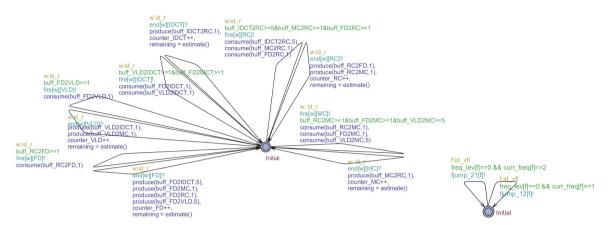

|   |            | 7.2.1         If W-SW Co-Design         155           7.2.2         Model-Driven Engineering         156                                        |

|   | 7.3        | The Model-Driven Framework                                                                                                                      |

|   | 1.5        |                                                                                                                                                 |

|   |            | 7.3.1 Model-Driven Engineering                                                                                                                  |

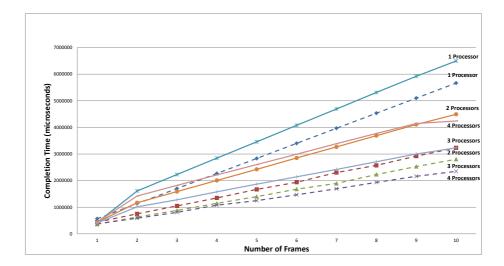

|   |                | 7.3.2   | Overview of the Model-Driven Framework | 158 |

|---|----------------|---------|----------------------------------------|-----|

|   |                | 7.3.3   | Tooling Choices                        | 160 |

|   | 7.4            | Details | s of the Model-Driven Framework        | 160 |

|   |                | 7.4.1   | SDF Graphs                             | 160 |

|   |                | 7.4.2   | Platform Application Models            | 164 |

|   |                | 7.4.3   | Allocation Models                      | 166 |

|   |                | 7.4.4   | Common Metamodel                       | 167 |

|   |                | 7.4.5   | Priced Timed Automata Models           | 168 |

|   | 7.5            | Case S  | Study and Evaluation                   | 169 |

|   |                | 7.5.1   | Case Study                             | 169 |

|   |                | 7.5.2   | Evaluation                             | 169 |

|   |                | 7.5.3   | Timing Performance                     | 172 |

|   | 7.6            | Conclu  | sions                                  | 175 |

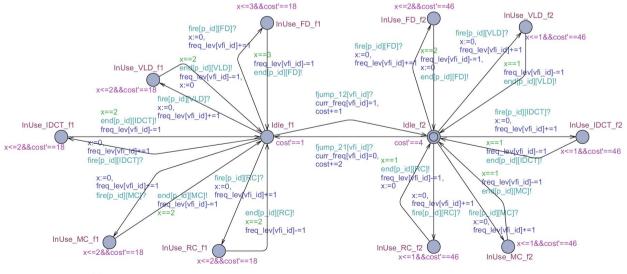

| 8 | $\mathbf{Cas}$ | e Stud  | y: A Face Recognition System           | 177 |

|   | 8.1            | Introd  | uction                                 | 177 |

|   | 8.2            | Descri  | ption of the Case Study                | 178 |

|   |                | 8.2.1   | Application: A Face Recognition System | 179 |

|   |                | 8.2.2   | Platform: FLEXAWARE                    | 180 |

|   | 8.3            | Resear  | ch Questions                           | 180 |

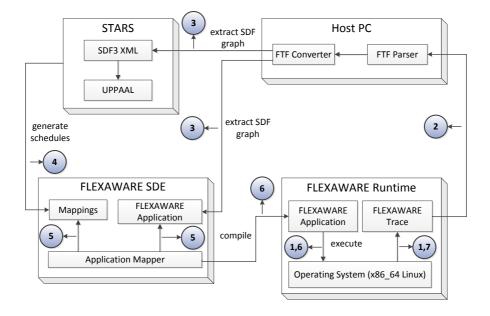

|   | 8.4            | Experi  | mental Setup                           | 181 |

|   |                | 8.4.1   | Overview of the Experimental Setup     | 181 |

|   |                | 8.4.2   | Details of the Experimental Setup      | 181 |

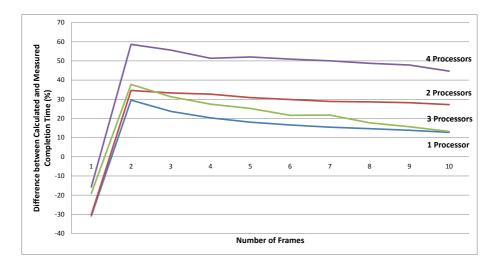

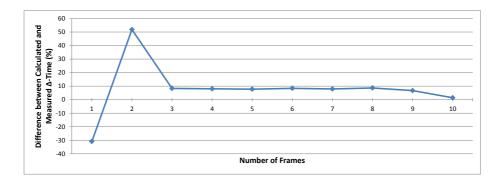

|   | 8.5            | Result  | 8                                      | 185 |

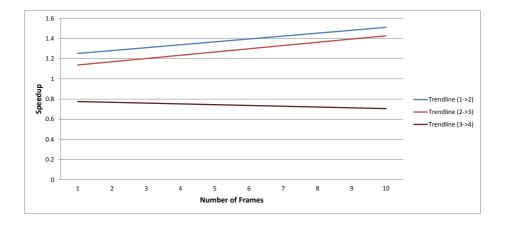

|   |                | 8.5.1   | Performance Evaluation                 | 185 |

|   |                | 8.5.2   | Speedup Evaluation                     | 189 |

|   |                | 8.5.3   | Tool Evaluation                        | 189 |

|   | 8.6            | Conclu  | sions                                  | 190 |

| 9 | Con            | clusio  | ns                                     | 193 |

|   | 9.1            | Contri  | butions                                | 193 |

|   | 9.2            | Recom   | mendations for Future Work             | 195 |

|   |                |         |                                        |     |

# **IV** Appendices

A Detailed Translation of System Model to Hybrid Automata (Chapter 6) 199

197

| B List of papers by the author | 211 |

|--------------------------------|-----|

| List of Symbols                | 213 |

| References                     | 215 |

# Introduction

ONCE, the access to consumer electronics devices such as televisions, telephones, and computers was a luxury shared by few. Nowadays, courtesy to the inventions in the field of electronics in the past halfcentury, consumer electronics devices have become ubiquitous in our daily lives. We are getting more dependent on computers to carry out our daily tasks, such as with-drawing money, scheduling an appointment, reading the news on a tablet, listening to music on a MP3 player, and watching a favourite film on DVD. According to MarketresearchReports.Biz, the Consumer Electronics market is going to witness a value of US \$1.6 trillion by 2018 [MAR13].

Most of consumer electronics devices contain one or more processors to perform the required functionalities of the device. Such devices are termed *embedded systems*. An important subclass of embedded systems is known as *embedded multimedia systems*, which deal with processing multimedia information such as, data, voice, graphics, animations etc., in real-time. Examples of embedded multimedia systems are mobile phones, tablets, virtual reality (VR) enabled gaming consoles, music players, and car navigation systems. As multimedia applications inherently include continuous streams (e.g., streaming videos or audio clips), we can say that many embedded multimedia systems contain *streaming applications* [TKA02].

Embedded multimedia systems are on the rise to make their way in our everyday lives. This trend is also leading to the new challenges of getting a tradeoff between performance, cost (number of processing or memory elements etc.), and energy consumption for these systems. In sections 1.1-1.3, we will investigate the societal, consumer and industrial challenges that led to this research on efficient performance and energy optimisation of streaming applications.

## 1.1 Challenges: A Societal Perspective

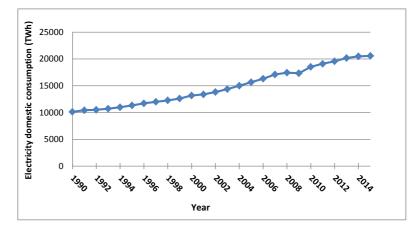

The demand for energy in both commercial and domestic environments is increasing. While our primary sources of energy are running out, the side effects of energy usage have adverse environmental effects. For example, climatologists are associating emission of greenhouse gases such as  $CO_2$  to global warming. Figure 1.1 shows the worldwide energy consumption (TWh) from 1990-2015 [ENE16], where we can see that the energy usage per year has increased dramatically. In fact, in this century so far, the rate of rise in energy consumption is 56%, and this trend is expected to grow at a similar rate. Former U.S. Secretary

Figure 1.1: Worldwide energy consumption (y-axis) over years (x-axis) [ENE16]. The worldwide energy consumption rose at the rate was 56% from 2000-15.

of Energy and Nobel prize winner, Steven Chu placed this issue in the following context [CHU08].

'A dual strategy is needed to solve the energy problem: (1) Maximise energy efficiency and decrease energy use. This part of the solution will remain the lowest hanging fruit for the next few decades; (2) Develop new sources of clean energy.'

Consumer electronics are no different in contributing to high energy consumption. For example, according to Fraunhofer USA, consumer electronics devices in USA consumed 169 TWh of electricity in 2013, which amounts to 12% of residential electricity consumption [FRA14].

To avoid harmful effects of this trend, such as depletion of energy sources, higher emission of  $CO_2$ , and global warming, utilisation of green computing methods and practices must be observed at an individual level. By green computing, we refer to using energy-efficient and environmentally friendly electronic devices, refurbishing and recycling existing old electronic devices, and buying green electricity supplied from renewable energy sources.

## 1.2 Challenges: A Consumer Perspective

#### 1.2.1 Longer System Lifetime

Modern embedded multimedia systems are equipped with ever increasing functionalities. If we consider the evolution of mobile phones, we can see that the a device whose sole purpose was to provide convenient communication, has become a true multimedia system. Apart from video streaming, current mobile phones are equipped with high quality cameras, and are able to browse the Internet, provide navigation and gaming interfaces etc. Cisco predicts that by 2020, 75% of the world's mobile data traffic will consist of multimedia content,

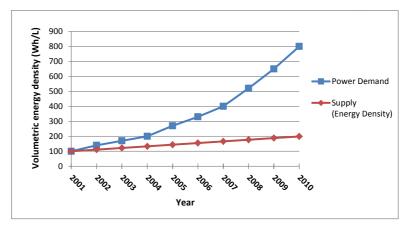

Figure 1.2: Battery energy density (y-axis) over years (x-axis) [ECO05], showing that the mobile device power consumption outgrows the amount of energy a battery can store, at a rate of more than three.

up from 55% in 2015 [CIS16]. Multimedia applications are considered as the most energy-hungry applications. Hence, a key challenge in modern embedded systems is the ever increasing energy consumption.

However, the battery energy densities of embedded multimedia systems have not grown at the same rate over the years [Cha07]. Figure 1.2 shows the growth of battery energy density versus power demand, according to a study by the Boston Consulting Group in 2005 [ECO05]. According to this study, the amount of energy that a battery can store (its *energy density*) is growing by 8% a year. Mobile-device power consumption, meanwhile, is growing at more than three times this rate. As a consequence, everyone owning a mobile phone is aware of the issue to monitor the battery charge and recharge it frequently. Not only mobile phones, every battery-powered system faces the same challenge. For example, Tesla's Model S electric car with a 60 kWh battery delivers 206 miles (334 km) [EPA13]. Therefore, for long trips, the driver has to continuously monitor the battery level, and get it charged at regular charging points.

Thus, *system lifetime* is a major challenge that consumers have to face all the time, i.e., the time one can use the battery before it is empty.

#### 1.2.2 Robust Performance

Modern embedded multimedia systems are expected to perform robustly under strict resource constraints. A mobile phone capable of playing HD videos is a typical example. To process a video frame, the audio and video streams are split and processed separately. The video stream undergoes various picture enhancement steps to improve the video quality. Similarly, several audio improvement algorithms, e.g., echo cancellation, noise reduction etc., are performed on the audio stream. After the audio and video streams are processed separately, they are put in sync again and output on the screen and speakers. Hence, seamless and robust performance is a key requirement for consumers.

Modern day mobile phones such as Google Pixel [GOO16] are able to support VR, which has even higher video quality and resolution than HD videos. Thus, VR requires more intensive processing than HD videos, which in turn requires more processing power, to provide the same seamless performance.

## 1.3 Challenges: An Industry Perspective

Gordon Moore predicted in 1965 that processing power for computers will double every two years [Moo65]. Over the past half-century, engineers more or less managed to maintain that predicted pace. As a result, software applications with increasing concurrency and complexity are continuously implemented on embedded multimedia systems. Mobile phones, discussed earlier, are a typical example of devices with increasing complexity. We see the same trend of increasing complexity also in other embedded multimedia systems such as VRenabled gaming consoles, TVs, and cameras. Frits Vaandrager predicted this trend in 1998 by stating [Vaa98]:

'In recent years there has been a dramatic growth of the number of embedded applications and of the size and complexity of the software used in these applications. For many products in the area of consumer electronics the amount of code is doubling every two years.'

To cope with the ever-increasing complexity and deliver robust performance, modern-day embedded multimedia systems must possess sufficient *computational power*. At the same time, energy consumption must be kept to a minimum as most of these devices are battery powered (e.g., mobile phones, tablets, satellites, portable gaming consoles etc.). Thus, we cannot add processors more than a certain extent due to strict energy limitations. In addition to energy, these devices also have size and cost limitations which further restrict the number of processors.

To minimise energy consumption and prolong system lifetime, modern processors are being equipped with several energy management techniques, e.g., adapting the speed of the system to balance energy and performance implemented as *Dynamic Voltage and Frequency Scaling* [WWDS94], sleep modes implemented as *Dynamic Power Management* [BBDM00], and partitioning processors as *Voltage and Frequency Islands* [HM07]. This thesis deals with all of these energy management methods. Furthermore, the processors in a hardware platform can be classified as: (1) *homogeneous* where all processors are identical, so a (streaming) task can be mapped on any processor.

Moreover, in modern embedded multimedia systems, different components are interconnected, and hence influence each other. Thus, it is not easy to separate different design concerns such as computation, communication, power consumption, memory storage etc., and then try to integrate them together in a naive way. Other than rapidly evolving technology, the fierce market competition puts extra pressure on system designers to shorten time-to-market and reduce development cost, while they are dealing with design complexities they have never seen before.

One solution to bridge this gap is by providing more design automation, e.g., by utilising computer-aided design (CAD) tools to assist with designing, synthesis, simulation, analysis, and testing process. By shifting the design tasks to computers, the minds of the system designers can be liberated to focus more on understanding the increasing complexity and how to handle it.

#### 1.4 Problem Statement

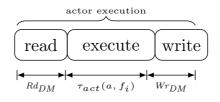

Real-time embedded multimedia applications are often composed of several individual tasks. However, embedded multimedia systems have a limited number of processors to run these applications. To meet severe performance constraints such as functioning robustly while consuming as low as possible energy, efficient mapping of tasks to processors is necessary. Mapping an application onto a multiprocessor system involves three main operations: (1) assigning tasks to processors, (2) ordering tasks on each processor, and (3) specifying the time at which each task executes. These operations are collectively referred to as *scheduling* the application on the multiprocessor system.

In this thesis, we are interested in generating *time-* and *energy-optimal* schedules of streaming applications. From generated schedules, we can determine a trade-off between performance, energy consumption, and number of processors. This facilitates system designers to build robust systems with longer lifetime, and reduced development and manufacturing costs. The central research question addressed by this thesis is formulated as follows.

'How to manage performance and energy of streaming applications running on a given number of (possibly heterogeneous) processors with respect to their hard real-time requirements.'

## 1.5 Proposed Approach

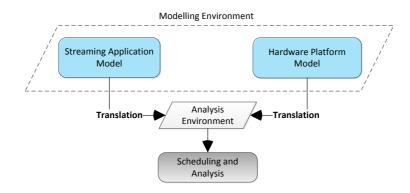

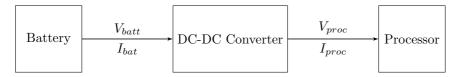

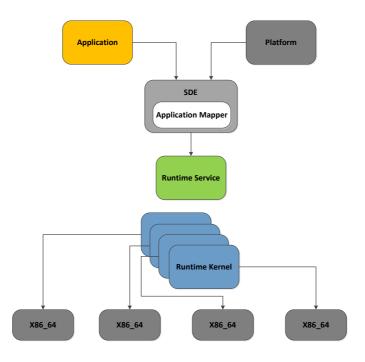

For realising time- and energy-optimal scheduling of streaming applications, we need an approach with the following components, as shown in Figure 1.3.

- Model of computation for streaming applications. Firstly, we need a model of computation for streaming applications that captures all semantics of an application such as inter-task dependencies and their synchronisation properties. Furthermore, the model of computation must be able to express the timing behaviour of an application. This thesis considers synchronous dataflow (SDF) [LM87b] which is a popular formalism for modelling streaming applications.

- *Hardware platform model.* Secondly, a multiprocessor hardware platform model is required onto which the streaming applications' tasks can be mapped. The hardware platform model must also offer heterogeneous mapping capabilities, in case a task cannot be mapped to all processors

Figure 1.3: Overview of the approach proposed in this thesis. A streaming application is modelled, along with a hardware platform, using a modelling environment. Afterwards, these models are translated to an analysis environment which analyses performance and derives optimal schedules.

due to computation limitations. Moreover, the hardware platform model must be decorated with various timing- and energy-related aspects such as Dynamic Voltage and Frequency Scaling, Dynamic Power Management, and Voltage and Frequency Islands. To model hardware platforms, we introduce *platform application models* (PAMs) in this thesis.

- Analysis environment. Thirdly, we need an analysis environment for generating time- and energy-optimal schedules for an application. For this purpose, we model SDF and PAMs in *automata* and utilise *model checking* [CE81, QS82].

- Modelling environment. Lastly, we need an environment that allows efficient modelling of SDF, PAMs, and mappings of SDF tasks to hardware platforms. This is achieved with the help of model-driven engineering [VSB<sup>+</sup>13].

Figure 1.3 shows the flow of our approach and how the aforementioned components are related to each other. First, a streaming application captured by an SDF model of computation, and a hardware platform represented as a PAM, are modelled using model-driven engineering. Secondly, these models are translated to the model-checking domain, which is used to generate the optimal schedules and analyse the performance. In the following sections, we discuss the components in Figure 1.3 in more detail.

#### 1.5.1 Synchronous Dataflow

In an SDF graph, actors communicate with each other by sending ordered streams of data-elements (termed *tokens*) over channels. When an actor fires, it consumes tokens from its input channels, performs computations on these

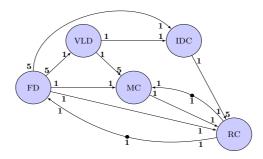

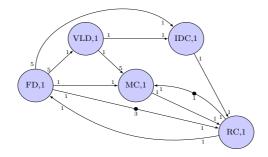

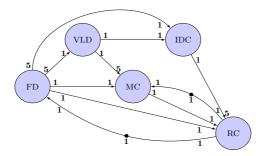

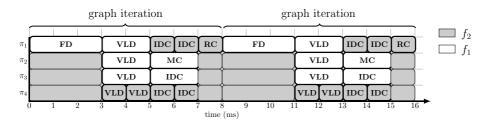

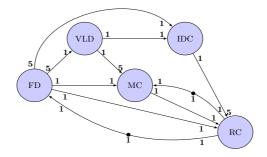

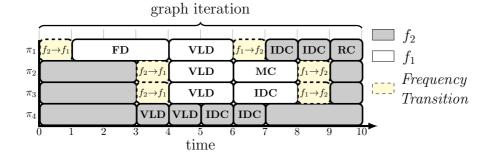

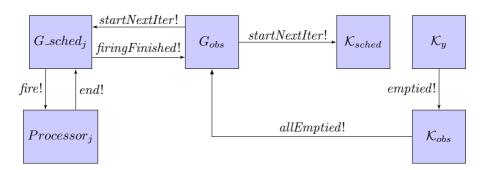

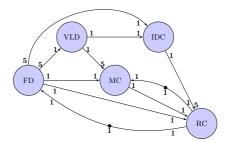

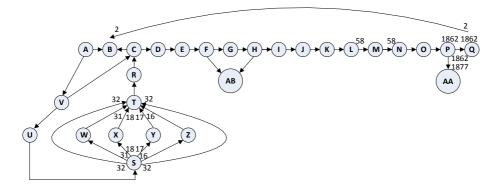

Figure 1.4: SDF graph of an MPEG-4 decoder. Each actor performs part of the MPEG-4 decoding such as, frame detection (FD), variable-length decoding (VLD), inverse discrete cosine transformation (IDC), motion compensation (MC), and reconstruction (RC).

tokens, and produces results as tokens on output channels. In an SDF graph, actors consume and produce a fixed amount of tokens when they fire. This type of model of computation makes it possible to analyse various features such as, a throughput [dKBS12, SBGC07, GGS<sup>+</sup>06], latency [SB09, GSB<sup>+</sup>07], and minimum buffer requirements [GBS05, HRG08, WBS07].

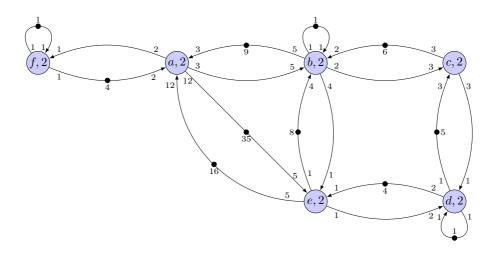

**Example 1.1.** MPEG-4 is a popular data compression method of audio and visual (AV) digital data. The SDF graph of an MPEG-4 decoder is shown in Figure 1.4 [TKW12]. Each of the five actors performs part of the MPEG-4 decoding. The MPEG-4 decoding starts in the actor FD (frame detector) which detects the type of the incoming frame. Different frame types require different number of *macroblocks*, which are processing units in image and video compression formats. The SDF graph in Figure 1.4 contains the number of macroblocks equal to five (shown by the number on the tail of the outgoing channels of FD to VLD and IDC). The actor VLD (variable-length decoder) decodes the variable number of bits, IDC (inverse discrete cosine transformation) applies the data decoding, and MC (motion compensation) predicts a frame in a video by accounting for motion of the camera and/or objects in the video. The complete frame is decoded when the video is reconstructed by the actor RC (reconstruction).

The actors are connected by the channels which correspond to (in principle unbounded) first-in first-out (FIFO) buffers. The actors communicate over the channels by exchanging tokens (unit of information that is communicated between the actors) represented by dots. For example, in Figure 1.4, the number of initial tokens in the channel from RC to FD represent how many frames the SDF graph can process concurrently. As we have one token in the channel from RC to FD in Figure 1.4, the SDF graph can process one frame at a time, and next frame can start only after the completion of the first frame.

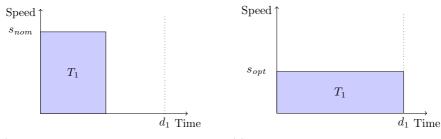

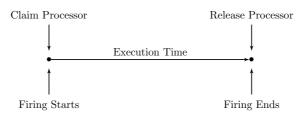

(a) Schedule without DVFS. The speed of the processor  $s_{nom}$  is too high, as a result the task  $T_1$  finishes well ahead of its deadline  $d_1$ , leading to higher energy consumption.

(b) Schedule with DVFS. The speed of the processor is decreased to  $s_{opt}$ , which makes the task  $T_1$  to finish exactly at the deadline  $d_1$ , leading to reduced energy consumption.

Figure 1.5: Schedules without and with DVFS

#### 1.5.2 Hardware Platform Model

The SDF actors are mapped onto a hardware architecture termed *Platform Application Model* (PAM). The PAM consists of multiprocessors, to handle the concurrency of an SDF application. Moreover, the PAM is able to capture timing aspects of SDF actors, and energy related features such as power consumption of the processors. As mentioned earlier, the energy optimisation for modern processors has become one of the most critical, challenging and essential criteria. Therefore, the PAM is equipped with energy management techniques, namely DVFS and DPM. We explain these techniques in the following.

#### **Dynamic Voltage and Frequency Scaling**

The speed (operations per second) of a processor scales cubically to its power consumption [GHK14]. Dynamic Voltage and Frequency Scaling (DVFS) [WWDS94] is a technique that decreases the clock frequency (and the voltage) of a processor, leading to reduced speed and power consumption. In this way, power is consumed for a longer time, but the overall global energy consumption<sup>1</sup> is reduced. Other than processors, DVFS is also used in devices such as flash storage, hard drives, and network cards [LK10, SC01].

**Example 1.2.** Let us consider an application in Figure 1.5a having one task  $T_1$  with a finishing deadline  $d_1$ . The x-axis shows the time, and the y-axis shows the speed. The amount of work for task  $T_1$  is represented by the area of the task (time  $\times$  speed). We assume that this task is running at the nominal speed  $s_{nom}$ . As a result, it finishes well before its deadline.

Figure 1.5b shows the result after deploying DVFS, where we can see that the speed of the same task reduces, and it finishes exactly at the deadline  $d_1$ . As there is a cubic relation between the speed and the power consumption (energy per time unit), the overall energy consumption is reduced also.

<sup>&</sup>lt;sup>1</sup>Energy is the integral of power over time.

| Task  | Amount of Work | Arrival Time | Deadline |

|-------|----------------|--------------|----------|

| $T_1$ | 5              | 0            | 19       |

| $T_2$ | 5              | 0            | 19       |

| T3    | 5              | 14           | 19       |

Table 1.6: Task characteristics of the example application

#### **Dynamic Power Management**

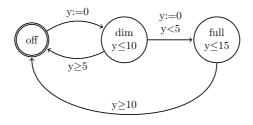

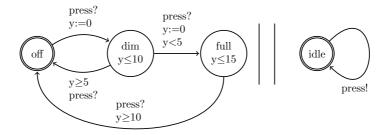

We have seen earlier that DVFS reduces the energy consumption of a device when it is *active*. Another novel energy management technique termed Dynamic Power Management (DPM) [BBDM00] reduces the energy consumption of a device when it is *idle*. DPM supports switching to a low power *sleep mode*, if the device is idle for a longer period of time. For example, consider a processor of a typical mobile phone, having three power states, i.e., ON, INACTIVE, and OFF. If the processor is in the ON state, LCD and backlight of the phone is turned on. If the phone remains idle for some time, the processor enters the INACTIVE state in which the backlight turns off, but the LCD stays turned on. If the phone stays idle for some more time, the LCD is turned off too (the OFF state).

A device may have multiple sleep states. The deeper the sleep model, the higher are the energy savings at the expense of transition latency<sup>2</sup>. Therefore, a device is put to the sleep mode only if the energy savings at the sleep mode outweighs the energy costs of transitioning to the sleep mode and back. The combination of DPM and DVFS guarantees optimal energy reduction.

**Example 1.3.** Let us consider an application having three tasks given in Table 1.6, adapted from [Ger14]. We assume that these tasks are mapped on a single processor, and that a task cannot be interrupted after it has been started, i.e., preemption is not allowed. The processor has a single sleep mode where it consumes no power. The power consumption of the processor is 1 W when it is idle. The power cost for transition to the sleep mode and back is 2 W and 1 W respectively. We ignore the active power consumption of this example, as it does not affect the mapping order of the tasks.

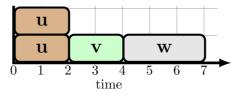

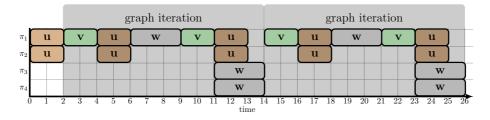

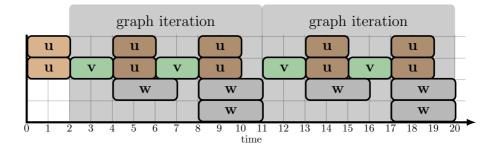

From Table 1.6, we can observe that task  $T_3$  cannot be started before 14 time units. Therefore, tasks  $T_1$  and  $T_2$  must be finished before 14 time units in any order. Please note that whatever the ordering sequence and the starting time of tasks  $T_1$  and  $T_2$ , the total idle time of the processor is always equal to 4 time units.

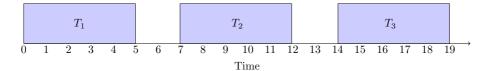

Figure 1.7 shows one possible schedule of this example. Here, the processor is idle between 5 and 7 time units, where the total idle power consumption is 2 W. The total power cost of transition to the sleep mode and back is 3 W, which is larger than the idle power consumption. Therefore, the processor stays idle, and

<sup>&</sup>lt;sup>2</sup>Transition latency is the time required to switch to a sleep model and back.

Figure 1.7: Suboptimal schedule (idle time energy = 4 W)

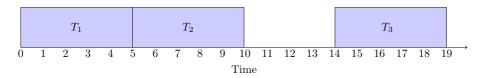

Figure 1.8: Optimal schedule (idle time energy = 3 W)

does not go to the sleep mode. The same happens when the processor is idle again between 12 and 14 time units. Hence, the total idle power consumption of this schedule is 4 W.

In an optimal schedule of this example, the processor stays idle for 4 time units continuously. In this way, the total power cost of the transition to the sleep mode outweighs the idle power consumption. Therefore, the processor moves to the sleep mode, which reduces the total idle power consumption to 3 W. Figure 1.8 shows one possible optimal schedule of this example, where the processor is idle for only once between 10 and 14 time units.

#### Voltage and Frequency Islands

For multiprocessors, DVFS comes in two favours, viz., local and global DVFS [MSH<sup>+</sup>11]. While local DVFS changes the speed per processor, global DVFS makes this change for all processors. Local DVFS is the more energy-efficient of the two. However, local DVFS is expensive and complex to implement because it requires more than one clock domain. In contrast, global DVFS requires a simpler hardware design, but may lead to less reduction in power consumption [MSH<sup>+</sup>11].

To balance the energy efficiency and design complexity, the concept of voltage and frequency islands (VFIs) [HM07] is introduced. A VFI consists of a group of processors clustered together, with each VFI running at a common speed. The speed of the processors in the same VFI may differ from the processors in other VFIs.

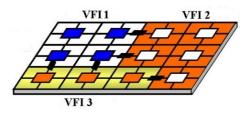

**Example 1.4.** Figure 1.9 shows an example hardware platform model with 12 processors (adapted from [OMCM07]). The processors are partitioned into three VFIs shown by white, red, and green background colour.  $\Box$

#### Scheduling Techniques

Now, that the methods for energy management in multiprocessors are presented, we will explain the different scheduling techniques in the following. Recall

Figure 1.9: Hardware platform model having 12 processors partitioned into three VFIs shown by white, red, and green background colour.

that the scheduling problem consists of (1) assigning tasks to processors, (2) specifying the order in which the tasks fire on each processor, and (3) specifying the time at which the tasks fire. For generating energy-optimal schedules, the scheduling method needs to keep into account two additional parameters, i.e., (1) the optimal idle and running time of the processors (controlled through DPM), and (2) the optimal frequency to execute a certain task (throttled using DVFS).

Lee and Ha published a scheduling taxonomy based on performing tasks at either compile-time or run-time [LH89], as shown in Table 1.10. Each scheduling strategy is explained in the following.

*Fully dynamic.* The first strategy is *fully dynamic*, where all of the scheduling steps are performed at run-time. When all input operands for a task are available, the task is assigned to an idle processor, its order of firing is determined, and executed. The most common fully dynamic scheduling strategies are earliest deadline first (EDF), where the task having the earliest deadline is given priority, and rate-monotonic scheduling (RMS) where the task with the lowest amount of work is given priority.

| Scheduling<br>Strategy | Assignment | Ordering | Timing  |

|------------------------|------------|----------|---------|

| Fully dynamic          | Run        | Run      | Run     |

| Static-assignment      | Compile    | Run      | Run     |

| Static-order           | Compile    | Compile  | Run     |

| Fully static           | Compile    | Compile  | Compile |

*Static-assignment.* In *static-assignment* strategy, instead of assigning a task to a processor at run-time, this step is done at compile-time. Then, using a local run-time scheduler, tasks are assigned to a processor and executed.

Table 1.10: Multiprocessor scheduling strategies

*Static-order*. In *static-order* strategy, the compiler assigns the processor to a task, as well as the order of firing. Afterwards, a local run-time scheduler executes the tasks when their input data is available.

*Fully static.* The last strategy is *fully static*; here the compiler determines the assignment, ordering, and the exact execution time of tasks. There exist different methods for devising fully static scheduling, e.g., round-robin and Time Division Multiplexing (TDM).

Fully static strategy is extensively used in scheduling of streaming applications because of its low implementation overhead [KCMH10]. Because of the same reason, this thesis also considers the fully static scheduling strategy.

#### 1.5.3 Model Checking

For the analysis of timing and energy behaviour of a streaming application mapped on a hardware platform, we also need a suitable analysis environment. Nowadays, three performance analysis approaches are used for embedded applications, namely simulation, mathematical optimisation, and model checking. We explain each of the approaches in the following.

*Classical Simulation.* Simulation is the process of designing a model of a real system and conducting experiments with this model for the purpose either of understanding the behaviour of the system or of evaluating various strategies for the operation of the system [Sha75]. Simulation involves the following phases.

- 1. The first step is to generate an artificial history of the system.

- 2. The second step involves observation of the artificial history to derive inferences concerning the functional characteristics of the real system.

A specific simulation termed *Monte Carlo* allows probabilistic analysis of a system. This is done by repeated random sampling of the input variables based on their distributions to obtain the statistics of the output variables [Moo97, Fis96]. Monte Carlo method is guaranteed to terminate, but it is not guaranteed to give the correct result. Simulation explores only a *limited* set of possible execution of the system.

Mathematical Optimisation. Optimisation is an approach to find an optimal, or the absolutely most efficient, way to achieve an objective while simultaneously satisfying all constraints associated with achieving this objective [OPT, Sny05]. Typically, the objective is maximisation or minimisation of an analytical mathematical expression with a large amount of variables. A typical model in mathematical optimisation consists of the following four key ingredients [Kal04].

- data representing *constants* in a system such as production capacity of a manufacturing plant;

- variables representing *parameters* in a system such as production rate of a manufacturing plant;

| Approach                   | Optimality | Schedule<br>Generation | Ease of<br>Modelling |

|----------------------------|------------|------------------------|----------------------|

| Classical Simulation       | _          | _                      | +                    |

| Optimisation               | +          | +                      | _                    |

| Model Checking             | +          | +                      | +                    |

| Statistical Model Checking | +/-        | _                      | +                    |

Table 1.11: Comparison of different performance analysis approaches

- constraints representing restrictions of a system such as downtime of a manufacturing plant caused by breakdowns, material shortages etc., and

- the objective function representing the goal such as maximisation of utilisation rate of a manufacturing plant.

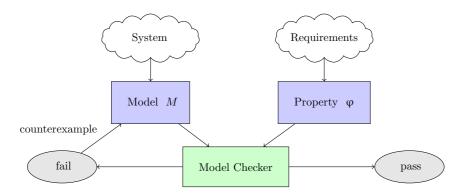

*Model Checking.* Model checking is a model-based verification technique that analyses the system behaviour in a mathematically precise and unambiguous way [CE81, QS82]. Using model checking, we can explore *all* possible states in a brute-force way. In this way, it can be shown that a system truly (dis)satisfies a property.

As mentioned earlier, we are interested in deriving optimal schedules. For this purpose, the analysis environment must have the following features.

- It must guarantee that the achieved results are optimal.

- It must be able to generate execution traces (schedules).

- It must be model-based, in order to fit in our model-driven engineering based framework.

Table 1.11 shows the comparison of these analysis approaches. Classical simulative methods are mostly model-based and generate traces. However, they cannot make sure that all interesting corner cases are covered even if we run simulations exhaustively, and thus optimality cannot be guaranteed. On the other hand, mathematical optimisation ensures optimality. However, mathematical optimisation is difficult to model as it requires quantification of all ingredients such as variables, constraints etc. in a mathematical form. Only model checking provides all of these features, and hence we consider it as an analysis environment in this thesis. In addition to model checking, we also consider statistical model checking. In contrast to classical simulation, statistical model checking combines simulations and statistical methods (such as sequential hypothesis testing) in order to decide with some degree of confidence whether the system satisfies the property or not.

In particular, we use model checking for performing *nondeterministic* scheduling, where the choices of the assignment, ordering, and the exact firing time of actors is determined nondeterministically by a scheduler at design-time in such a way that the generated schedules are time- or energy-optimal. In contrast, classical fully static strategies such as round-robin and TDM cannot guarantee optimality. For example, if we have an SDF graph where an actor rarely fires, we still have to assign a time slice to that actor in the round-robin scheduling strategy, which will affect the overall finishing time.

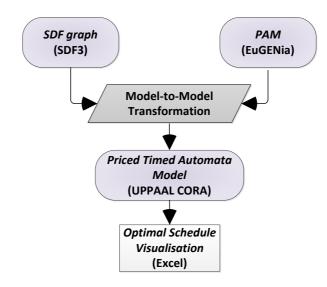

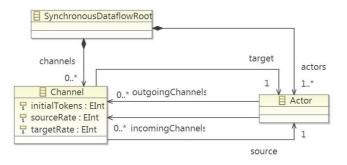

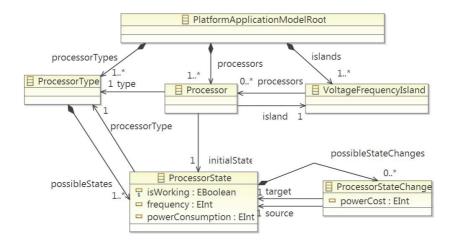

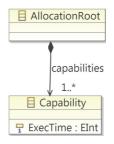

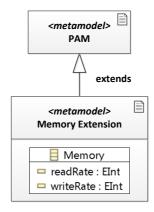

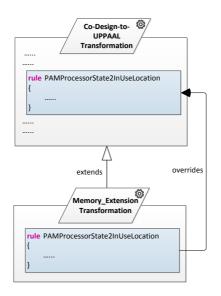

#### 1.5.4 Model-Driven Engineering

To achieve optimal timing and energy management of a streaming application, the last component we need is an efficient modelling environment. This thesis considers the *Model-Driven Engineering* (MDE) [VSB<sup>+</sup>13] paradigm that treats models as first-class citizens. In MDE, the important concepts of the target domain are formally captured in a so-called *metamodel*. Separate metamodels for the domains of interest help to keep the design modular. All models are instances of a metamodel, or possibly an integrated set of metamodels. Moreover, a model can be transformed to another via *model transformations*, defined at the metamodel level. MDE also provides modularity, convenient extension mechanisms, and interoperability between different tools.

## 1.6 Thesis Structure

#### 1.6.1 Thesis Overview

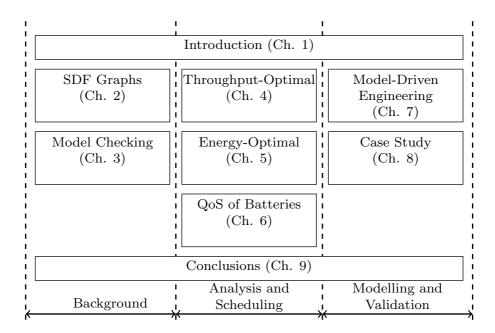

Figure 1.12 shows the structure of the thesis. The whole thesis is divided into the following three main parts.

- The first part *Background* contains Chapter 2 and 3. This part presents background material required to understand later chapters. Therefore, the readers are urged to study this part first.

- The second part *Analysis and Scheduling* contains Chapters 4 6. These chapters explain different scheduling and analysis techniques for SDF graphs mapped on multiprocessor hardware platforms. The chapters in this part can be read independently after reading the first part.

- The third part *Modelling and Validation* contains two chapters. Chapter 7 introduces model-driven engineering for dataflow applications. This chapter can be studied independently. Chapter 8 applies the methodology in Chapter 4 in the case study of face recognition system. Thus, the readers are advised to read Chapter 4 first before reading this chapter.

#### 1.6.2 Contributions

This thesis makes several contributions to efficient modelling and optimal scheduling of streaming applications on a multiprocessor platform. Given an SDF graph, this thesis presents the following contributions.

Figure 1.12: Overview of the structure of the thesis

- *Throughput optimisation*. A technique of deriving a schedule that fits on the given number of processors and maximises throughput is given (Chapter 4). This technique can also handle heterogeneous processor models, in which only specific processors can run a particular task due to their computational limitations. Moreover, using this technique, we can determine a trade-off between number of processors and throughput.

- Energy optimisation. An energy optimisation method that applies the combination of Dynamic Power Management (DPM) and Dynamic Voltage and Frequency Scaling (DVFS), and considers processors partitioned into Voltage and Frequency Islands (VFIs) is presented (Chapter 5). We further demonstrate that VFIs allow combining DPM and DVFS policy with any granularity.

- *Performance assessment*. An approach of assessing performance, and model checking of multiple batteries for different design alternatives is presented (Chapter 6). It is further shown that our approach allows better scalability than a state-of-the-art approach [JHBK09].

- Efficient modelling using MDE. A state-of-the-art model-driven engineering (MDE) framework is proposed (Chapter 7). In the framework, we present a reusable set of three coherent, extensible metamodels. Furthermore, we define and apply model transformations from the dataflow domain to the model-checking domain. Lastly, we demonstrate that our fully automated framework provides modularity, extensibility and interoperability between tools.

• *Practical Validation*. The technique of generating throughput-optimal schedules presented in Chapter 4 is validated (Chapter 8). For this purpose, an industrial case study termed "Face Recognition Application" provided by Recore Systems, Netherlands is considered.

## 1.6.3 Contents and Origins of the Chapters

The remainder of the thesis is organised in the following way. The origins of the chapters are also given where relevant.

- Chapter 2 presents streaming applications and their characteristics. It also formally defines SDF graphs, and various notions associated with them. We also introduce the state-of-the-art tool for SDF analysis termed  ${\rm SDF}^3$ .

- **Chapter 3** introduces the different model-checking formalisms considered in the thesis, and describes them with the help of examples.

- Chapter 4 presents a technique of deriving throughput-optimal schedules of an SDF graph on a given number of processors, using model checking. This chapter is based on the paper "Resource-Constrained Optimal Scheduling of Synchronous Dataflow Graphs via Timed Automata", which was published at ACSD 2014 [AdGH<sup>+</sup>14a].

- Chapter 5 extends the work in Chapter 4 and presents a method of generating energy-optimal schedules of an SDF graph on a given number of processors, using model checking. This chapter is based on the paper "Green Computing: Power Optimisation of VFI-based Real-time Multiprocessor Dataflow Applications", which was published at DSD 2015 [AHSvdP15a].

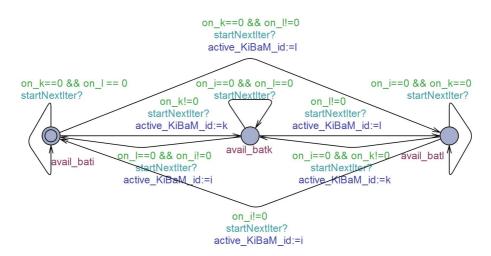

- Chapter 6 considers an intuitive battery model termed kinetic battery models (KiBaMs) [MG93] in the hardware platform model. In this way, the processors are dependent on the battery charge to run. Once the batteries are empty, the processors cannot run any more. Moreover, using statistical model checking, different performance aspects are determined. This chapter is based on the paper "Model Checking and Evaluating QoS of Batteries in MPSoC Dataflow Applications via Hybrid Automata", which was published at ACSD 2016 [AJSvdP16a].

- Chapter 7 proposes a MDE-based approach for SDF graphs. This chapter is based on the paper "A Model-Driven Framework for Hardware-Software Co-design of Dataflow Applications", which was published at CyPhy 2016 [AYRS16a].

- **Chapter 8** performs the scheduling of an industrial case study of face recognition system mapped on a limited number of processors.

- Chapter 9 concludes this thesis and provides future directions.

#### 1.7 Conclusions

This chapter has laid the foundation for the rest of the thesis. In particular, the problem statement of the thesis and the proposed approach is explained. Over the past half century, the revolution in the hardware industry has changed the shape of the modern-day embedded systems. As a result, more and more applications and functionalities are being integrated in these systems. On the one hand, this has improved the standards in our daily life. On the other hand, this trend is causing negative effects on our environment due to increased emission of greenhouse gases. Furthermore, many of the embedded systems are battery-powered. This means that these systems must be recharged more frequently, which is leading to depletion of the world's energy sources. To cope with such situation, green computing has become an important, crucial, and key necessity of today's world.

This thesis contributes in overcoming this challenge by presenting an approach which allows efficient energy management of multiprocessor streaming applications, leading to energy-conscious systems. To realise this objective, the following choices are considered in this thesis.

- Streaming (software) applications modelled as SDF graphs.

- Homogeneous/Heterogeneous multiprocessor hardware platform to execute the streaming (software) tasks.

- Utilisation of MDE for efficient modelling of SDF graphs, hardware platform models, and mapping of SDF actors to processors.

- Model checking for performance analysis and generation of optimal schedules.

# Part I Background

## **Dataflow Preliminaries**

LGORITHMS for streaming applications can be naturally represented by block diagrams or flow charts in which computational blocks are interconnected by links that represent sequences of data values. Furthermore, the utilisation of visual programming in block diagrams or flow charts provides an intuitive specification mechanism for streaming applications. This thesis considers synchronous dataflow (SDF) [LM87b] to represent streaming applications

One of the reasons for the popularity of SDF models is their ability to capture parallelism in a streaming application. The imperative programming languages such as C and FORTRAN are based on *von Neumann* architecture, in which a small processor is attached to a big memory. Data items are present in the memory in their "cells" from where they are fetched one by one. Afterwards, these data items are sent to the central processing unit (CPU) in which the actual computation is performed, and then the results are returned one by one to their original cells. Thus, data in von Neumann architecture is static. This leads to a significant overhead of data-dependency constraints, resulting in challenges in compilation of such specifications onto the parallel hardware architectures. SDF models, on the other hand, impose minimal data-dependency constraints, enabling a compiler to detect parallelism. This also leads to efficient hardware synthesis, where it is important to specify and exploit concurrency.

Another reason for the popularity of SDF models is that they offer several analytical properties. The most important analytical property of SDF models is to effectively exploit parallelism in a streaming application by scheduling computations onto multiple processors at design-time. Given such a schedule computed at design-time, we can extract information from it towards optimising the final implementation.

Due to the success of SDF in industry, several commercial and research tools have been developed around SDF and closely related models. Commercial tools include Signal Processing Worksystem (SPW) from Cadence [PLN92, BL91], COSSAP [RPM92] and Cocentric System Studio [BV00] from Synopsys, ADS from Agilent, LabVIEW from National Instruments [AK98], and System Canvas from Angeles Design Systems [MCR01]. Tools based on the SDF formalism developed at different research laboratories and institutes include DESCARTES [RPM92], DIF [HKB05], GRAPE [LEAP95], the Graph Compiler [VPS90], NPclick [SPRK04], PeaCE [SOIH97], PGMT [Ste97], Ptolemy [BHLM94], StreamIt [TKA02], the Warp Compiler [Pri92], Lustre [HCRP91], Lucid [WL85], and SDF<sup>3</sup> [SGB06]. **Chapter Outline.** SDF graphs are formally defined in Section 2.1. Different semantics associated with SDF graphs are presented in Section 2.2 and Section 2.3 explains how to model storage capacities in SDF graphs. Section 2.4 describes the throughput analysis of SDF graphs. A state-of-the art tool implemented with various SDF graph analysis and techniques termed SDF<sup>3</sup> [SGB06] is explained in Section 2.5. A comparison of SDF and other dataflow models is given in Section 2.6. Section 2.7 explains different case studies modelled as SDF graphs. Finally, Section 2.8 presents a summary of the chapter.

## 2.1 Synchronous Dataflow Models

In typical streaming applications, there is a set of tasks to be executed in a certain order. An important part of these applications is a set of periodically executing tasks which consume and produce fixed amounts of data. An SDF graph is a directed, connected graph in which these tasks are represented by *actors*, data communicated is represented by *tokens*, and (FIFO) buffers used to transport tokens between actors are represented by *channels*. Each channel is connected to precisely one producer and precisely one consumer. The execution of an actor is known as an (*actor*) firing and the number of tokens consumed or produced onto a channel as a result of a firing is referred to as *consumption* and *production rates* respectively.

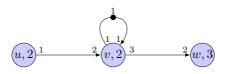

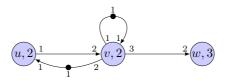

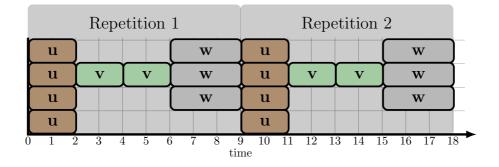

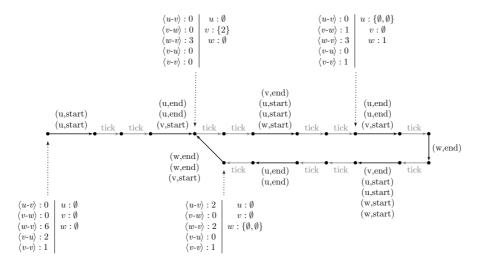

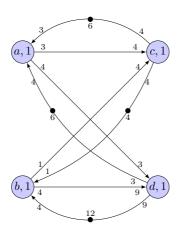

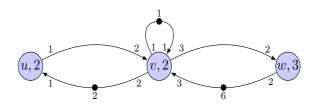

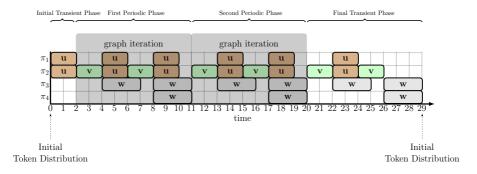

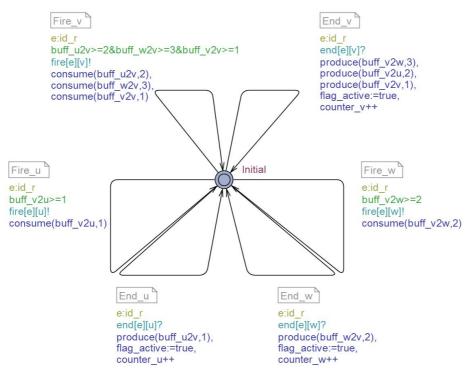

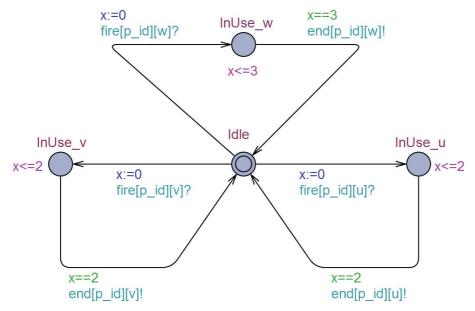

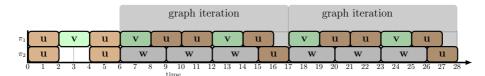

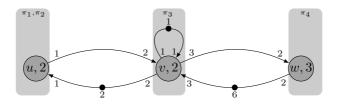

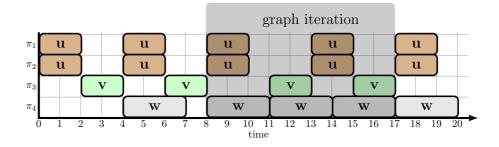

**Example 2.1.** Figure 2.1 shows an SDF graph with three actors u, v, w. Arrows between the actors depict the channels which hold tokens (dots). The numbers near the source and destination of each channel are the rates.

Figure 2.1: An example SDF graph (adapted from [dKBS12]).

Formally, the definition of an SDF graph is as follows.

**Definition 2.2.** An SDF graph is a tuple  $(A, D, Tok_0)$  where:

- A is a finite set of actors,

- D is a finite set of dependency channels  $D \subseteq A^2 \times \mathbb{N}^2$ , and

- $\mathsf{Tok}_0: D \to \mathbb{N}$  denotes initial tokens in each channel.

A dependency channel d = (a, b, p, q) denotes a data dependency of actor b on actor a. The firing of actor a results in the production of p tokens on channel d. If the number of tokens on channel d is greater than q, actor b can execute, and as a result, it consumes q tokens from channel d.

Figure 2.2: SDF graph in Figure 2.1 extended with time

**Definition 2.3.** The sets of input In(a) and output channels Out(a) of an actor  $a \in A$  are defined as

$$In(a) = \{(a_0, a, p, q) \in D | a_0 \in A, p, q \in \mathbb{N}\}$$

$$Out(a) = \{(a, b, p, q) \in D | b \in A, p, q \in \mathbb{N}\}$$

Informally, if the number of tokens on every input channel  $d_i$  is greater than  $q_i$ , actor  $a_i$  fires and removes  $q_i$  tokens from every  $(a_{0_i}, a_i, p_i, q_i) \in In(a)$ . For example, actor v in Figure 2.1 consumes two tokens from channel u-v and one token from channel v-v, and produces three tokens on channel v-w and one token on channel v-v after finishing firing.

**Definition 2.4.** The consumption rate CR(a, b, p, q) and production rate PR(a, b, p, q) of a channel  $(a, b, p, q) \in D$  are defined as

$$CR(a, b, p, q) = q$$

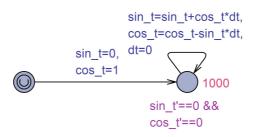

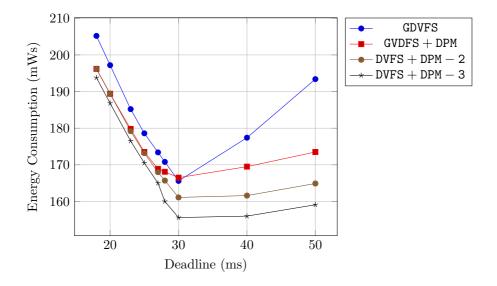

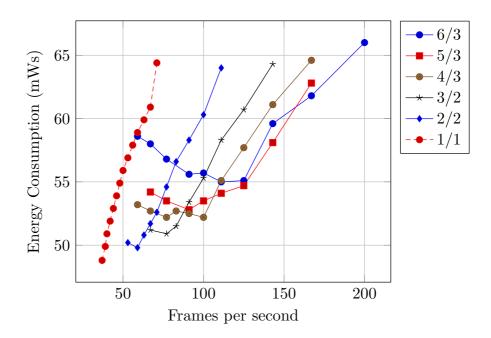

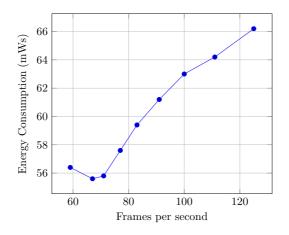

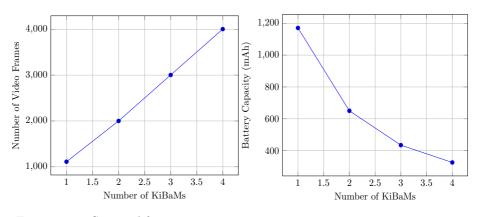

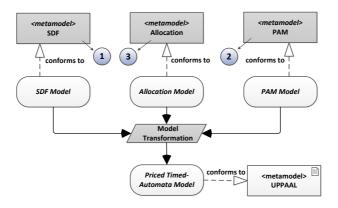

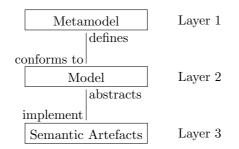

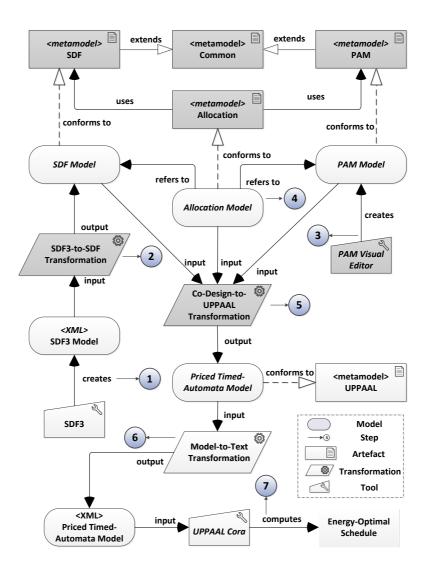

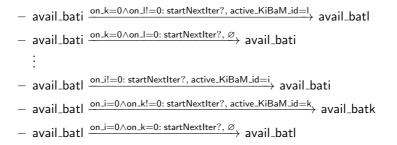

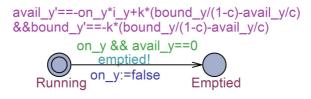

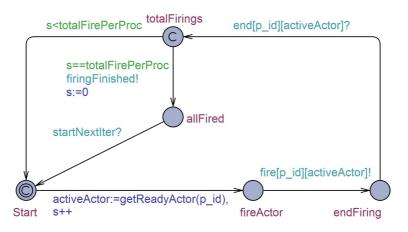

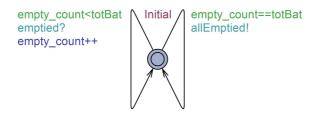

$PR(a, b, p, q) = p$